在Verilog代码编写过程中,准确区分可综合与仿真语句是至关重要的。这不仅能够确保代码在硬件实现中的正确性和效率,还能在仿真阶段有效地验证设计功能。

1、理解可综合语句

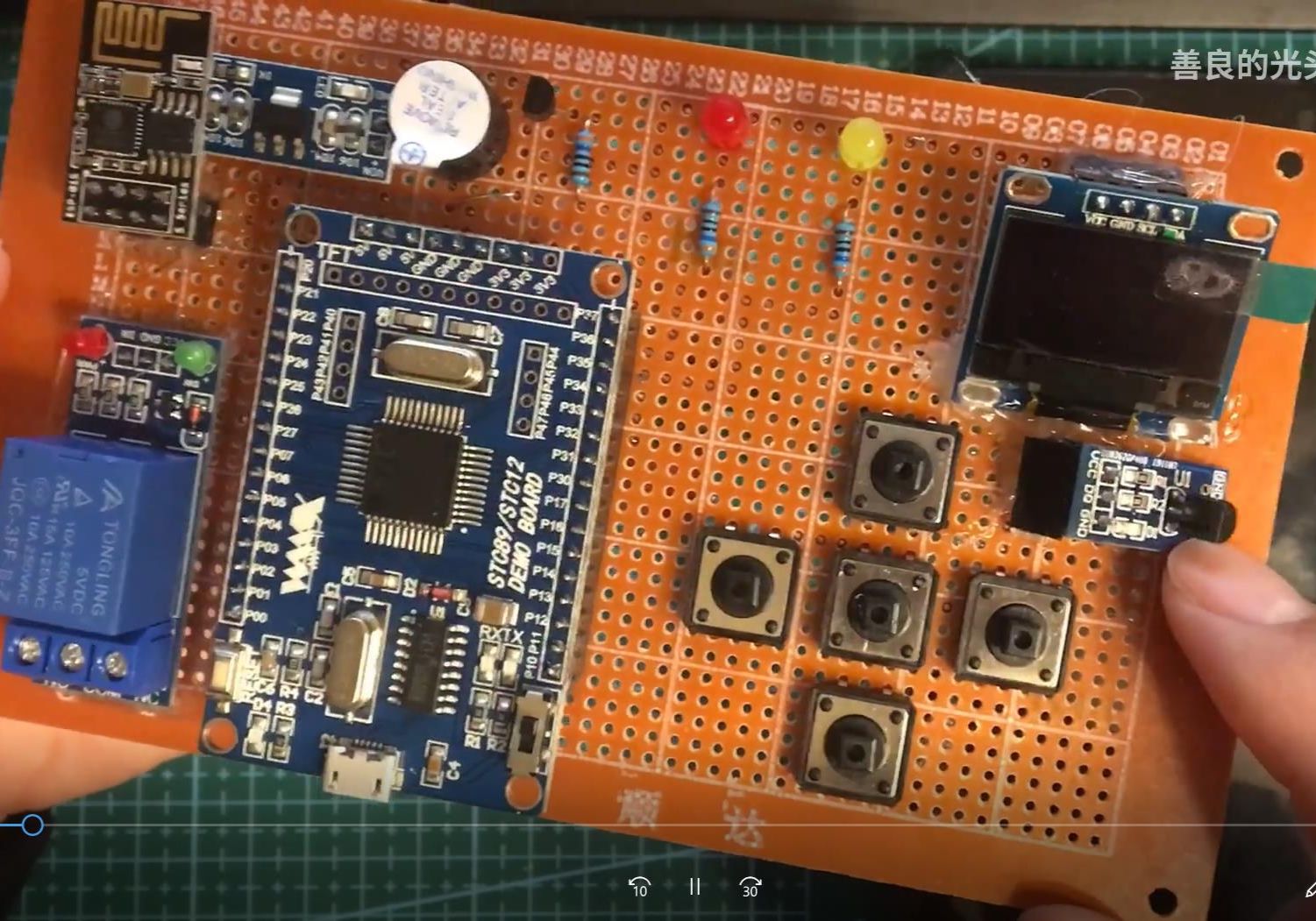

可综合语句是指那些能够被综合工具(如FPGA综合器或ASIC综合器)转化为实际硬件电路的Verilog代码。这些语句通常描述的是硬件的直接行为,如寄存器的读写、逻辑门的操作等。以下是一些常见的可综合语句:

①寄存器(reg)定义与赋值:

使用reg类型定义的变量,通常用于描述寄存器或存储单元。

在always或initial块中使用非阻塞赋值(<=)或阻塞赋值(=),根据上下文确定。

②线网(wire)连接与逻辑操作:

使用wire类型定义的变量,通常用于描述逻辑门之间的连接。

通过连续赋值语句(assign)或逻辑运算符(如and、or、not等)实现逻辑功能。

③模块实例化与端口连接:

使用module关键字定义模块,并通过实例化其他模块来构建复杂的硬件系统。

端口连接应明确指定方向(输入、输出或双向),并使用正确的数据类型。

2、识别仿真语句

仿真语句是指那些主要用于仿真阶段,但不被综合工具转化为硬件电路的Verilog代码。这些语句通常用于模拟硬件的外围电路、测试激励或验证设计功能。以下是一些常见的仿真语句:

①延迟控制:

使用#符号指定延迟时间,如#10 clk = ~clk。这种语句在仿真中用于产生时钟信号或其他周期性信号,但不被综合为硬件电路。

②不可综合的系统任务与函数:

使用$display、$monitor等系统任务输出仿真信息。

调用不可综合的系统函数,如$time、$random等。

③测试激励与验证:

在initial块中使用force和release语句强制设置变量值,以模拟特定的测试条件。

使用assert语句或expect语句(在某些仿真工具中)验证设计是否满足预期行为。

3、编写代码时的注意事项

明确区分用途:在编写代码时,应明确每个语句的用途是综合还是仿真。这有助于在后续阶段(如综合、布局布线、测试等)中避免混淆和错误。

使用条件编译:在需要同时包含可综合和仿真语句的情况下,可以使用条件编译指令(如```verilog

ifdef SIMULATION // 仿真语句 else

// 可综合语句

`endif

本文凡亿教育原创文章,转载请注明来源!

扫码关注

扫码关注