爬电距离:

两个导电部件之间,或一个导电部件与设备及易接触表面之间沿绝缘材料表面测量的最短空间距离。沿绝缘表面放电的距离即泄漏距离也称爬电距离,简称爬距。

对最小爬电距离做出限制,是为了防止会在绝缘材料表面产生局部恶化传导路径的布线,这样的布线会使得电子在绝缘表面或附近放电。

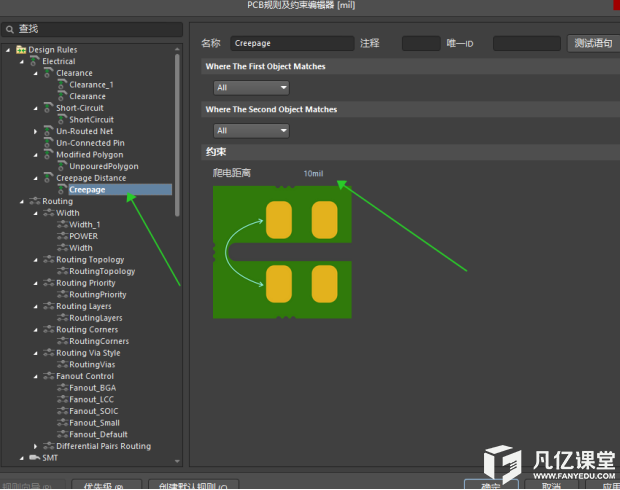

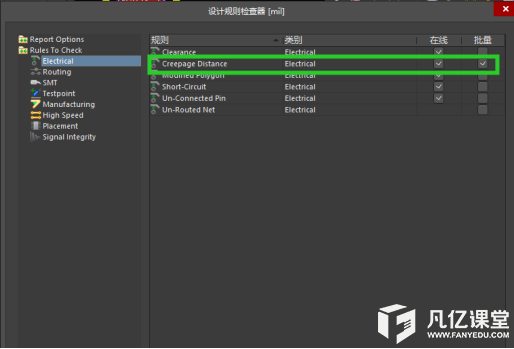

规则设置:

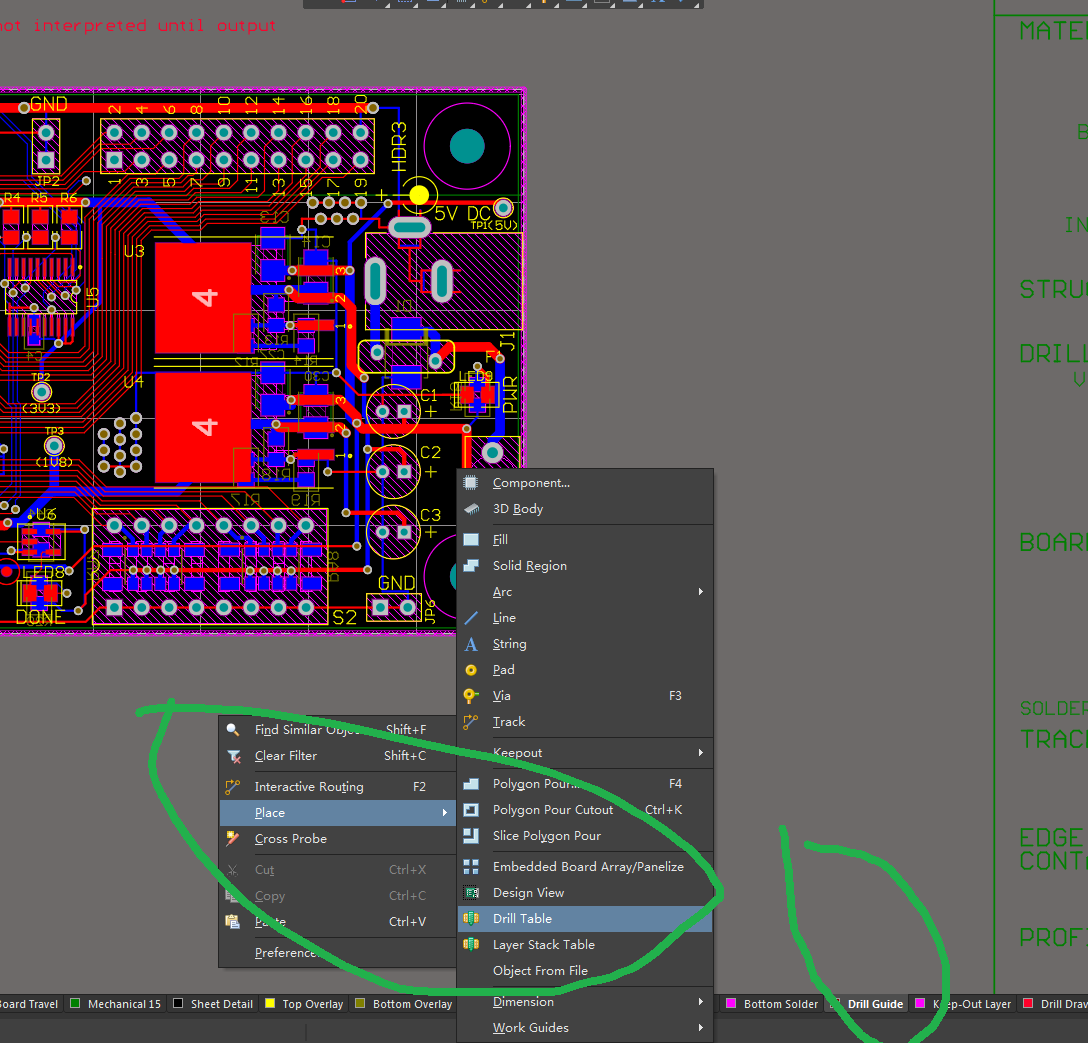

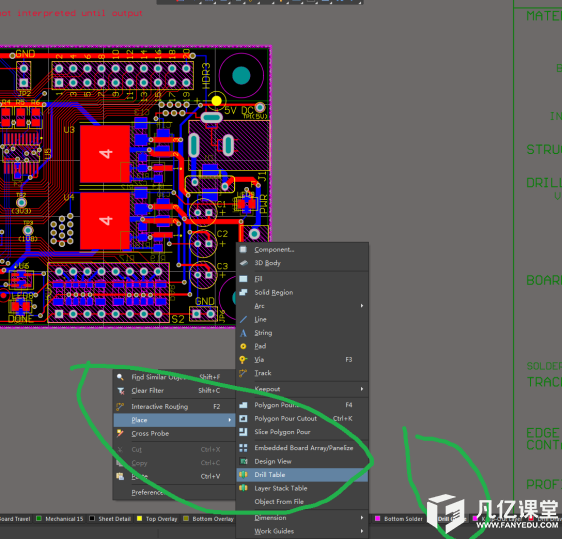

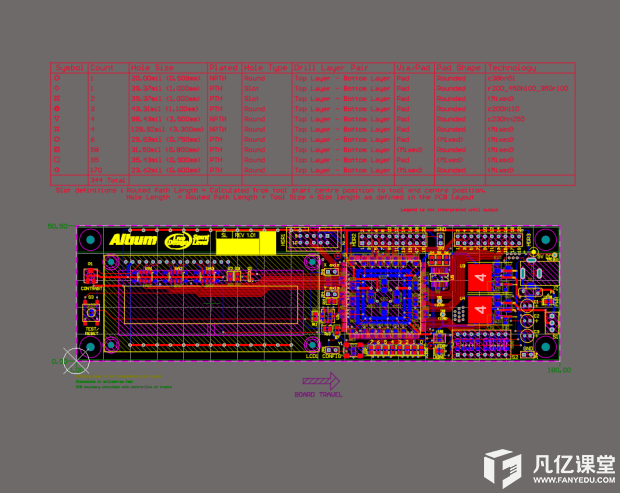

1. 执行菜单栏“设计”-“规则”命令,或者使用快捷键DR打开规则管理器

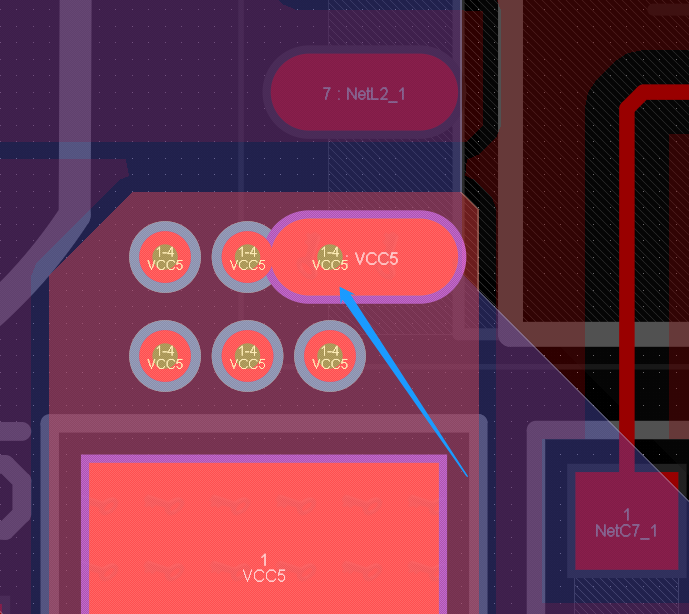

2. 在规则管理器中找到设置爬电距离的规则Creepage distance,对爬电距离进行设置

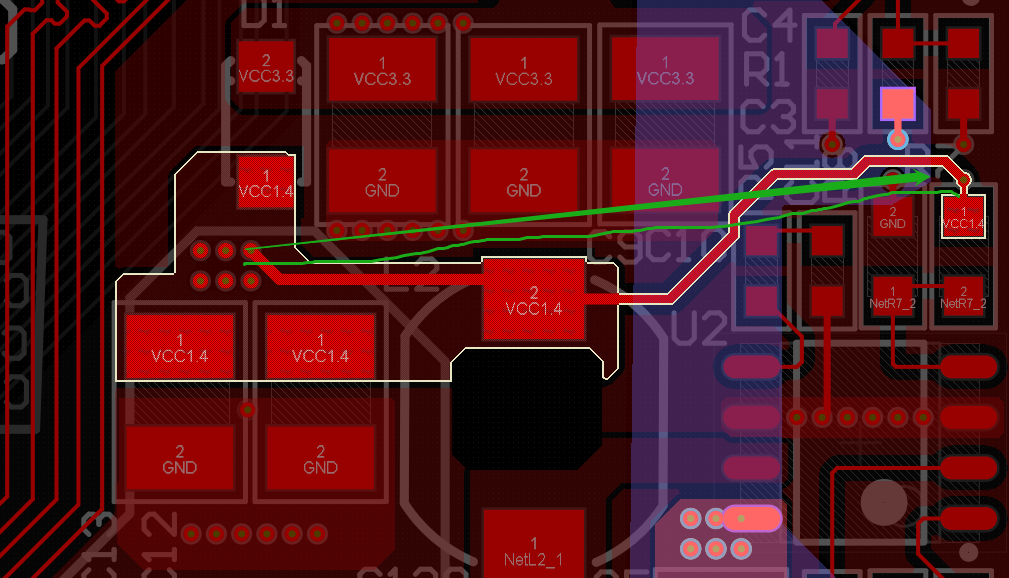

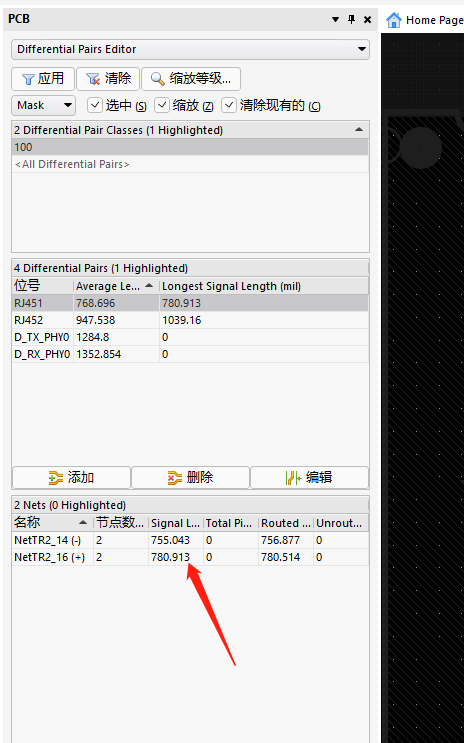

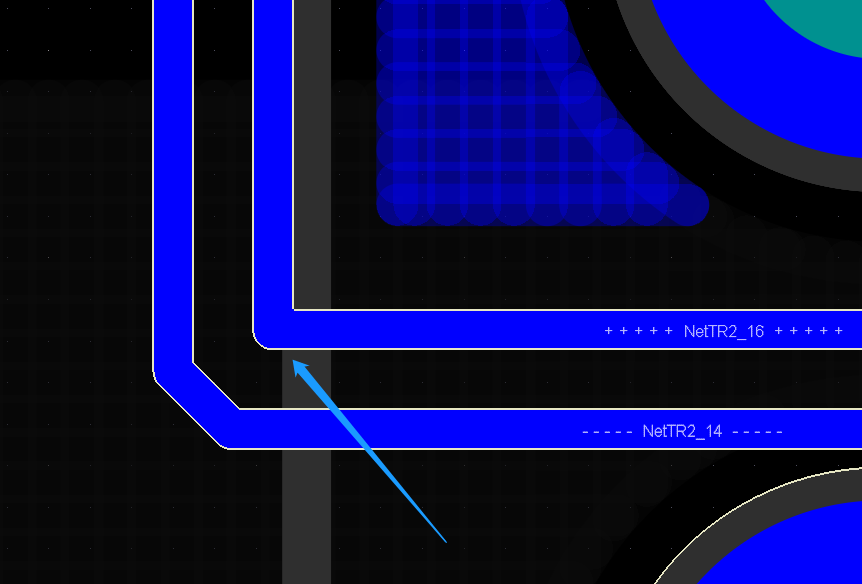

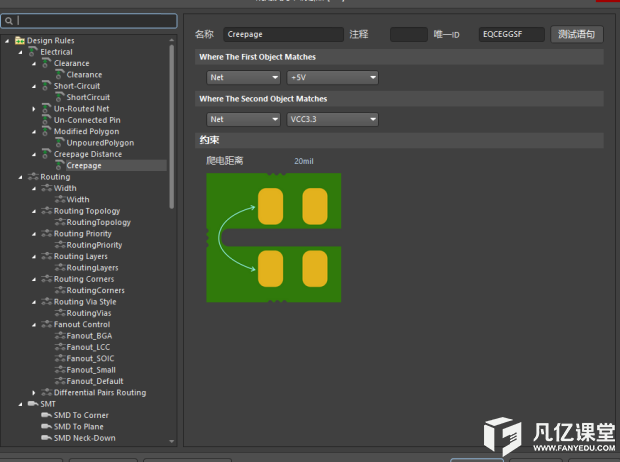

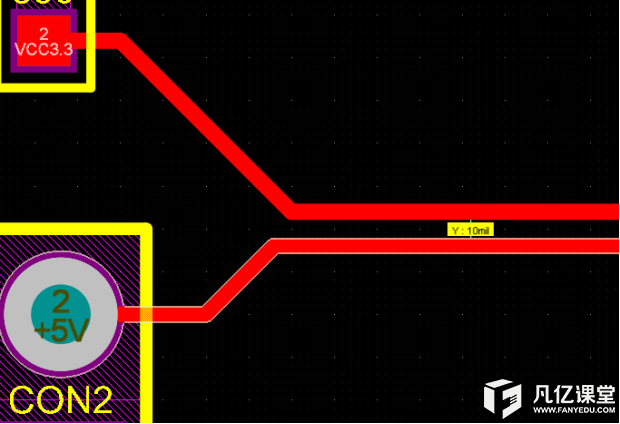

这里用两根网络来举例简单说明一下这个规则:

1.这里对VCC3.3和+5V的爬电距离设置为20mil

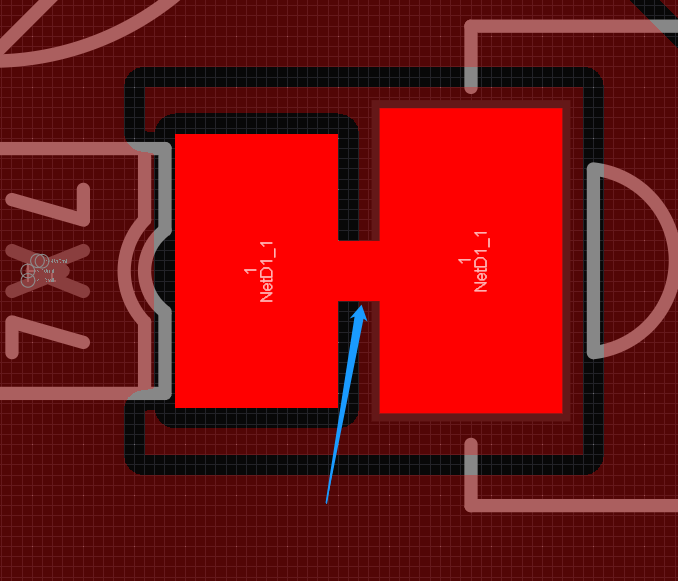

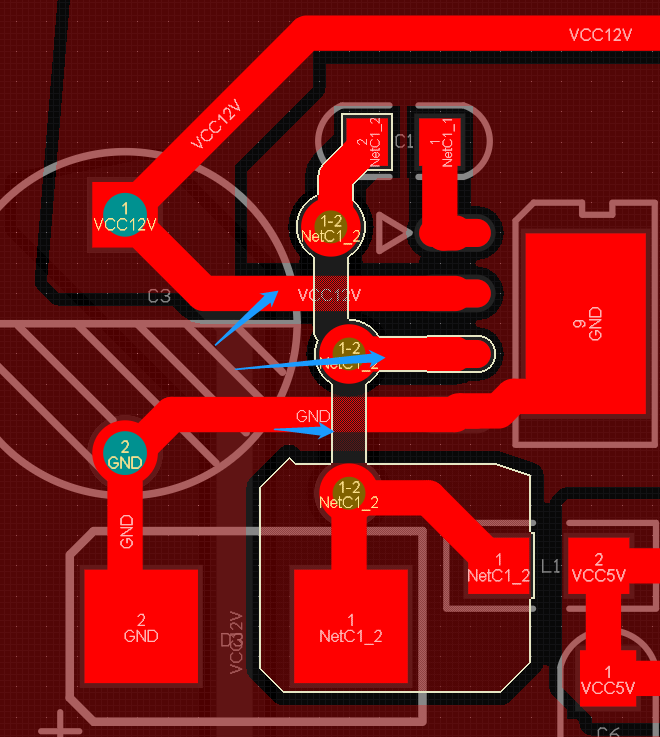

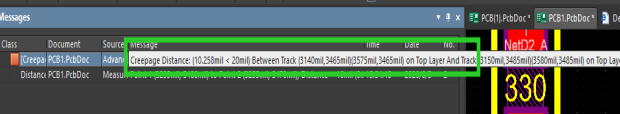

2.通过快捷键TDR进行DRC检查发现,出现如图所示的爬电间距不够的报错

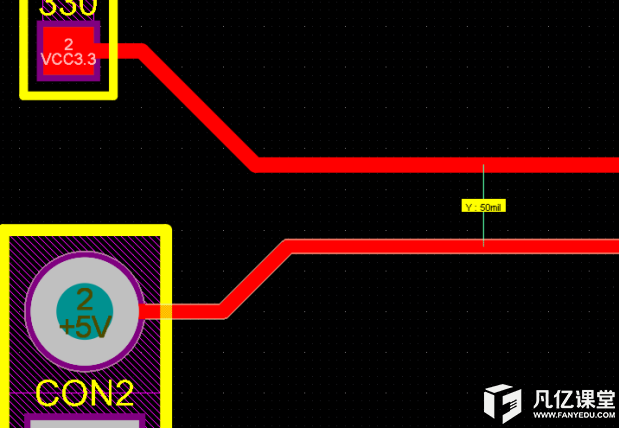

3.我们增大两者之间的间距,然后再次进行DRC检查,发现这个报错消失了 说明我们这个规则设置成功了,我们的间距需要满足我们所设置的爬电距离才不会进行报错

对于pcb设计中的爬电距离经验介绍:

1)PCB设计中弱电距离应大于15mil,强电应大于100mil,如果距离不够可以考虑开槽,开槽大于1mm。对于一个槽(>1mm),唯一的要求是,现有的爬电距离,再加上槽宽度和的两倍槽深度必须等于或大于的爬电距离。凹槽也不能削弱PCB基板的强度而使PCB板达不到硬度测试要求。

2)关于PGND ,CGND,48V,60V电源,这些信号的爬电距离:推荐为2mm,如果因为器件管脚、结构等作2mm有困难,最小可以做到1mm。特别是负片层、一定要做到。

3)隔离器下面的所有层的空间不能放置走线,过孔,焊盘,以保持最大的爬电距离。

4)en61347-1中没有pcb板爬电距离的规定。

ul60950安全标准:电源高压侧初级走线间隔4mm,初级与次级走线间隔8mm,低压边及控制线走线间隔0.3mm。

扫码关注

扫码关注