导言

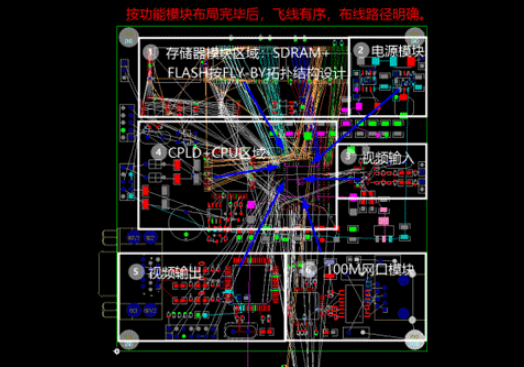

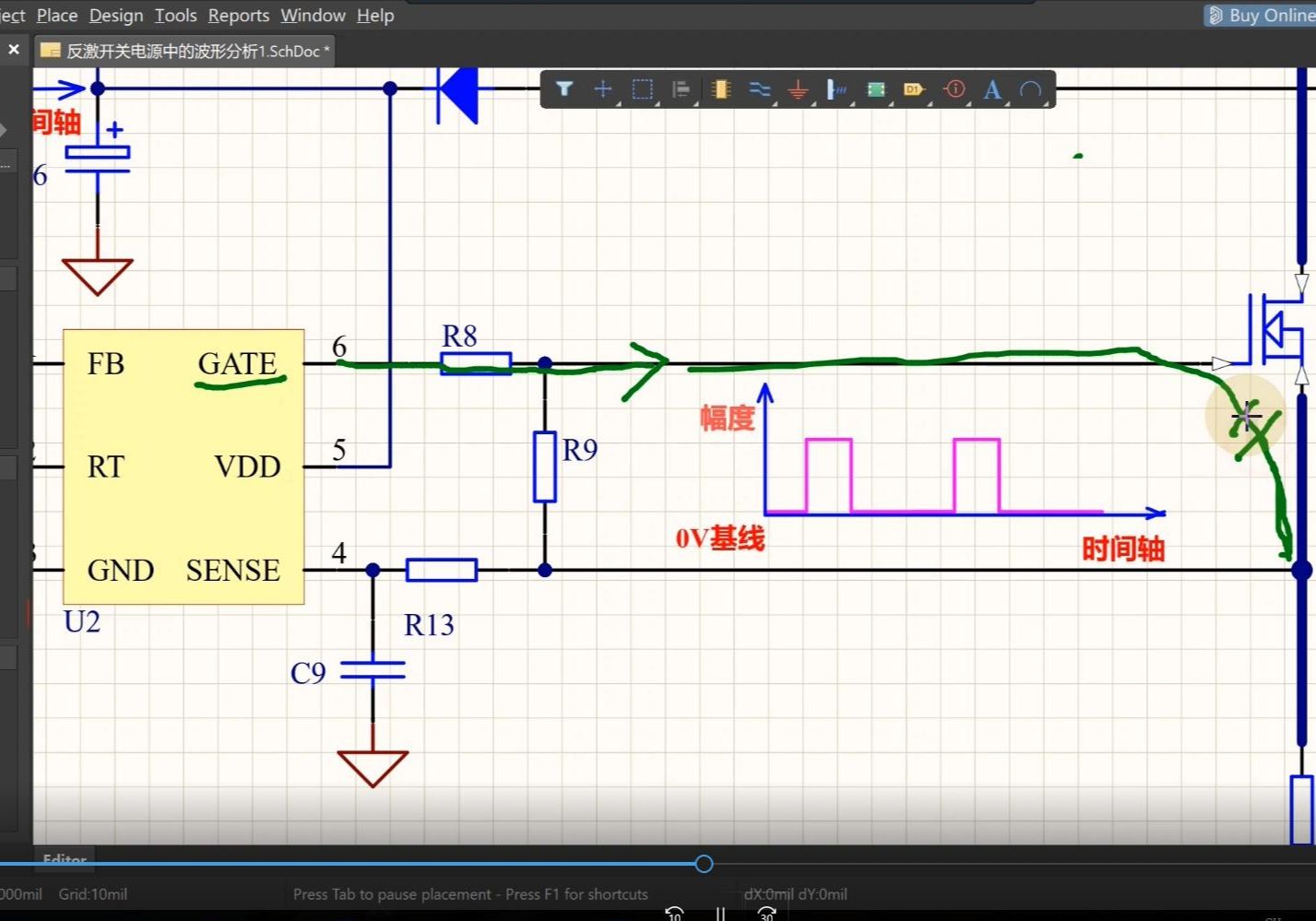

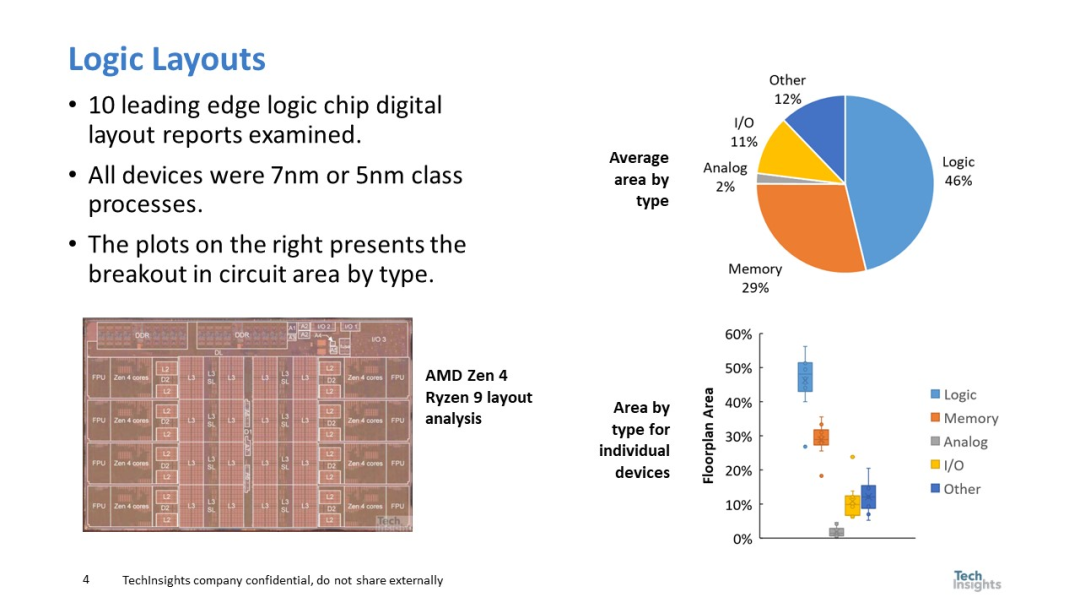

要了解逻辑器件的未来,首先要了解现代高性能芯片的组成。如图 1 所示,最先进的逻辑器件由占芯片面积不同比例的几个关键元件组成。

图 1. 逻辑布局逻辑器件占芯片面积的比例略低于一半,SRAM 等存储器约占三分之一,其余面积用于 I/O、模拟元件和其他杂项元件。有趣的是,测得的 SRAM 面积往往小于系统级芯片 (SoC) 产品通常引用的百分比。

图 1. 逻辑布局逻辑器件占芯片面积的比例略低于一半,SRAM 等存储器约占三分之一,其余面积用于 I/O、模拟元件和其他杂项元件。有趣的是,测得的 SRAM 面积往往小于系统级芯片 (SoC) 产品通常引用的百分比。

逻辑部分: 标准单元

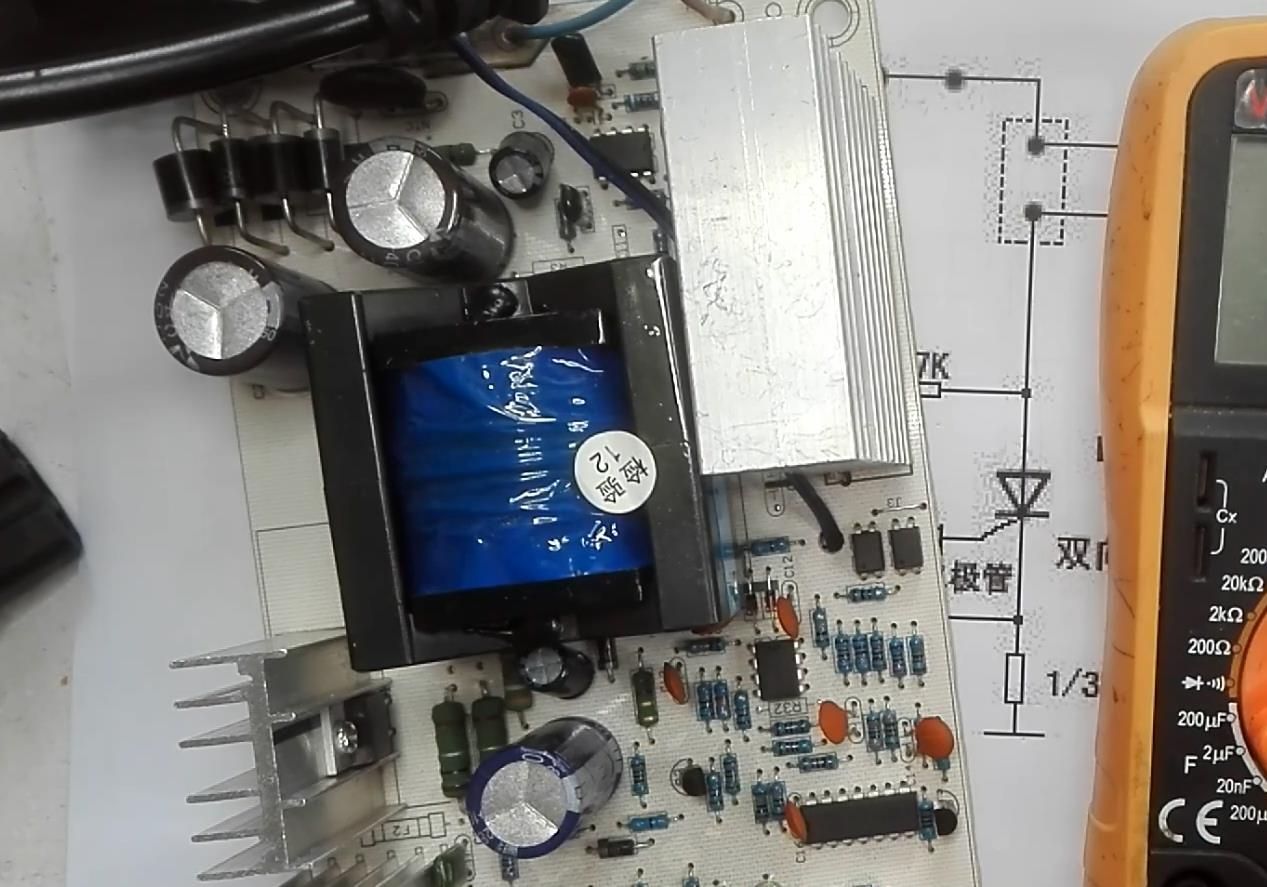

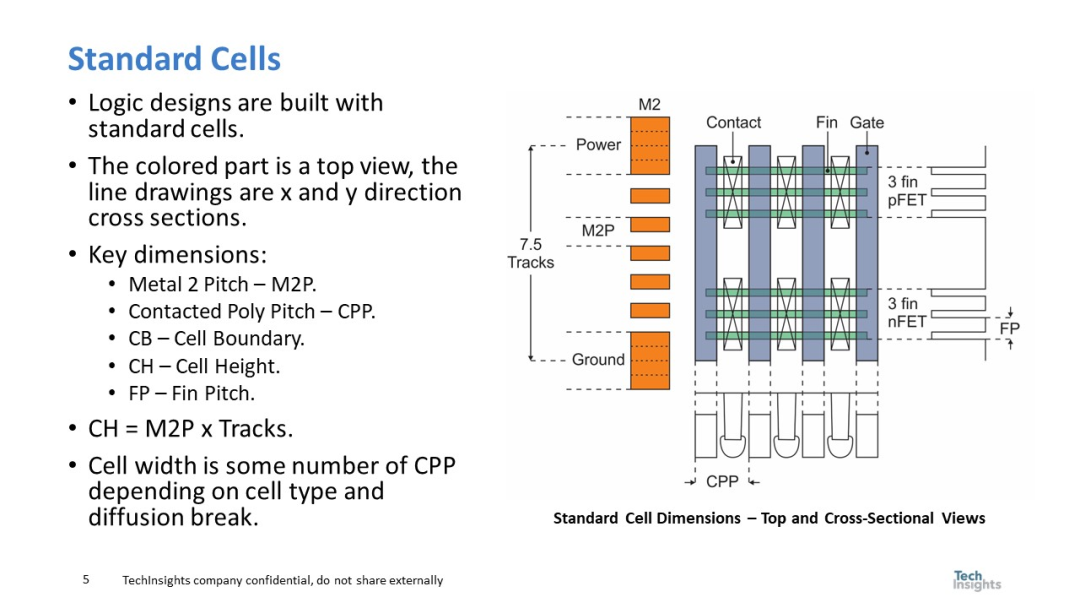

既然逻辑在芯片中占如此重要的部分,我们就从这里开始。逻辑设计使用标准单元,标准单元是基本的构建模块。图 2 显示了典型标准单元的结构。

图 2. 标准单元标准单元的高度取决于金属间距(M2P)乘以轨道数,受右图所示器件横截面结构的限制。同样,电池的宽度取决于底部的接触式多点间距(CPP)和器件横截面结构。

图 2. 标准单元标准单元的高度取决于金属间距(M2P)乘以轨道数,受右图所示器件横截面结构的限制。同样,电池的宽度取决于底部的接触式多点间距(CPP)和器件横截面结构。

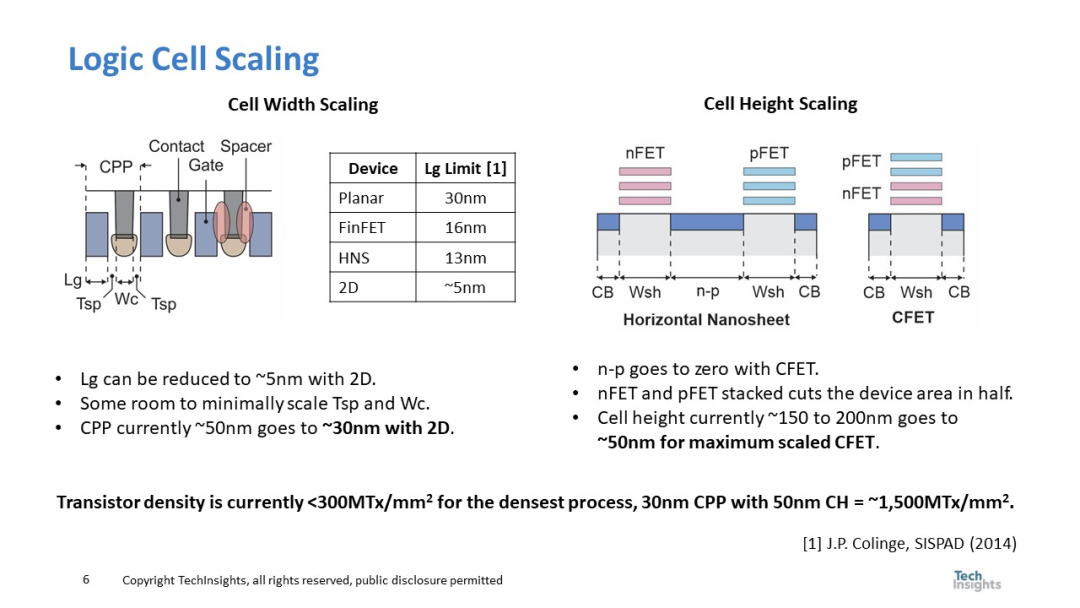

这些尺寸的缩放受到各种物理因素的限制,如图 3 所分析。

图 3. 逻辑单元缩放单元宽度的缩放由 CPP 决定,CPP 包括栅极长度 (Lg)、触点宽度 (Wc) 和触点到栅极间距厚度 (Tsp)。虽然不同类型的器件对 Lg 有不同的限制,但由于寄生效应,Wc 和 Tsp 在进一步扩展时面临挑战。

图 3. 逻辑单元缩放单元宽度的缩放由 CPP 决定,CPP 包括栅极长度 (Lg)、触点宽度 (Wc) 和触点到栅极间距厚度 (Tsp)。虽然不同类型的器件对 Lg 有不同的限制,但由于寄生效应,Wc 和 Tsp 在进一步扩展时面临挑战。

单元高度扩展已从传统的鳍式场效应晶体管设计发展到水平纳米片(HNS),从而实现了单纳米片堆叠而不是多鳍片。随着互补场效应晶体管(CFET)向堆叠器件发展,通过垂直堆叠 nFET 和 pFET,可以消除水平 n-p 间距。

与目前每平方毫米约 3 亿个晶体管相比,结合按比例的 CPP 和单元高度,晶体管密度可高达每平方毫米约 15 亿个晶体管(MTx/mm²)。不过,利用二维材料实现如此高的密度可能要到 2030 年代中后期才能实现。

行业路线图和公告

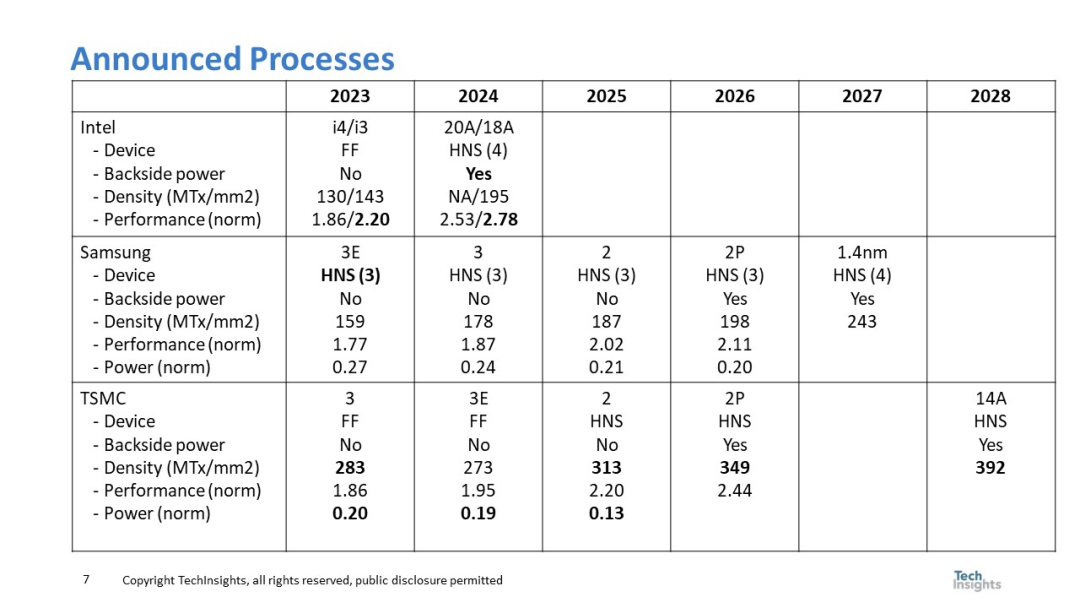

图 4 总结了英特尔、三星和台积电公布的工艺,包括器件类型、背面功率传输、密度、功率和性能数据(如有)。

图 4. 已公布的工艺主要创新包括三星在 2023 年提前采用 HNS、英特尔在 2024 年推出背面功率交付,以及台积电在密度和功率方面的领先地位。

图 4. 已公布的工艺主要创新包括三星在 2023 年提前采用 HNS、英特尔在 2024 年推出背面功率交付,以及台积电在密度和功率方面的领先地位。

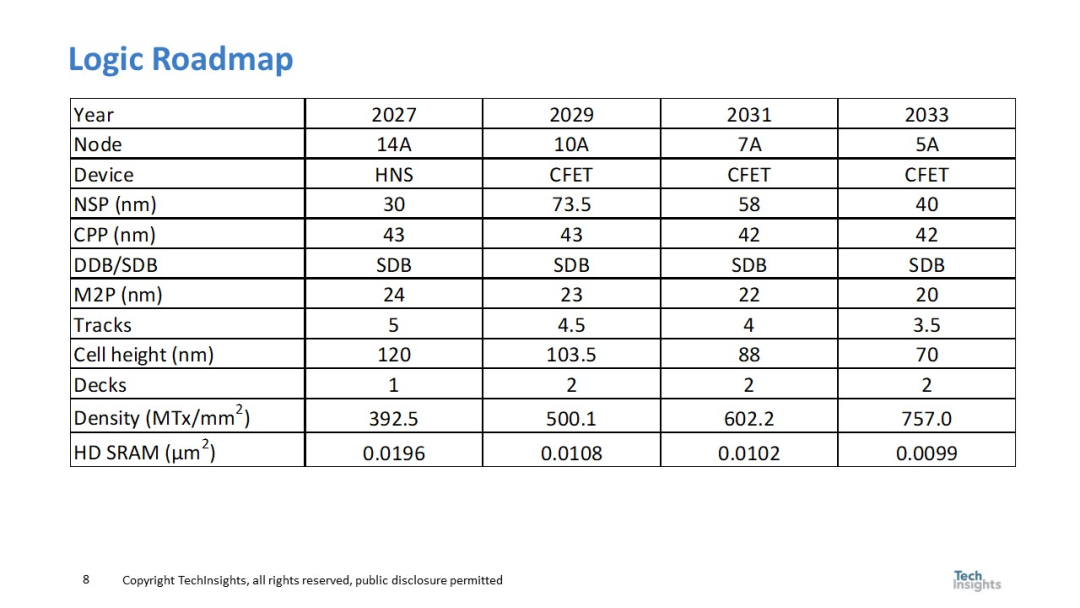

图 5 展示了逻辑路线图,预测了 SRAM 单元尺寸和整体逻辑密度趋势。 图 5. 逻辑路线图预计 2029 年前后 CFET 的推出将提高逻辑密度,并将 SRAM 单元尺寸减小近一半,而 SRAM 单元尺寸在最近的节点上一直停滞不前。预计到 2034 年,整体逻辑密度将达到约 757 MTx/mm²。

图 5. 逻辑路线图预计 2029 年前后 CFET 的推出将提高逻辑密度,并将 SRAM 单元尺寸减小近一半,而 SRAM 单元尺寸在最近的节点上一直停滞不前。预计到 2034 年,整体逻辑密度将达到约 757 MTx/mm²。

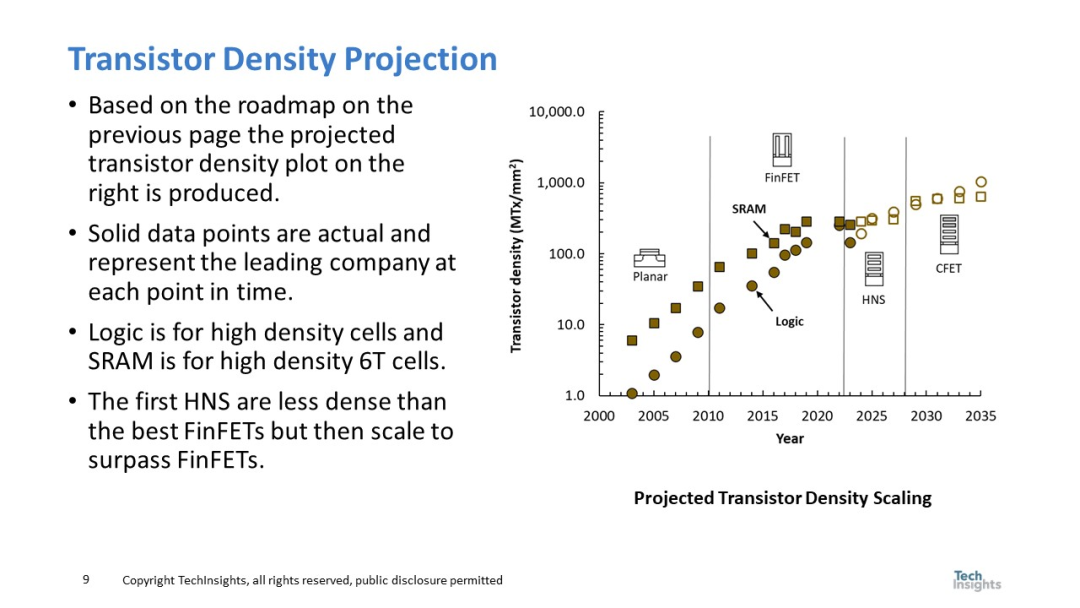

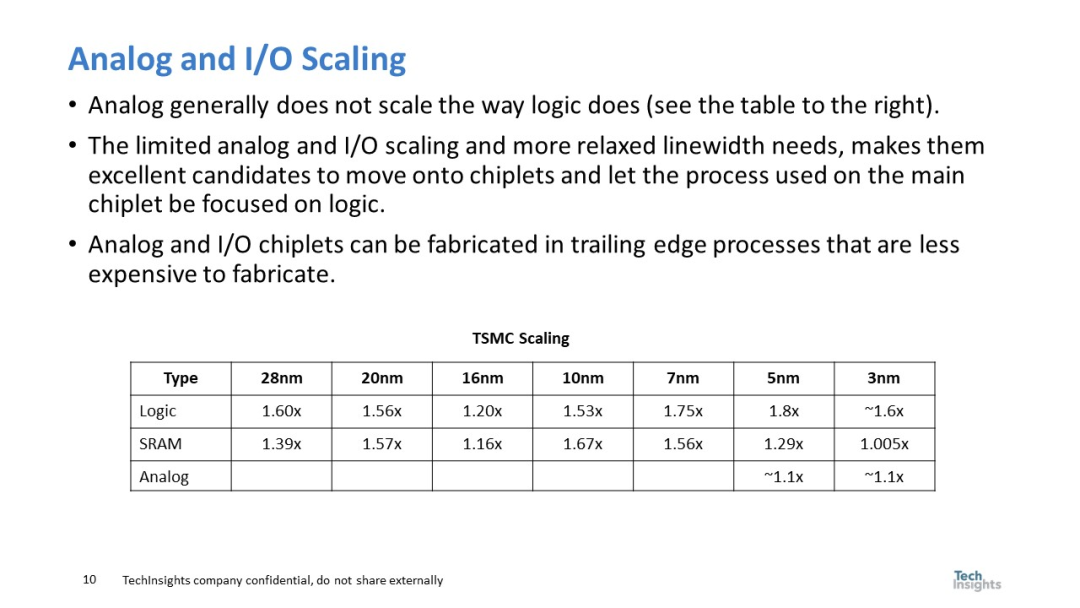

图 6 显示了逻辑和 SRAM 晶体管密度放缓但持续增长的情况,目前逻辑密度与 SRAM 相似。 图 6. 晶体管密度预测与逻辑和 SRAM 相比,模拟和 I/O 的扩展速度更慢,如图 7 利用台积电数据所示。

图 6. 晶体管密度预测与逻辑和 SRAM 相比,模拟和 I/O 的扩展速度更慢,如图 7 利用台积电数据所示。 图 7. 模拟和 I/O 扩展经济和成本考虑

图 7. 模拟和 I/O 扩展经济和成本考虑

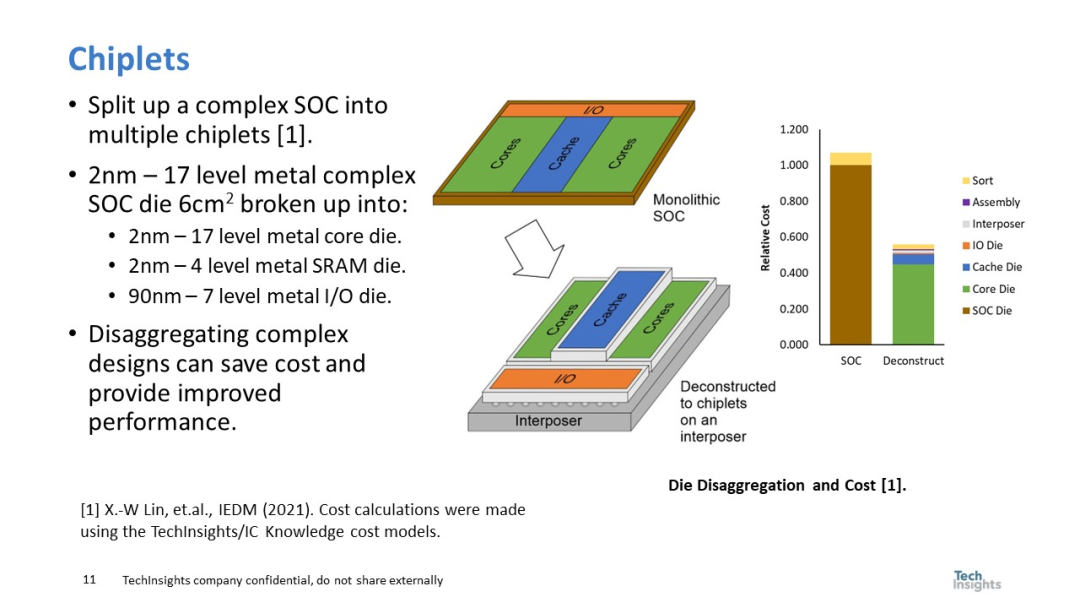

如图 8 所示,SRAM、模拟和 I/O 组件扩展速度较慢的一个潜在解决方案是使用Chiplets。通过将大型 SoC 分解成优化的Chiplets,即使考虑到封装和组装成本的增加,也能显著节约成本。

图 8. Chiplets图 9 显示了逻辑、SRAM 和 I/O 工艺的归一化晶圆和晶体管成本。

图 8. Chiplets图 9 显示了逻辑、SRAM 和 I/O 工艺的归一化晶圆和晶体管成本。

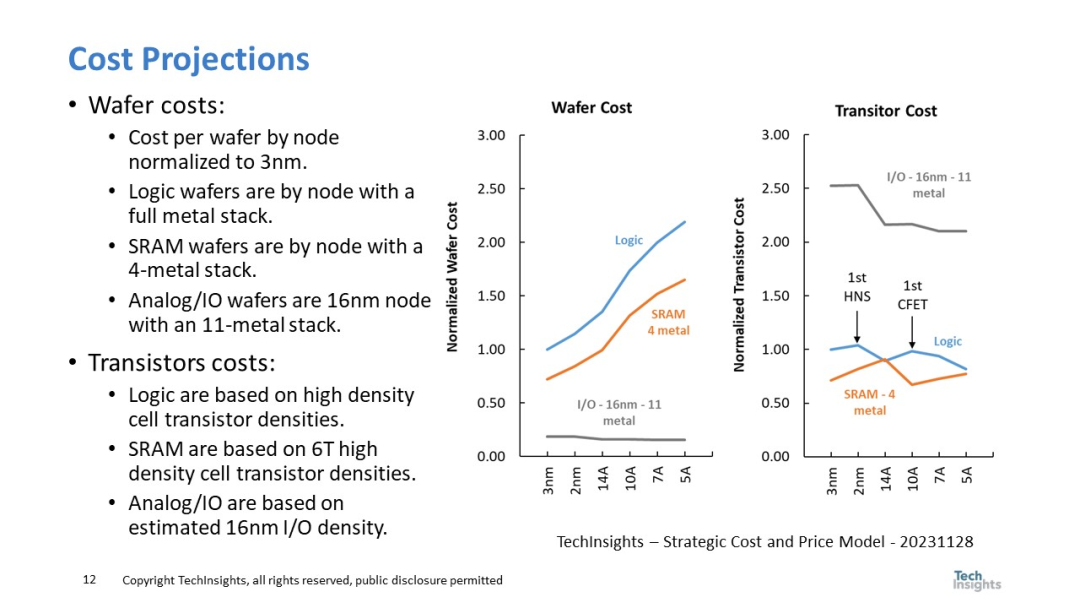

图 9. 成本预测虽然逻辑晶圆成本因金属层的增加而继续增加,但 SRAM 晶圆因其常规布局而可以利用较少的金属层。I/O 晶圆成本基于低成本的 16 纳米 FinFET 节点,以确保足够的性能。

图 9. 成本预测虽然逻辑晶圆成本因金属层的增加而继续增加,但 SRAM 晶圆因其常规布局而可以利用较少的金属层。I/O 晶圆成本基于低成本的 16 纳米 FinFET 节点,以确保足够的性能。

将晶圆成本转换为晶体管成本,I/O 晶体管的成本最高,因为其尺寸较大,尽管是在成本较低的节点上制造。逻辑晶体管成本在最初的 2 纳米 HNS 和 CFET 节点上飙升,但预计之后将恢复缩减。SRAM 晶体管成本则因缩减幅度有限而呈上升趋势,但 CFET 的一次性缩减效益除外。

总体而言,晶体管成本的降幅预计不大,但Chiplets可提供一次性的成本节约机会。

可持续性和碳足迹

解决半导体制造的碳足迹问题对于可持续发展很重要。图 10 解释了造成公司碳足迹的不同 "范围"。

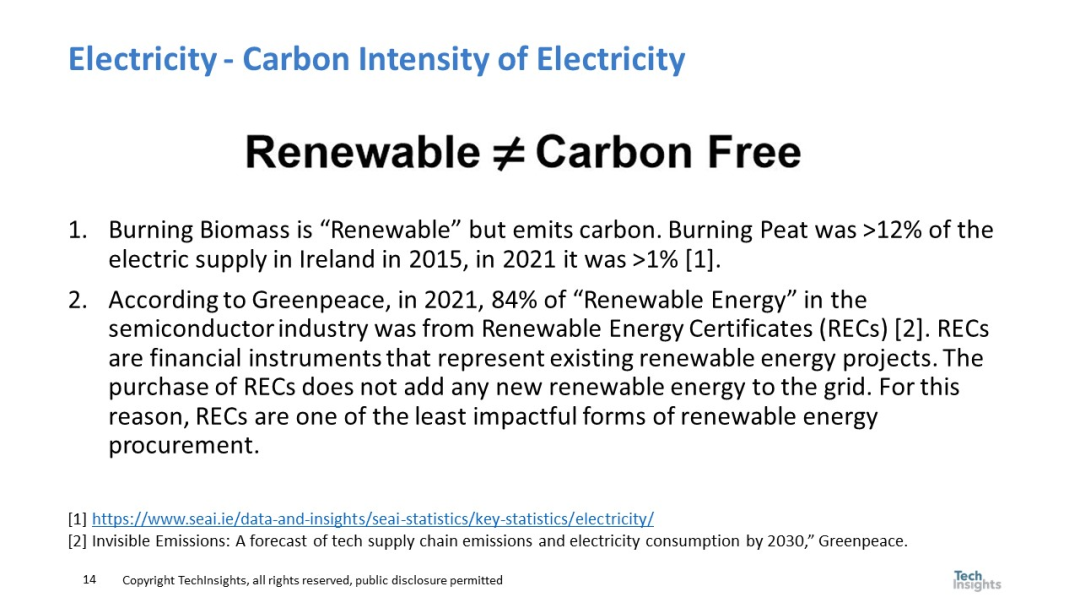

图 10. 碳足迹范围虽然许多公司声称通过使用可再生能源证书实现了外购电力的零排放(范围 2),但图 11 强调指出,2021 年半导体行业 84% 的 "可再生 "能源只是经过认证的信用额度,而不是实际的低碳来源。

图 10. 碳足迹范围虽然许多公司声称通过使用可再生能源证书实现了外购电力的零排放(范围 2),但图 11 强调指出,2021 年半导体行业 84% 的 "可再生 "能源只是经过认证的信用额度,而不是实际的低碳来源。

图 11. 电力的碳强度

图 11. 电力的碳强度

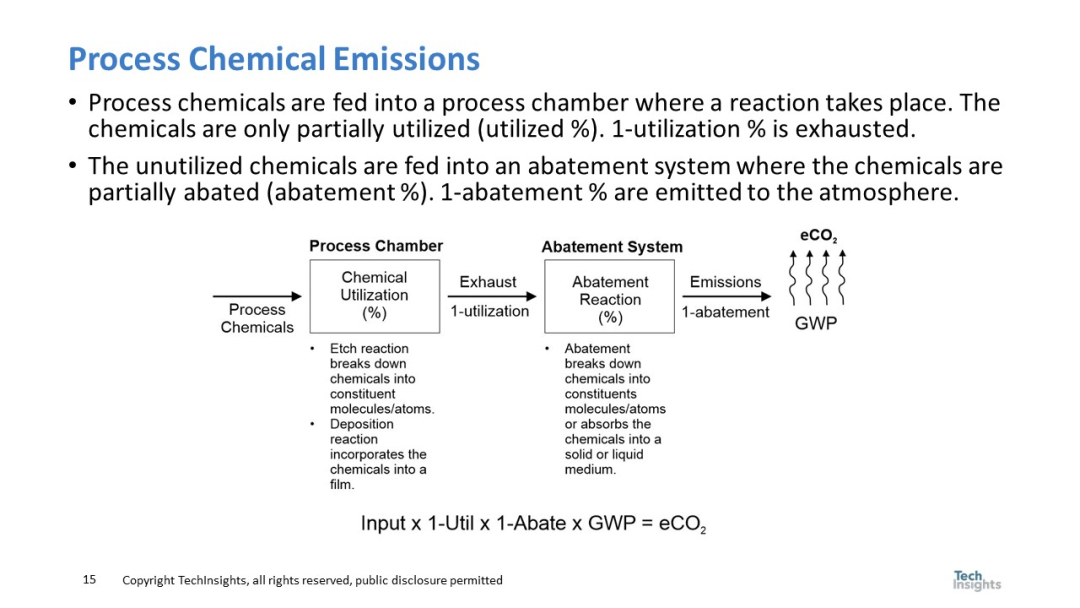

图 12 所示的工艺化学品排放是造成碳足迹的另一个重要因素。

图 12. 工艺化学品排放

从工艺室中逸出的化学品百分比(1-利用率)和减排系统的有效性(1-减排量)决定了向大气的排放量。然后将这些排放量乘以其全球升温潜能值 (GWP),计算出二氧化碳当量。

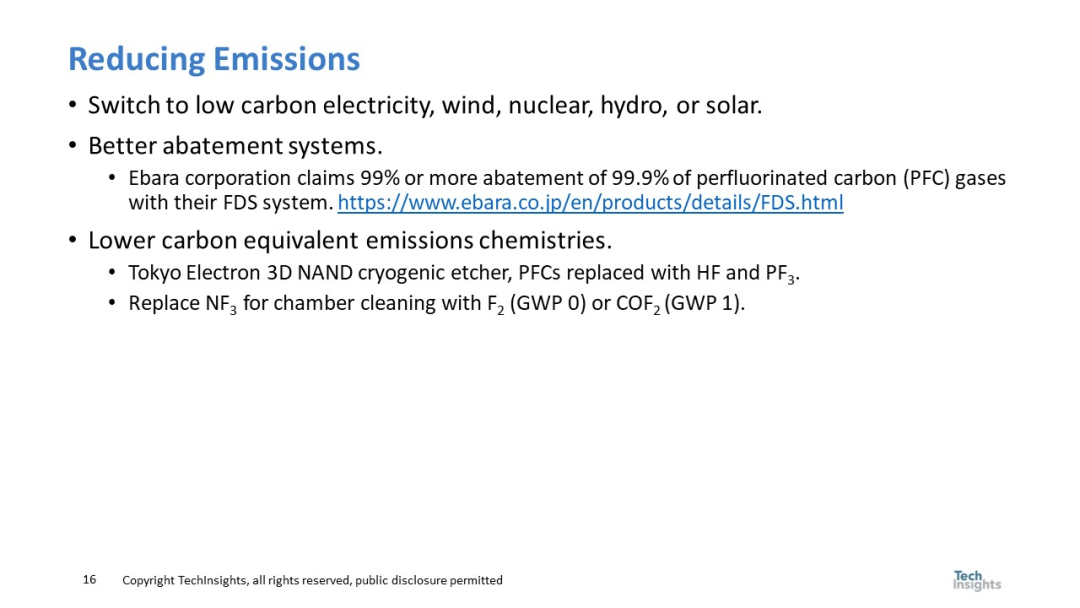

如图 13 所示,有几种减排方案可供选择。 图 13. 减少排放这些方案包括过渡到低碳电力来源、提高减排系统效率,以及采用氟 (F₂) 或 COF₂ 等低排放化学物质代替 SF₆ 和 NF₃ 等高全球升温潜能值气体。

图 13. 减少排放这些方案包括过渡到低碳电力来源、提高减排系统效率,以及采用氟 (F₂) 或 COF₂ 等低排放化学物质代替 SF₆ 和 NF₃ 等高全球升温潜能值气体。

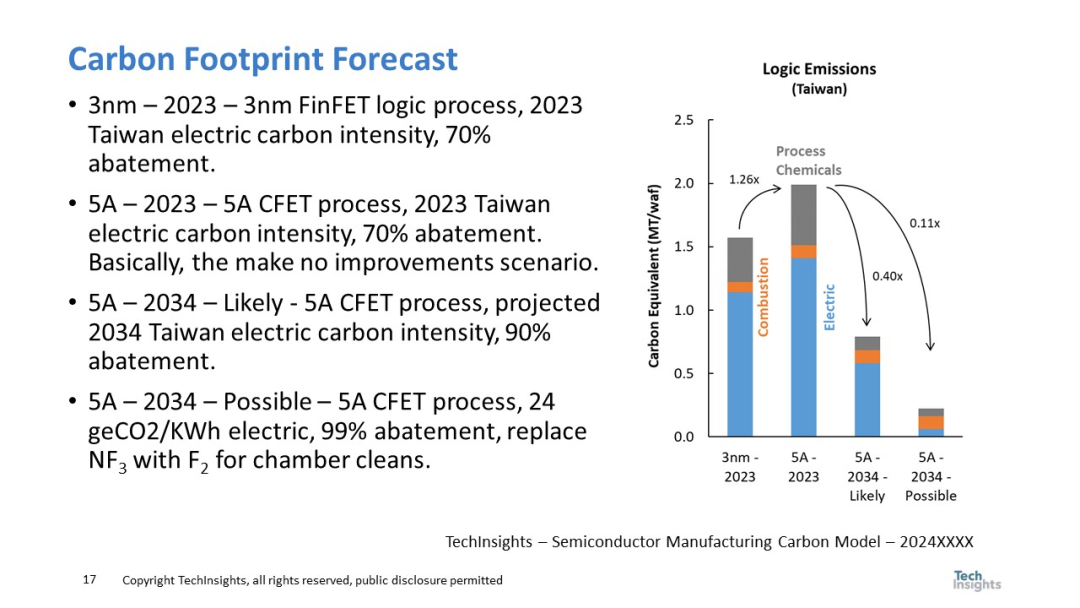

考虑到电力来源、减排效率和化学品选择等因素,图 14 预测了逻辑过程的碳足迹。

图 14. 碳足迹预测虽然可以逐步改善,但需要在低碳电力、高效减排(99%)和零全球升温潜能值化学品方面进行大量投资,以大幅减少逻辑制造的碳足迹。

图 14. 碳足迹预测虽然可以逐步改善,但需要在低碳电力、高效减排(99%)和零全球升温潜能值化学品方面进行大量投资,以大幅减少逻辑制造的碳足迹。

结论

如图 15 所示,在 HNS 和 CFET 等创新技术的推动下,逻辑器件的规模将继续扩大,尽管速度会有所放缓。预计到 2034 年,晶体管密度将达到约 757 MTx/mm²,而晶圆和芯片成本预计将出现小幅增长。

图 15. 总结解决半导体制造的碳足迹问题需要各方共同努力,包括采用低碳电力资源、高效减排系统和使用低排放工艺化学物质。

图 15. 总结解决半导体制造的碳足迹问题需要各方共同努力,包括采用低碳电力资源、高效减排系统和使用低排放工艺化学物质。

逻辑器件的未来将取决于技术创新、经济考虑和可持续发展承诺之间的平衡,因为行业将继续推进性能极限,同时最大限度地减少对环境的影响。

扫码关注

扫码关注