《SiP前世今生》系列文章由Cadence专栏作者Paul McLellan撰写。该系列共三篇文章,前两篇聚焦于SiP的驱动因素与技术发展,最后一篇内容重在阐明SiP的设计挑战与解决方案。

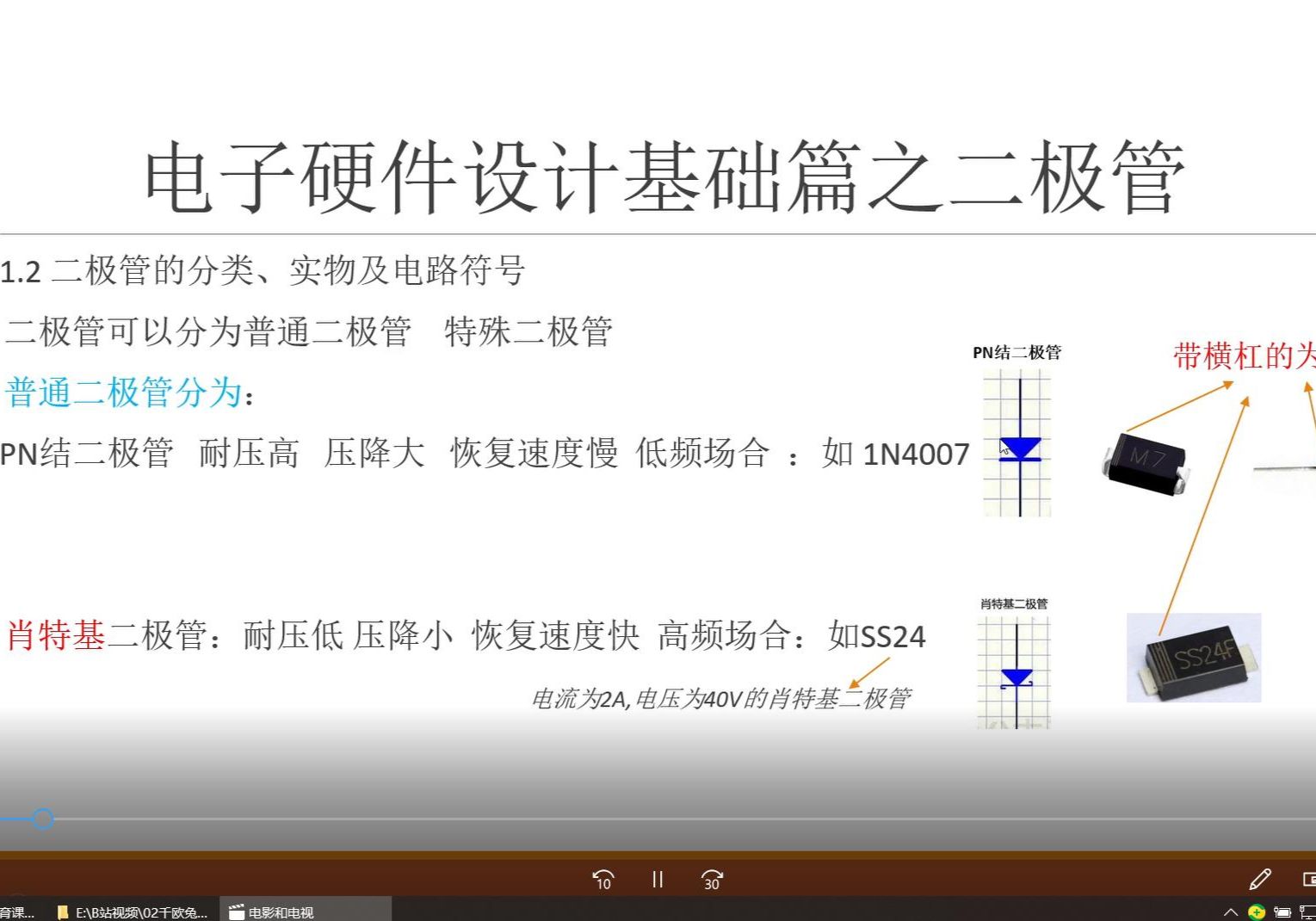

异质性

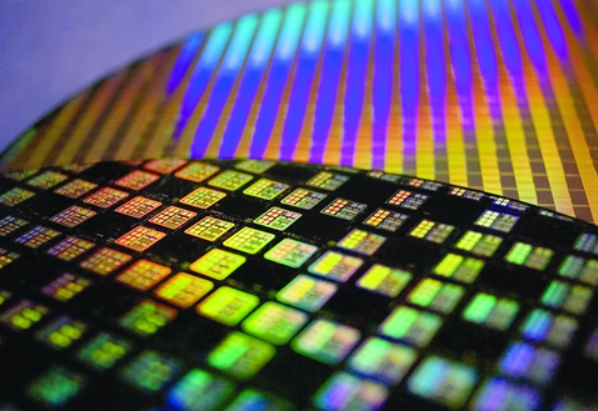

采用分离芯片的一个动因不仅仅是在单个制程中分割设计,而是封装来自不同制程的芯片。

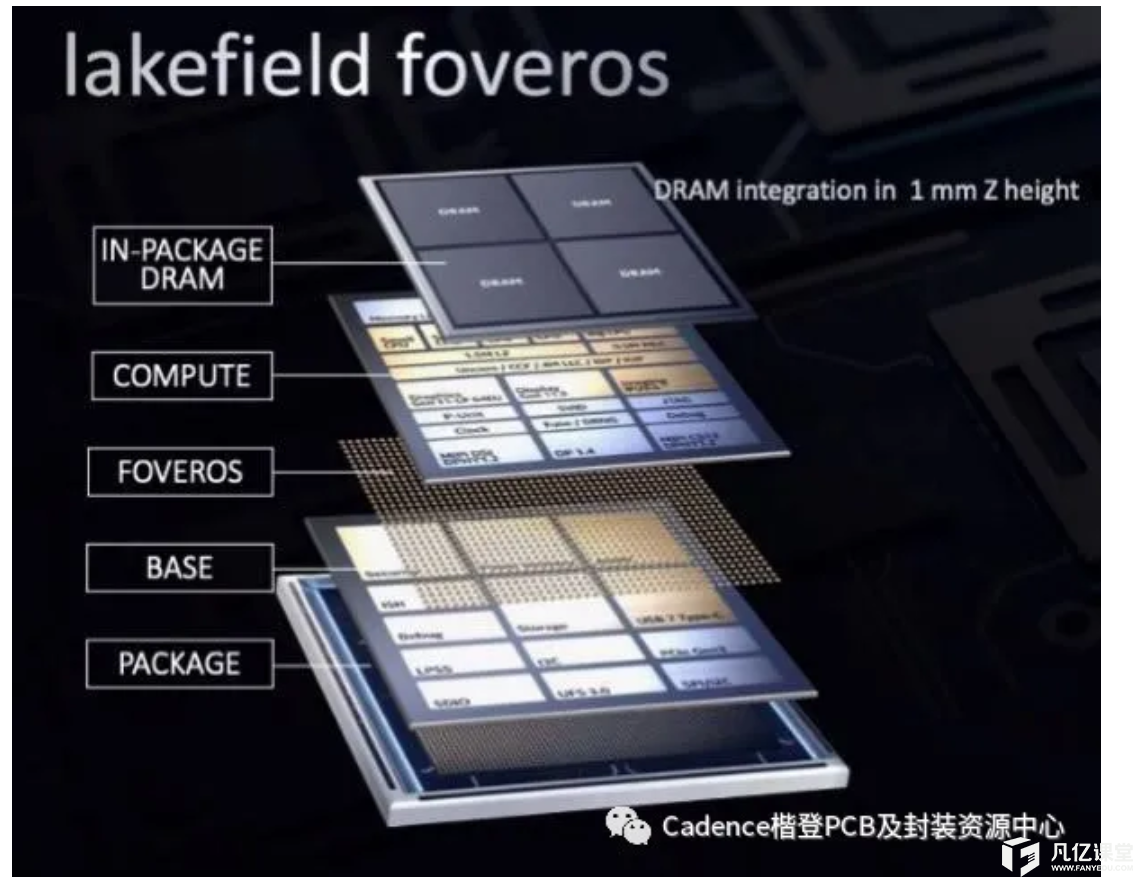

另一动因来自经济方面。HOT CHIPS大会上的演讲将设计分割成处理器本身和设计的I/O部分。处理器可以采用最先进、最昂贵的节点制造,而I/O则可以采用不够先进、较便宜的节点制造(通常落后一代)。下方图片是Intel的Lakefield芯片,它有一个I/O基片(采用非前沿的14纳米制程),10纳米制程的处理器,以及封装在顶部的动态随机存取存储器(DRAM)。这些都采用Intel的Foveros 3D技术组装。

这样做有两方面的原因。最显而易见的原因是,采用更先进的节点无法提高I/O接口的性能。当今,晶体管的先进节点更加昂贵,所以受经济因素的限制而不能大力推广先进节点的发展。但还有一个更微妙的原因。在生产中或者至少在测试芯片中,所有的I/O(和其他常规模块)都已经集成到硅片中。如果I/O芯片也采用最先进的制程技术生产,那么高速SerDes等的测试芯片就会构成退出整个系统的关键路径。

采用先进节点时,射频和模拟获益更少。事实上,不仅不会受益,还将成为不利因素。采用鳍式场效应晶体管(FinFET)的制程来设计模拟电路非常困难,因为FinFET是量子化的。晶体管的长度是统一固定的,而宽度是鳍的整数倍。在平面制程中,模拟电路设计人员可以选择晶体管的宽度和长度。模拟设计中,最重要的通常是关键晶体管之间的尺寸比。但是在FinFET中,两个晶体管的尺寸比不能为任意数值,所以需要进行模拟设计。继续采用28纳米等平面制程,甚至是65纳米等较为不成熟的节点进行模拟设计更为合理,因为采用这样的制程工艺进行设计(比如:模数转换器)已经实现了很好的例化以及大规模生产。

虽然我不是射频方面的专家,但我知道,几乎不可能采用FinFET制程来设计射频,因为FinFET晶体管本身具有高电容。对于射频,互连的高电阻也能成为一个问题。

另一方面,采用单独的芯片对一些光电器件来讲是具有吸引力的。尽管核心芯片上会布置一些光电元件,但不大可能布置激光器。通常,激光器采用InP(磷化铟)制造。在2019年美国举办的Photonics Summit上,Intel的主题便是构建双芯片解决方案,然后进行晶圆对晶圆的连接。

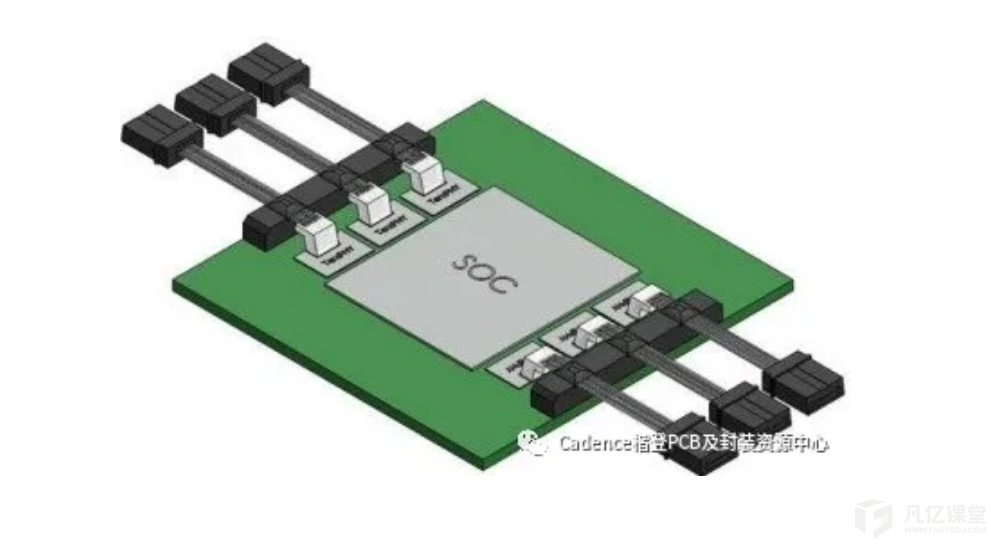

在HOT CHIPS大会上,Ayar Labs介绍了其TeraPhy芯片,这是一种小型光学芯片,可以添加到系统级芯片封装中,用以提供光学连接,如下图所示:

Chiplets

目前,在讨论多芯片封装的3D设计时,都有个假设前提,即:这些芯片均由同一个团队设计,或者至少由同一个公司设计;该假设不包含DRAM,因为DRAM都来自专业的DRAM制造商。DRAM必须大规模生产才会具有竞争力,而“大规模”指整厂一次产量。

但也存在另一种可能,那就是封装内器件实现商业化销售。此处的封装内器件便是Chiplets。其商业化销售还面临着若干挑战。其中一些是技术上的挑战,除此之外还有两个挑战——标准化和市场。事实上,Cadence目前有一个项目正致力于解决其中一些问题(具体内容见《行业洞察 I DARPA电子复兴计划:风口上的Chiplets能飞起来吗?》一文)。

如果同一个团队正在设计的两个芯片将放入同一个封装中,他们几乎可以选择任意通信方案。但是,如果chiplets在某种意义上是标准的,例如,高速SerDes chiplet或WiFi chiplet,那么系统级芯片必须使用该chiplet提供的接口。为了使工作简单化,接口最好经过验证,且是标准接口。封装内的各种距离都较短,因此不宜采用适合在底板上运行的同类型长距离SerDes。另一个优势是,相比通过封装传输到电路板,在封装内进行大量连接的成本相对较低(例如,宽版内存可以有数千个连接,而不用在八个或九个通道中传输所有数据)。

Cadence于2019年底发布了UltraLink D2D PHY IP产品,以及一款测试芯片(或测试chiplet),并对其进行了硅验证。该测试chiplet采用了我们的40Gbps SerDes,设计功耗非常低,并且能够最大限度地提高chiplet边缘(有时称为海滨)的连接性,而由于间距非常小,并不需要采用昂贵的制程。

Chiplet技术的支持者希望形成一个基于已知合格芯片(KGD)的chiplets市场,如此一来,便可以像在开放市场上购买HBM一样,购买各种各样的chiplets。设计也会变得更像电路板级的系统设计:可购买标准器件,甚至可能将单个系统级芯片设计成系统的核心。

对此,我有一点怀疑,因为库存问题似乎很难解决。当我在VLSI Technology工作时,我们总是遇到门阵列基础的库存挑战。门阵列设计的好处是,所有的基础都经过预扩散,然后保存在晶圆库中。这对于小批量的简单设计来说,效果很好。但有一个艰难的权衡。晶圆库中的任何晶圆都代表着已占用且正在贬值的金钱(而且,如果新的制程时代到来,还可能会过时)。另一方面,门阵列的好处在于,晶圆库随时可用,因此可以相应缩短订单的周转时间(这段时间内,只需在存储的晶圆上添加三层金属即可)。如此,我们便不再需要具有不同内存门结构比的基础晶圆。

Chiplets的价值主张是:

可以灵活选择零件的最佳制程节点——尤其是SerDes I/O和模拟,不需要采用“核心”制程节点

由于芯片尺寸较小,良率更高

通过使用预先存在的chiplets,缩短集成电路的设计周期和整合的复杂度

通过购买已知合格芯片(KGD),降低制造成本

在多个设计中使用相同的chiplets时,具有批量制造的成本优势

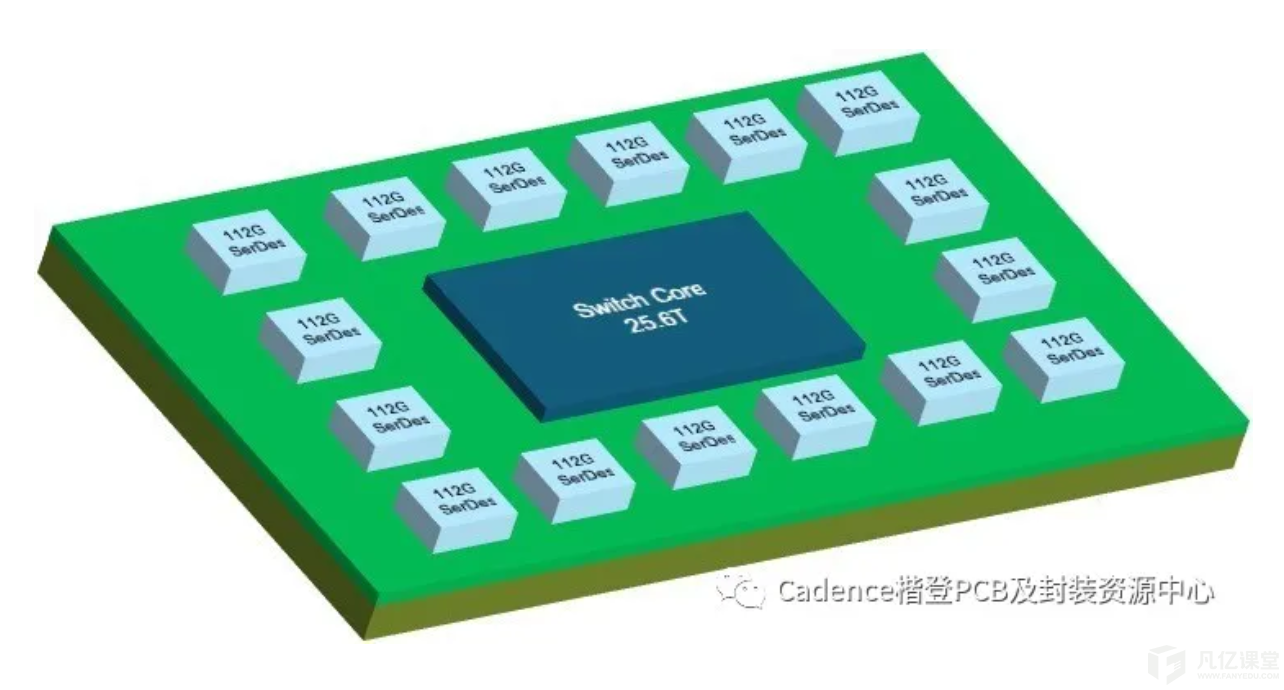

对于任何系统级封装解决方案,前几点都一样。如果可以直接从经销商那里购买chiplets,那么后三点的效果是最好的,但如果特定的系统需要专门制造的chiplets,也基本上将是这样。优势是,可以设计类似系统,如整合了112G SerDes的25.6Tbps转换器,而不是把所有SerDes接口都集成到较大核心系统级芯片上。

本篇内容至此结束,下一篇文章中我们将聚焦于SiP的设计挑战与解决方案,请大家继续关注。

扫码关注

扫码关注