《SiP前世今生》系列文章由Cadence专栏作者Paul McLellan撰写。该系列共三篇文章,前两篇聚焦于SiP的驱动因素与技术发展,最后一篇内容重在阐明SiP的设计挑战与解决方案。

超越摩尔

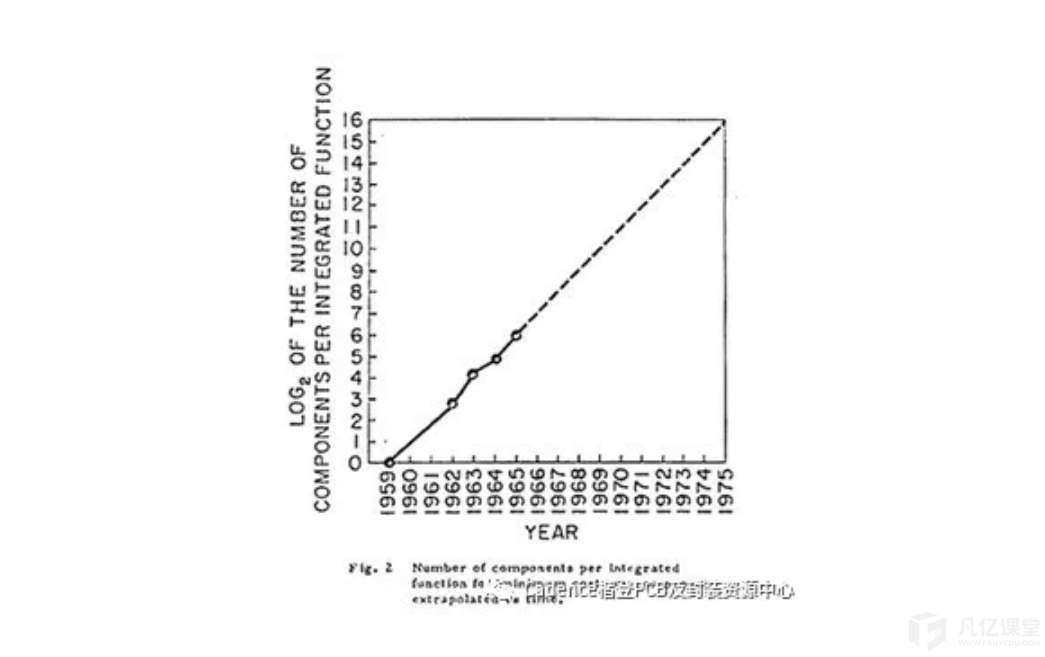

50多年来,半导体行业一直受益于摩尔定律。但是如今,半导体等比例缩小的时代已经结束。摩尔定律主要是作为一条经济法而存在——即集成电路上可容纳的晶体管数量,约每隔几年便会增加一倍。当然,是技术的发展使之成为现实;直到几年前,这一定律依然适用。高层次的经济主张是:每一代工艺将同一领域的晶体管数量增加一倍,成本仅增加15%,从而为每个晶体管节省35%的成本。但是因为当今的工艺愈发复杂,加之建造一个工厂的资本投入非常大(每台EUV步进机将耗资1亿美元),导致每一代晶体管都更加昂贵。因此我们发展出一个从7nm到5nm再到3nm的工艺路线图以及之后几代的路线图。但从经济角度来看,这些工艺不仅会像过去几十年来那样增加每个晶圆的成本,更会增加每个晶体管的成本。

戈登•摩尔很早就预料到这一天会到来,他表示从未想过摩尔定律会持续50多年。在几年前美国SEMICON West的视频采访中,当被问及他想因什么而被铭记时,戈登表示:“除了摩尔定律什么都不想。”但在《电子学》的原创论文中,他说:

事实可能会证明,用较小的功能模块构建大型系统将更加经济,而这些较小的功能模块是分开封装和互连的。

那一天已经到来。

另一个已存趋势是制造复杂的封装,即在一个封装中放置多个芯片的方法已变得更加经济。像所有大规模生产技术一样,这在很大程度上依靠大规模生产得来的经验。大型微处理器使用interposer技术;较小的(在晶体管数量和物理性能方面)通信芯片则一直使用扇出型芯片封装(FOWLP)技术。由于智能手机每年的出货量约为15亿部,这意味着任何一款型号的手机都可能出货量达到数亿部,提供了大量的生产经验。

考虑到以上因素,发展的平衡已经改变。在同一个芯片上制造大量晶体管,还是制造更小的芯片并将它们封装在一起,在经济上是一个复杂的决定。曾经,至少对于大型设计来说,经济上总是偏向单一的系统级芯片;但是现在,越来越多的事实证明天平已向复杂封装倾斜。

芯片尺寸

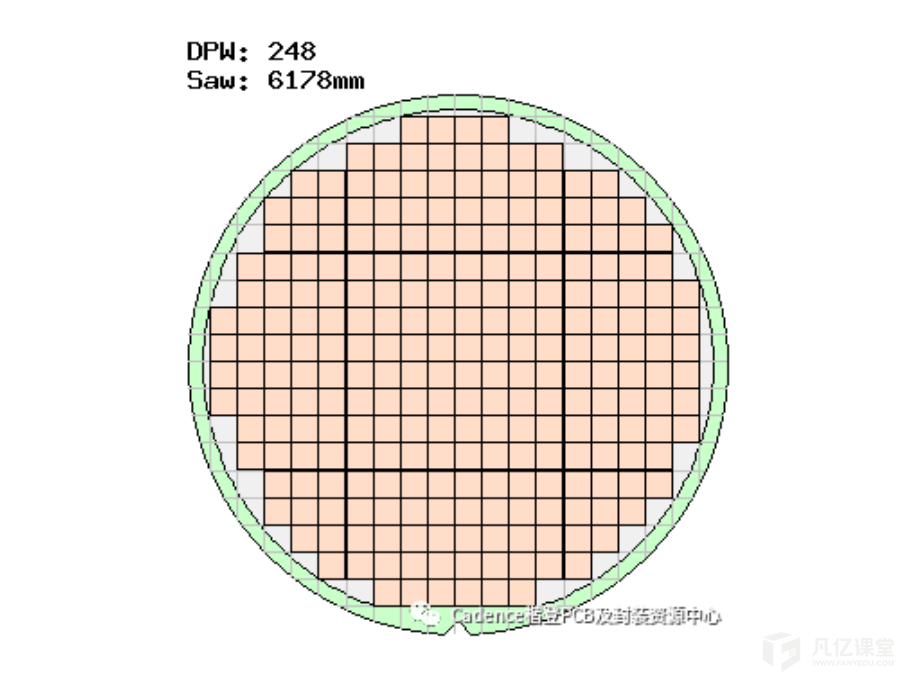

大芯片比小芯片产量低。如果致命的缺陷随机分布在晶片上,那么大芯片则更有可能存在缺陷。同时,大芯片的晶片边缘也有更多的浪费区域,因为晶圆更多而没有空间来放置芯片。过去,尽管存在上述缺点,构建大的系统级芯片也比构建单独的芯片后再将它们封装在一起更为经济。但是现在,构建小芯片却更为划算,特别是当一个完整的系统可以使用同一个芯片的多个副本时。以这种方式构建一个高级多核微处理器或一个可编程门阵列并不太具挑战性(显然毫无规律的巨大芯片无法利用这一点)。

超大设计还有一个问题:光刻工艺具有最大光掩模版尺寸。如果设计比这更大,那么进行分割是唯一的选择。

然而事实并非如此。Cerebras公司制造了世界上最大的单芯片,是可以放在300mm晶片上的最大的正方形。这种方法需要对切割线的互连进行特殊处理(并没有将芯片分开)。这也需要很强的一致性,因为所有的芯片都必须是相同的。然而,对于大多数设计来说,这种方法并不奏效。但是我们可以用微伏芯片进行晶片级集成,只需要在晶片上得到电源、地和以太网三个信号即可。也许Cerebras的方法将会得到更广泛的应用。

保持内存紧密

所有高性能处理器,无论是CPU、GPU、深度学习处理器还是其他处理器,都需要访问大存储器,以作为缓存或者直接存储(大)数据。大多数计算中的大量功耗只是简单地搬移数据,而不是进行实际计算。整体计算中的大多延迟也来自于这种搬移,所以显而易见地,我们需使内存更加靠近处理器。这将降低功耗,提高性能。

最明显的方法是把动态随机存取存储器和处理器放在同一个芯片上,但是这存在两个问题。首先,是前文讨论的芯片尺寸限制问题。其次,虽然可以混合动态随机存取存储器和逻辑处理,但成本较高。我们不能只用几个掩膜就把动态随机存取存储器添加在逻辑芯片上。

解决该问题的最早的方法被称为封装内封装(package-in-package,PiP)。该术语区别于封装上封装(package-on-package,PoP):在PoP中,两个球栅阵列(BGA)封装实际上是堆叠在一起的。两个芯片,如智能手机应用处理器和动态随机存取存储器,被放在同一个封装中,并且全部由引线键合,以避免出现像硅通孔(TSv)一样的复杂问题。这个方法已应用在智能手机上多年。

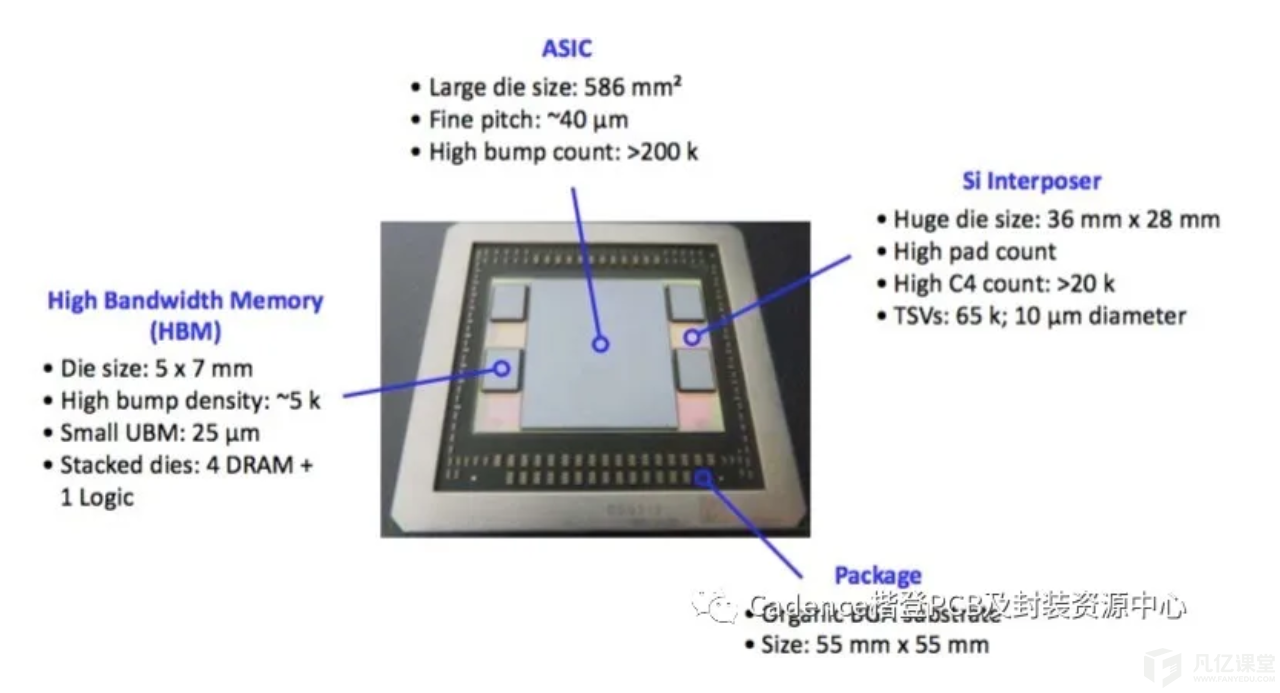

对于内存不足的高性能计算,则通常需要访问几个高带宽存储器(HBM或HBM2)。这些芯片由一个逻辑芯片和四或八个堆叠在顶部的动态随机存取存储器芯片组成,并都与硅通孔相连接。其实这已经是一个3D集成电路,尽管其本身并不具有很大的用处。然后将该电路放在处理器旁边的interposer上。下图是AMD公司的Fuji产品设计解析,Fuji是最早使用这种方法的设计之一。

还有一个JEDEC宽输入/输出标准,用于标准化高带宽内存(因此内存不依赖于设计),然后将带硅通孔的存储器放在逻辑芯片的顶部。由于宽输入/输出有1000个或更多引脚,它可以获得非常高的带宽,而不需要DDR接口上的所有SerDes。

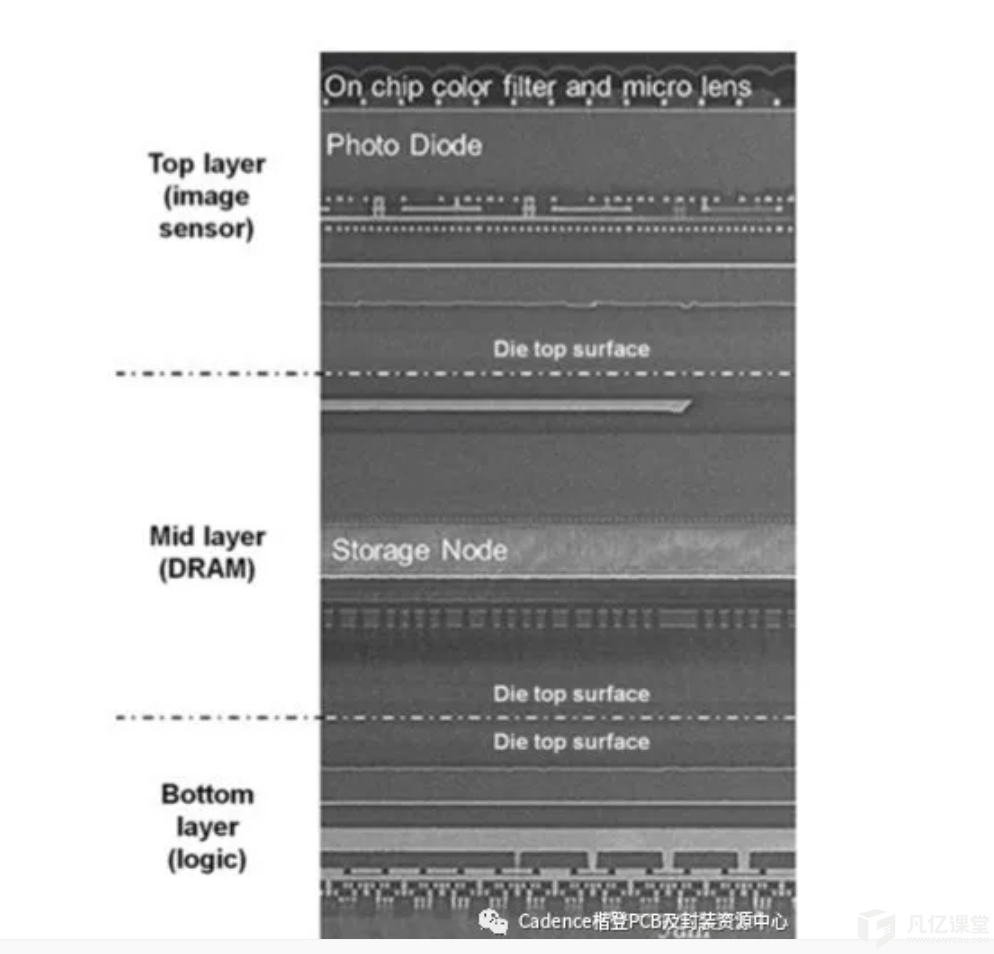

这种方法也用于互补金属氧化物半导体图像传感器(CIS)。传感器不是严格意义上的存储器,而是类似存储器:传感器的光线会穿过晶片的背面。这样,互连就不会有所妨碍。传感器变薄以透光,再将传感器进行翻转。相关的逻辑芯片被设计成完全相同的尺寸,翻转的传感器可以恰好地安装其上。有时,第三个动态随机存取存储器芯片会放入堆叠的中间。下图是三层的Sony CIS设计。

扫码关注

扫码关注