- 全部

- 默认排序

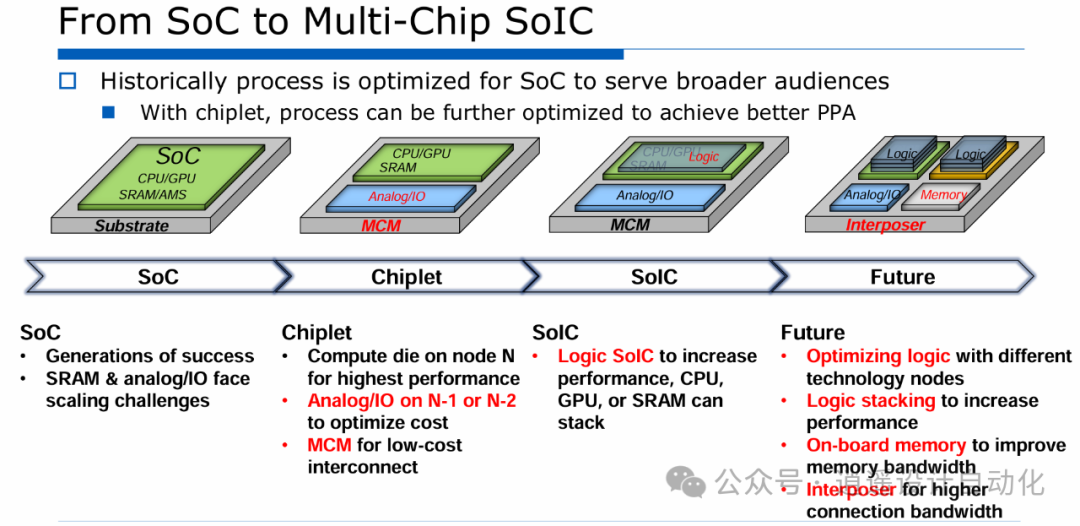

50多年来,半导体行业一直受益于摩尔定律。但是如今,半导体等比例缩小的时代已经结束。摩尔定律主要是作为一条经济法而存在——即集成电路上可容纳的晶体管数量,约每隔几年便会增加一倍。当然,是技术的发展使之成为现实;直到几年前,这一定律依然适用。高层次的经济主张是:每一代工艺将同一领域的晶体管数量增加一倍,成本仅增加15%,从而为每个晶体管节省35%的成本。但是因为当今的工艺愈发复杂,加之建造一个工厂的资本投入非常大(每台EUV步进机将耗资1亿美元),导致每一代晶体管都更加昂贵。因此我们发展出一个从7

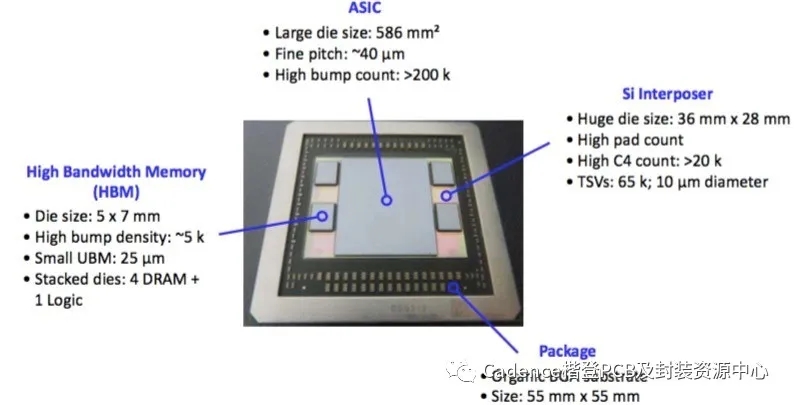

HOT CHIPS大会上的演讲将设计分割成处理器本身和设计的I/O部分。处理器可以采用最先进、最昂贵的节点制造,而I/O则可以采用不够先进、较便宜的节点制造(通常落后一代)。下方图片是Intel的Lakefield芯片,它有一个I/O基片(采用非前沿的14纳米制程),10纳米制程的处理器,以及封装在顶部的动态随机存取存储器(DRAM)。这些都采用Intel的Foveros 3D技术组装。

据日经亚洲报道,近期立讯精密、歌尔股份开始为苹果AirPods耳机提供细品封装服务,值得注意的是立讯精密提供的封装服务极有可能是“系统级封装(SiP)”服务。工程师无忧学芯片封装设计:>>SiP封装设计零基础实战教程>>IC&SiP芯片封装

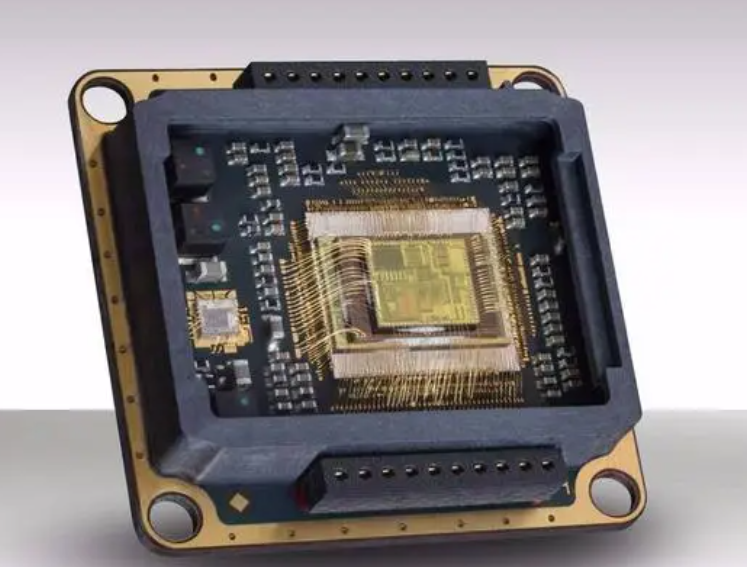

随着电子信息技术的发展和社会的需求,电子产品迭代更新速度加快,逐渐向小型化、轻量化、高性能、多功能和低成本方向发展,而系统级封装(SIP)因为具备设计灵活、短周期、兼容性好、低成本等特点开始脱颖而出,成为工程师必须优先了解的一种理想封装技术

随着集成电路技术沿摩尔定律发展至今,从第一代插孔元件、第二代表面贴装、第三代面积阵列,再到现在的芯片封装,这些封装技术以系统级封装技术(SIP)的实现奠定了基础,然而很少工程师知道,良好的SIP可明显改善电磁兼容和信号完整性问题。所谓的系统

在电子工程领域内,封装技术对于芯片的稳定性、性能及成本都有着至关重要的影响,其中,SIP封装作为一种灵活且可扩展的封装形式,被广泛应用在各种实时通信应用程序,本文将谈谈SIP封装的分类及优缺点,希望对小伙伴们有所帮助。1、单列直插式封装(S

Agilex™ FPGA 家族基于10纳米技术,可为各种计算密集型和带宽密集型应用提供定制加速和连接,同时提高性能并降低功耗。 Agilex™ FPGA 家族采用异构 3D 系统级封装 (SiP) 技术,集成了首款基于 10 纳米制程技术的

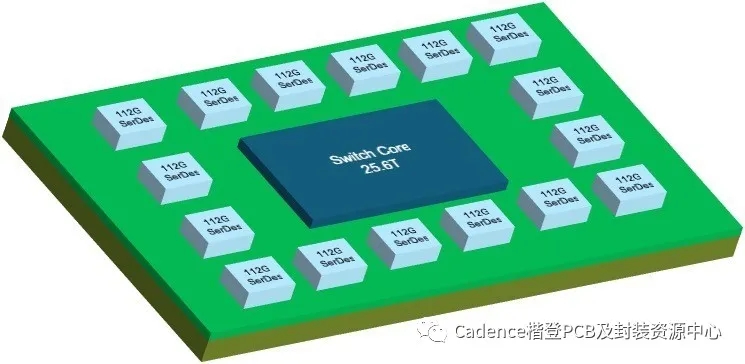

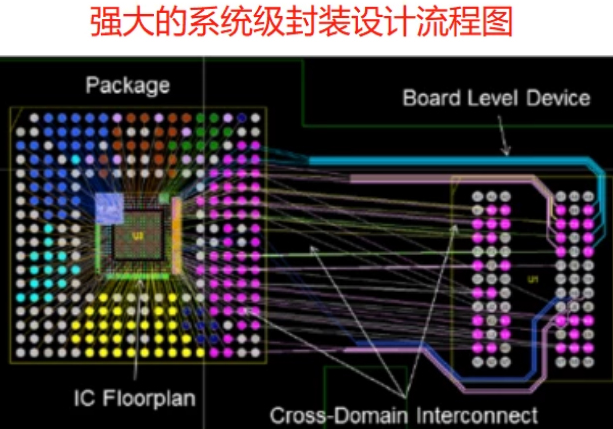

简介在生成式人工智能、高性能计算 (HPC) 和数据中心的推动下,人们对计算能力的需求不断增长,这也刺激了对先进 CMOS 工艺和封装技术的需求。为满足这一日益增长的需求,半导体行业正在推动到 2030 年实现万亿晶体管三维集成电路(3DIC)系统级封装(SiP)解决方案。本文将探讨台积电推动采用c

扫码关注

扫码关注