自从华为中芯国际等多家中企被美国制裁封杀,国人开始知道半导体芯片的重要性,并提出国产全面化口号大力发展本土企业,芯片加工工艺作为芯片的关键环节也得到了许多关注,这也造成多种领域的电子工程师必须对集成电路基本加工工艺流程有一定的了解,所以本文将详谈集成电路基本加工工艺流程。

集成电路的基本加工工艺流程如下:

1、外延生长

不同的外延工艺可制备不同的材料系统,目前常见的外延技术为化学气相沉积(CVD)、金属有机物气相沉积(MOCVD)和分子束外延生长(MBE)。

2、掩膜制版工艺

①掩膜功能

在集成电路开始制造之前,需要预先设定好每个工艺的制造过程和先后顺序。每个工艺中都需要掩膜来覆盖暂时不需要加工的位置,需要加工的位置则需要按照一定的图形来加工。版图设计就是将集成电路的布局按照集成电路工艺过程分为多层掩膜版的过程将这些过程制作成掩膜版的过程就是制版。

制版就是要产生一套分层的版图掩膜,为将来将设计的版图转移到晶圆上做准备,掩膜版主要用在光刻工艺过程中。

②掩膜制造

掩膜版可分成:整版及单片版,整版是指晶圆上所有的集成电路芯片的版图都是有该掩膜一次投影制作出来的。各个单元的集成电路可以不同。

单片版是指版图只对应晶圆上的一个单元。其他单元是该单元的重复投

影。晶圆上各个芯片是相同的。

早期掩膜制造是通过画图照相微缩形成的。

光学掩膜版是用石英玻璃做成的均匀平坦的薄片,表面上涂一层60~80nm

厚的铬,使其表面光洁度更高,这称之为铬版(Cr mask),通常也称为

光学(掩膜)版。

新的光刻技术的掩膜版与光刻技术有关。

③图案发生器方法

集成电路上任何一个图形都可以由无数个矩形形成,任何一个矩形都有在空间的坐标和长和宽。将分割的所有图形的参数记录并制版,得初缩板,初缩板用来重复投影制作掩膜版,此外还有X射线制版法,电子束扫描法。

3、氧化工艺

在集成电路的制作过程中要对硅表面反复进行氧化,制备SiO2薄膜。生长SiO2薄膜的方法有多种,如热氧化、阳极氧化、化学气相淀积等。其中以热氧化和化学气相淀积(CVD)最为常用。热氧化生成SiO2薄膜是将硅片放入高温( 1000~1200°C)的氧化炉内,然后通入氧气,在氧化环境中使硅表面发生氧化,生成SiO2薄膜。热氧化分为干氧法和湿氧法两种。

4、掺杂工艺

①热扩散法掺杂

利用原子在高温下的扩散运动,使杂质原子从浓度很高的杂质源向硅中扩散并形成一定的分布。

热扩散通常分两个步骤进行:

预淀积(predeposition,也称预扩散);

推进(drive in,也称主扩散)

②离子注入法掺杂

离子注入掺杂也分为两个步骤,分别是离子注入和退火再分布。

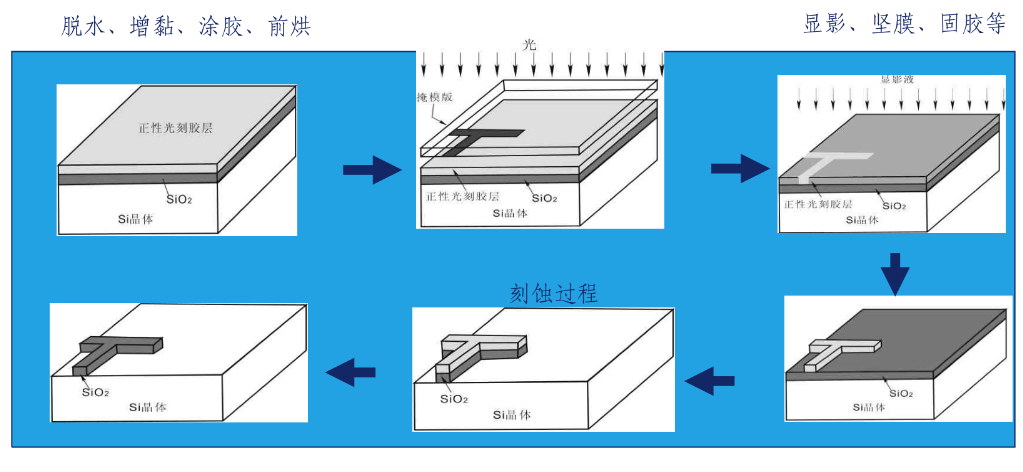

5、光刻工艺

扫码关注

扫码关注