FPGA是当今数字系统设计的主要硬件平台,优点是完全由用户通过软件进行配置和编程,可以反复擦写,无需改变PCB电路板即可修改升级,极大地缩短了系统设计的周期,提高了实现的灵活性降低成本,因此极大地获得了硬件工程师的青睐。所以本文将重点分享FPGA的组成结构及模块功能。

FPGA全称为Field Programmable Gate Array,即现场可编程门阵列,是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物,是作为专用集成电路(ASIC)领域中的一种半定制电路而出现。

FPGA的组成结构及模块功能

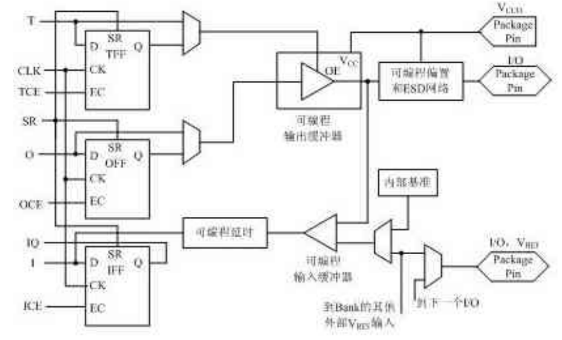

1、可编程输入输出单元(IOB)

可编程输入/输出单元简称I/O单元,是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配要求,其示意结构如图所示,FPGA的I/O按组分类,每组都能够独立地支持不同的I/O标准。通过软件的灵活配置,可适配不同的电气标准与I/O物理特性,可调整驱动电流的大小,可以改变上下拉电阻。目前I/O口频率越来越高,一些高端的FPGA通过DDR寄存器技术可支持高达2Gbps的数据速率。

2、可配置逻辑块(CLB)

CLB是FPGA内的基本逻辑单元,CLB的实际数量和特性会依据器件的不同而不同,但每个CLB都包含一个可配置开关矩阵,次矩阵由4或6个输入、一些选型电路(多路复用器等)和触发器组成。开关矩阵是高度灵活的,可对其进行配置以便处理组合逻辑、移位寄存器或RAM。每个CLB模块不仅可用于实现组合逻辑、时序逻辑,还可配置分布式RAM和分布式ROM。

3、数字时钟管理模块(DCM)

业内大多数FPGA均提供数字时钟管理(赛灵思的全部FPGA产品均具有这种特性)。赛灵思公司推出最先进的FPGA提供数字时钟管理和相位环路锁定。相位环路锁定能够提供精确的时钟综合,且能够降低抖动,并实现过滤功能。

4、嵌入式块RAM(BRAM)

大多数FPGA都具有内嵌的块RAM,这大大拓展了FPGA的应用范围和灵活性。块RAM可被配置为单端RAM、双端口RAM、内容地址存储器(CAM)以及FIFO等常用存储结构。RAM、FIFO是比较普及的概念,在此就不冗述。CAM存储器在其内部的每个存储单元中都有一个比较逻辑,写入CAM中的数据会和内部的每一个数据进行比较,并返回与端口数据相同的所有数据的地址,因而在路由的地址交换器中有广泛的应用。除了块RAM,还可以将FPGA中的LUT灵活地配置成RAM、ROM和FIFO等结构。在实际应用中,芯片内部块RAM的数量也是选择芯片的一个重要因素。

5、丰富的布线资源

布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定了信号在连线上的驱动能力和传播速度。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。第一类是全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;第二类是长线资源,用以完成芯片Bank间的高速信号和第二全局时钟信号的布线;第三类是短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;第四类是分布式的布线资源,用于专有时钟、复位等控制信号线。

6、底层内嵌单元

内嵌功能模块主要指DDL、PLL、DSP等软处理核,现在越来越丰富的内嵌功能单元,使得单片FPGA成为了系统级的设计工具,使其具备了软硬件联合设计的能力,逐步向SOC平台过渡。

7、内嵌专用硬核

内嵌专用硬核是相对底层嵌入的软核而言的,指FPGA处理能力强大的硬核,等效于ASIC电路。为了提高FPGA性能,芯片生产商在芯片内部集成了一些专用的硬核。

扫码关注

扫码关注