随着时代快速发展,集成电路产业已成为各国各组织激烈厮杀的“必争兵家之地”,与集成电路相关的电子工程师也开始成为各国各组织必争的人才资源,这也促使很多人从事集成电路设计,今天我们来谈谈集成电路的设计方法。

集成电路的设计方法具体如下:

1、全制定设计方法(Full-Custom Design Approach)

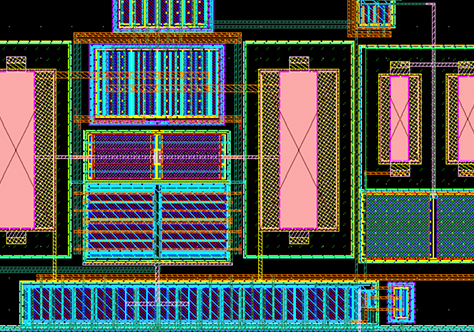

特点:完全是由用户工程师根据所选定的生产工艺来独立的进行集成电路产品设计。

优点:得到最高速度、最低功耗和醉生面积的芯片设计;

缺点:花费大量的人力、物力和时间。

需要注意的是,全制定设计方法是模拟集成电路常用的设计方法。

2、半定制设计方法(Semi-Custom Design Approach)

是基于制造商预先准备好母片上的设计。

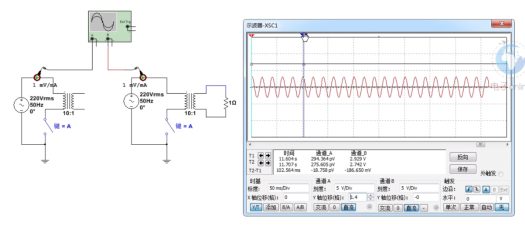

①门阵列设计法

特点:形状和尺寸相同的单元排成阵列固定高度的布线通道;

优点:设计周期大大缩短,设计成本大大下降;

缺点:灵活性低、门利用率不高、易造成芯片面积的浪费。

②门海定制方法

特点:基本的单元(不共栅的P管和N管)铺满整个芯片(除I/O区外);基本单元之间无氧化隔离区;布线通道不固定;

优点:相对于门阵列法,门利用率高、集成密度大、布线灵活、布通率高;

缺点:面积浪费、门利用率不高。

③标准单元设计法

特点:基本单元调用法,各个单元具有同一高度的版图尺寸,但宽度不等。

优点:

相比门阵列法,芯片的利用率高,也能保证100%的连续步通率、也可获得较佳的电路性能,可与全定制设计法相结合,在芯片内放入宏单元和功能块。

缺点:原始投资大,成本较高。

④积木块设计方法

也是通用单元设计法。

特点:相对于比较标准单元,不要求单元等高和等宽,每个单元可根据最合理的情况单独进行版图设计。且布线通道不统一,根据需要加以分配,积木块单元通常是较大规模的功能模块。

优点:灵活性大;

缺点:自动布线较困难。

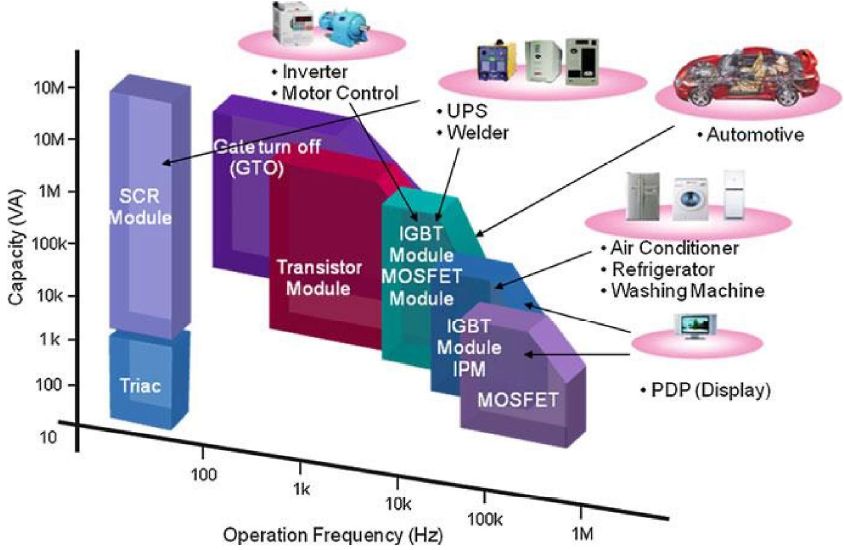

⑤可编程逻辑器件设计方法(PLD)

PLD的分类:简单PLD和复杂PLD

简单PLD的分类:

可编程只读存储器(PROM)

可编程逻辑阵列(PLA)

可编程阵列逻辑(PAL)

通用可编程阵列逻辑(GAL)

大容量PLD的分类:

复杂可编程逻辑器件(CPLD)

现场可编程门阵列(FPGA)

0

0

收藏

微博

微信

复制链接

0

评论 0 收藏

侵权举报

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

您需要登录后才可以评论登录

扫码关注

扫码关注