以 Micron公司容量为512Mb(512兆位),规格为8M×16×4的某款 SDRAM为例,介绍 SDRAM的引脚定义。

(1) CLK:时钟信号,为输入信号。 SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。

(2) (2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有两个,其是关闭时钟以进入省电模式,其二是进入自刷新( SELF REFRESH)状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。在电路设计中需注意,应为CKE信号提供可靠的驱动源,如果在设计中无需CKE所提供的功能,应将CKE信号上拉为高电平。

(3) CS#:片选信号,为输入信号,低电平有效。仅当CS#有效后, SDRAM才能识别存储器控制器发送来的命令。设计中,CS#信号应上拉。

(4) RAS#:行地址选通信号,为输入信号,低电平有效。

(5) CAS#:列地址选通信号,为输入信号,低电平有效。

(6) WE#:写使能信号,为输入信号,低电平有效。

(7) BA[1:0]:BANK地址信号,为输入信号。

(8) A[12:0]地址信号,为输入信号。

(9) DQ[15:0]数据信号,为输入输出双向信号

(10) DQML/DQMH:简写为DQM,是数据掩码信号,为输入输出双向信号,其方向与数据总线的方向相同,高电平有效。当DQM有效时,数据总线上出现的对应数据字节被接收端屏蔽。例如,某位宽为16位的 SDRAM,数据总线分为两个字节:DQ[7:0]和DQ[15:8],DQML对应于DQ[7:0],DQMH对应于DQ[15:8],在读操作时,假设DQML高电平而DQMH为低电平,则存储器控制器将忽略 SDRAM发出的DQ[7:0,]只存儒DQ[15:8]信号线所携带的数据。DQM信号主要用于 SDRAM的突发( Burst)操作,连续发送若干字节的数据,当发送方不希望其中的某些字节被接收方接收时,可使用DQM信号以屏蔽这些字节。设计中需注意,若无需DQM所提供的功能,应将DQM下拉到GND。

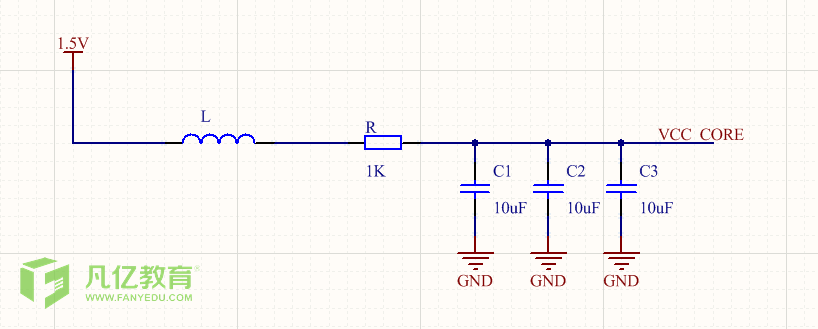

(11) VDD: SDRAM内核工作电源,为3.3V。

(12)VDDQ: SDRAM数据总线I/O口电源,为33V。为VDDQ与VDD分开供电,有利于抗干扰,但为简化电路设计,一般还是采用同一个电源为VDDQ与VDD供电。

扫码关注

扫码关注