一、嵌入式硬件电路设计概述

随着物联网、人工智能技术的发展,我们的生活越来越智能化,信息化。智能手机,智能手环,智能锁,智能冰箱,自动驾驶,机器人等智能产品层出不穷,人类即将进入智能时代。我们的产品,设备要实现智能化,其中用到的最核心技术及嵌入式技术。

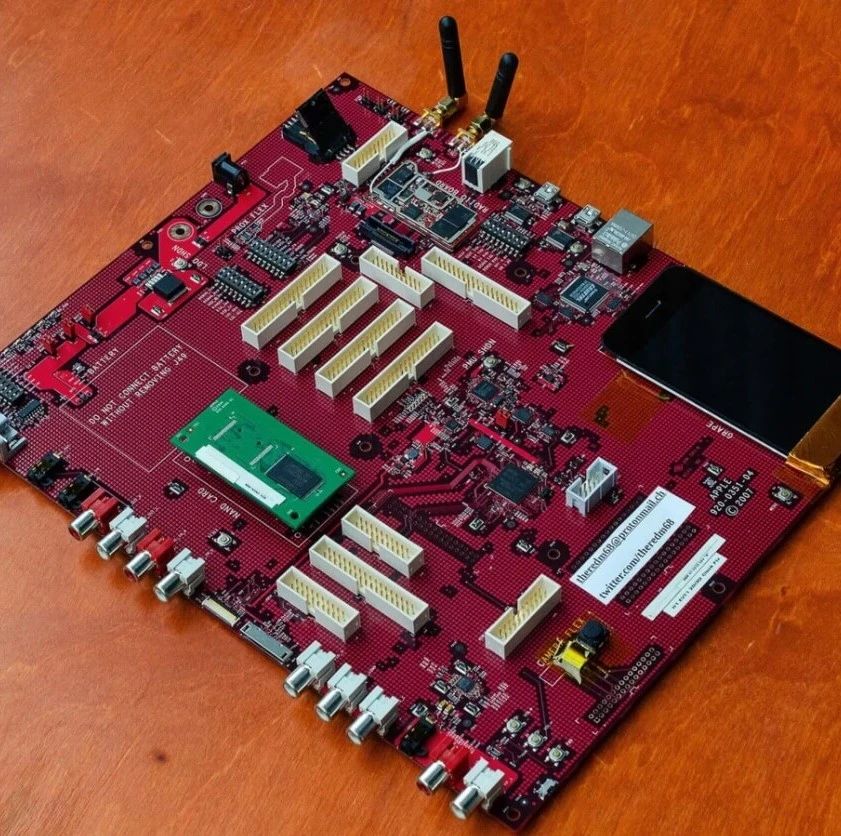

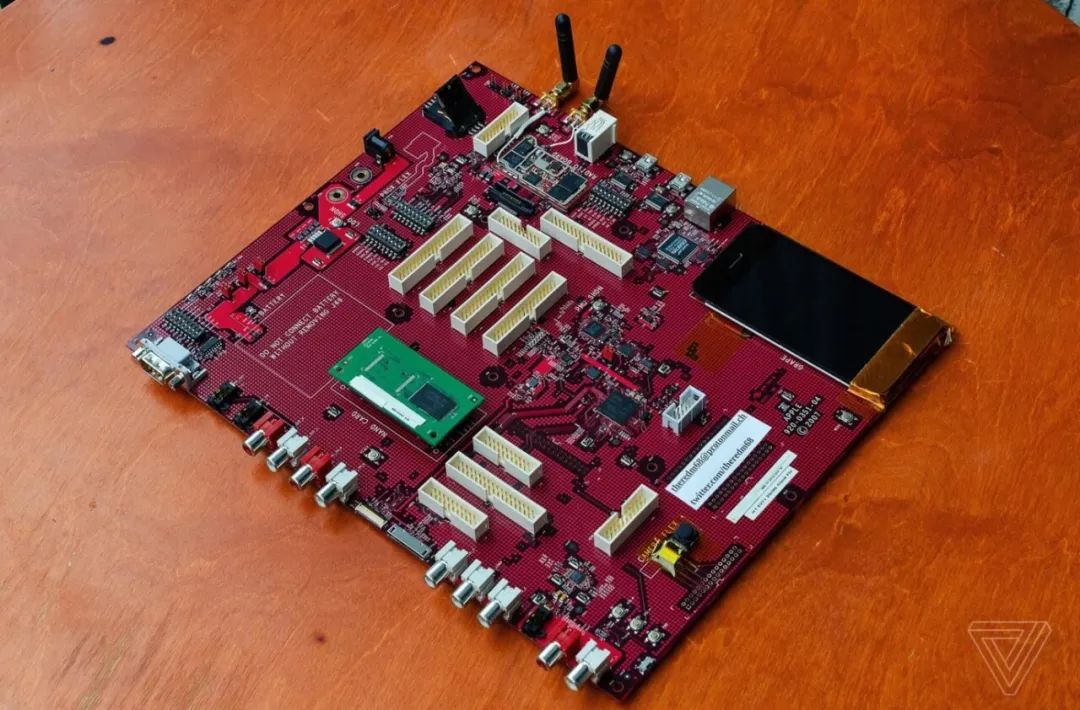

嵌入式技术是软件、硬件相结合一门学科,包括嵌入式软件和嵌入式硬件,嵌入式软件和硬件构成智能产品最核心的部分,嵌入式硬件相当于产品的躯壳,它依靠嵌入式软件而工作,在嵌入式软件的控制下完成产品相应的功能,是嵌入式软件的载体;嵌入式软件相当于产品的大脑,是产品的灵魂,没有了嵌入式软件,硬件就是一堆废铜烂铁,无法工作;同样,没有了嵌入式硬件,嵌入式软件将无所依附。所以说嵌入式硬件和软件同等重要,两者相辅相成,缺一不可。

随着集成电路的发展,嵌入式硬件的功能设计相对来说比较简单,大多数情况下只需要根据芯片厂家提供的参考电路设计即可,嵌入式硬件设计的核心越来越偏向可靠性设计,电磁辐射,电磁兼容设计。接下来,我将以设计蓝牙模块开发板为例来讲解嵌入式硬件电路设计中的注意事项。

二、蓝牙技术及蓝牙芯片CC2640

“蓝牙”技术属于一种短距离、低成本、低功耗的无线连接技术,是一种能够实现语音和数据无线传输的开放性方案,采用2.4GHz的ISM (即工业、科学、医学)频段,其传输速率最高为每秒1Mb/s,以时分方式进行全双工通信,蓝牙收发器的一般有效通信范围为10米,配置功率放大器可以使通信距离达到100米左右。正如爱立信蓝牙组负责人所说,设计蓝牙的最初想法是“结束线缆噩梦”。

CC2640 器件是一款无线微控制器 (MCU),主要适用于 Bluetooth?低功耗 应用。此器件属于 SimpleLink? CC26xx 系列中的经济高效型超低功耗 2.4GHz RF 器件。它具有极低的有源 RF 和 MCU 电流以及低功耗模式流耗,可确保卓越的电池使用寿命,适合小型纽扣电池供电以及在能源采集型应用中使用.

CC2640 包含一个Cortex-M3内核,工作主频48MHZ,128K Flash,28K SRAM ,4个定时器,15个GPIO,串口,I2C,12位ADC等常用外设一应俱全,硬件资源非常丰富,完全满足日常无线应用。

三、蓝牙芯片CC2640硬件电路设计注意事项

设计以MCU为核心的嵌入式系统硬件电路需要根据需求分析进行综合考虑,需要考虑的问题较多,这里给出几个特别要注意的问题.

1. MCU选择

选择 MCU 时要考虑 MCU 所能够完成的功能、MCU 的价格、功耗、供电电压、I/O 口电平、管脚数目以及 MCU 的封装等因素。MCU 的功耗可以从其电气性能参数中查到。供电电压有 5V、3.3V 以及 1.8V 超低电压供电模式。为了能合理分配 MCU 的I/O资源,在 MCU 选型时可绘制一张引脚分配表,供以后的设计使用。

2. 电源电路设计

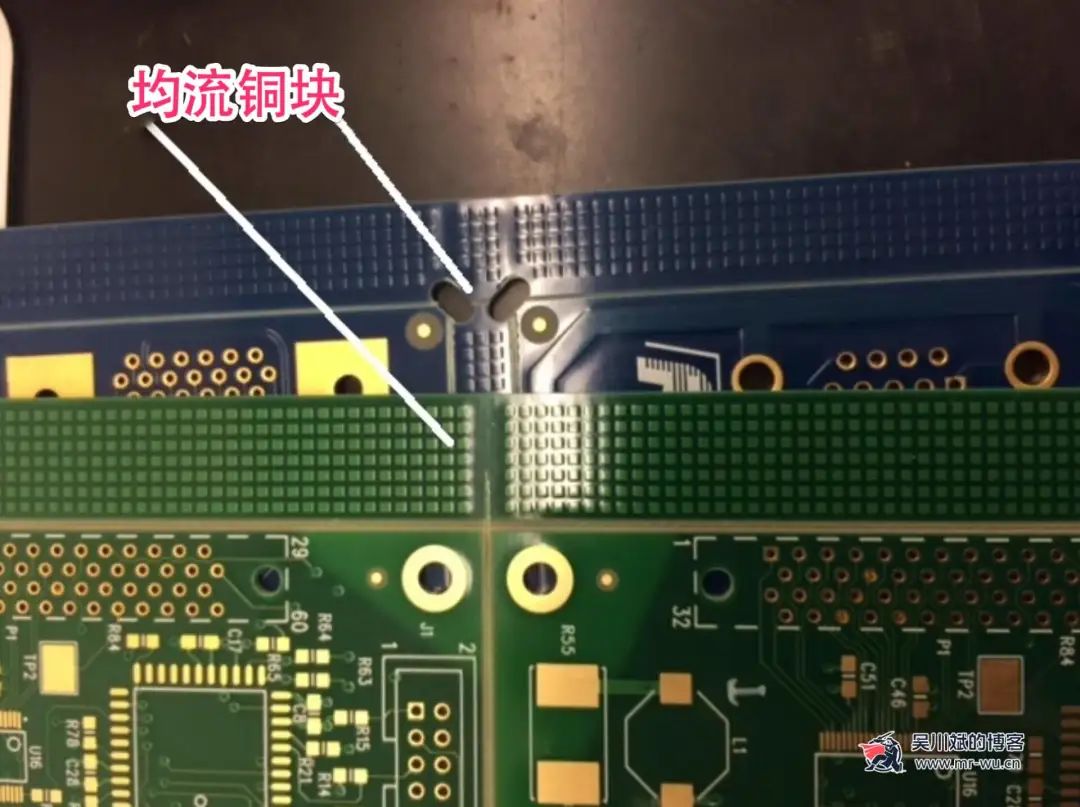

(1)考虑系统对电源的需求,例如系统需要几种电源,如24V、12V、5V或者3.3V等,估计各需要多少功率或最大电流(mA)。在计算电源总功率时要考虑一定的余量,可按公式“电源总功率=2×器件总功率”来计算。

(2)考虑芯片与器件对电源波动性的需求。一般允许电源波动幅度在 ±5% 以内。对于A/D转换芯片的参考电压一般要求 ±1% 以内。

(3)考虑工作电源是使用电源模块还是使用外接电源。

在这里我们使用低压差,低噪声,超快速线性稳压器RT9013给蓝牙无线模块供电.

CC2640的发送工作电流为10 mA左右,RT9013输出电流可以达到 500mA, 完全满足CC2640对工作电源的要求。

3. 普通IO口电路设计

(1)上拉、下拉电阻:考虑用内部或者外部上/下拉电阻,内部上/下拉阻值一般在 700ω 左右,低功耗模式不宜使用。外部上/下拉电阻根据需要可选 10Kω~1Mω 之间。

(2)开关量输入:一定要保证高低电压分明。理想情况下高电平就是电源电压,低电平就是地的电平。如果外部电路无法正确区分高低电平,但高低仍有较大压差,可考虑用 A/D 采集的方式设计处理。对分压方式中的采样点,要考虑分压电阻的选择,使该点通过采样端口的电流不小于采样最小输入电流,否则无法进行采样。

(3)开关量输出:基本原则是保证输出高电平接近电源电压,低电平接近地电平。I/O 口的吸纳电流一般大于放出电流。对小功率元器件控制最好是采用低电平控制的方式。一般情况下,若负载要求小于10mA,则可用芯片引脚直接控制;电流在 10~100mA 时可用三极管控制,在 100mA~1A 时用 IC 控制;更大的电流则适合用继电器控制,同时建议使用光电隔离芯片。

这里我们将开发板的的I/O口全部引出来,方便用户进行二次开发和测试验证。

4. A/D电路与D/A电路

(1)A/D电路:要清楚前端采样基本原理,对电阻型、电流型和电压型传感器采用不同的采集电路。如果采集的信号微弱,还要考虑如何进行信号放大。

(2)D/A电路:考虑 MCU 的引脚通过何种输出电路控制实际对象。

5.控制电路

对外控制电路要注意设计的冗余与反测,要有合适的信号隔离措施等。在评估设计的布板时,一定要在构件的输入输出端引出检测孔,以方便排查错误时测量。

6.考虑低功耗

低功耗设计并不仅仅是为了省电,更多的好处在于降低了电源模块及散热系统的成本。由于电流的减小也减少了电磁辐射和热噪声的干扰。随着设备温度的降低,器件寿命则相应延长,要做到低功耗一般需要注意以下几点:

(1)并不是所有的总线信号都要上拉。上下拉电阻也有功耗问题需要考虑。上下拉电阻拉一个单纯的输入信号,电流也就几十微安以下。但拉一个被驱动了的信号,其电流将达毫安级。所以需要考虑上下拉电阻对系统总功耗的影响。

(2)不用的I/O口不要悬空,如果悬空的话,受外界的一点点干扰就可能成为反复振荡的输入信号,而MOS器件的功耗基本取决于门电路的翻转次数。

(3)对一些外围小芯片的功耗也需要考虑。对于内部不太复杂的芯片功耗是很难确定的,它主要由引脚上的电流确定。例如有的芯片引脚在没有负载时,耗电大概不到1毫安,但负载增大以后,可能功耗很大。

7.考虑低成本

(1)正确选择电阻值与电容值。比如一个上拉电阻,可以使用4.5K-5.3K的电阻,你觉得就选个整数5K,事实上市场上不存在5K的阻值,最接近的是4.99K(精度1%),其次是5.1K(精度5%),其成本分别比精度为20%的4.7K高4倍和2倍。20%精度的电阻阻值只有1、1.5、2.2、3.3、4.7、6.8几个类别(含10的整数倍);类似地,20%精度的电容也只有以上几种值,如果选了其它的值就必须使用更高的精度,成本就翻了几倍,却不能带来任何好处。

(2)不要什么都选最好的。在一个高速系统中并不是每一部分都工作在高速状态,而器件速度每提高一个等级,价格差不多要翻倍,另外还给信号完整性问题带来极大的负面影响.

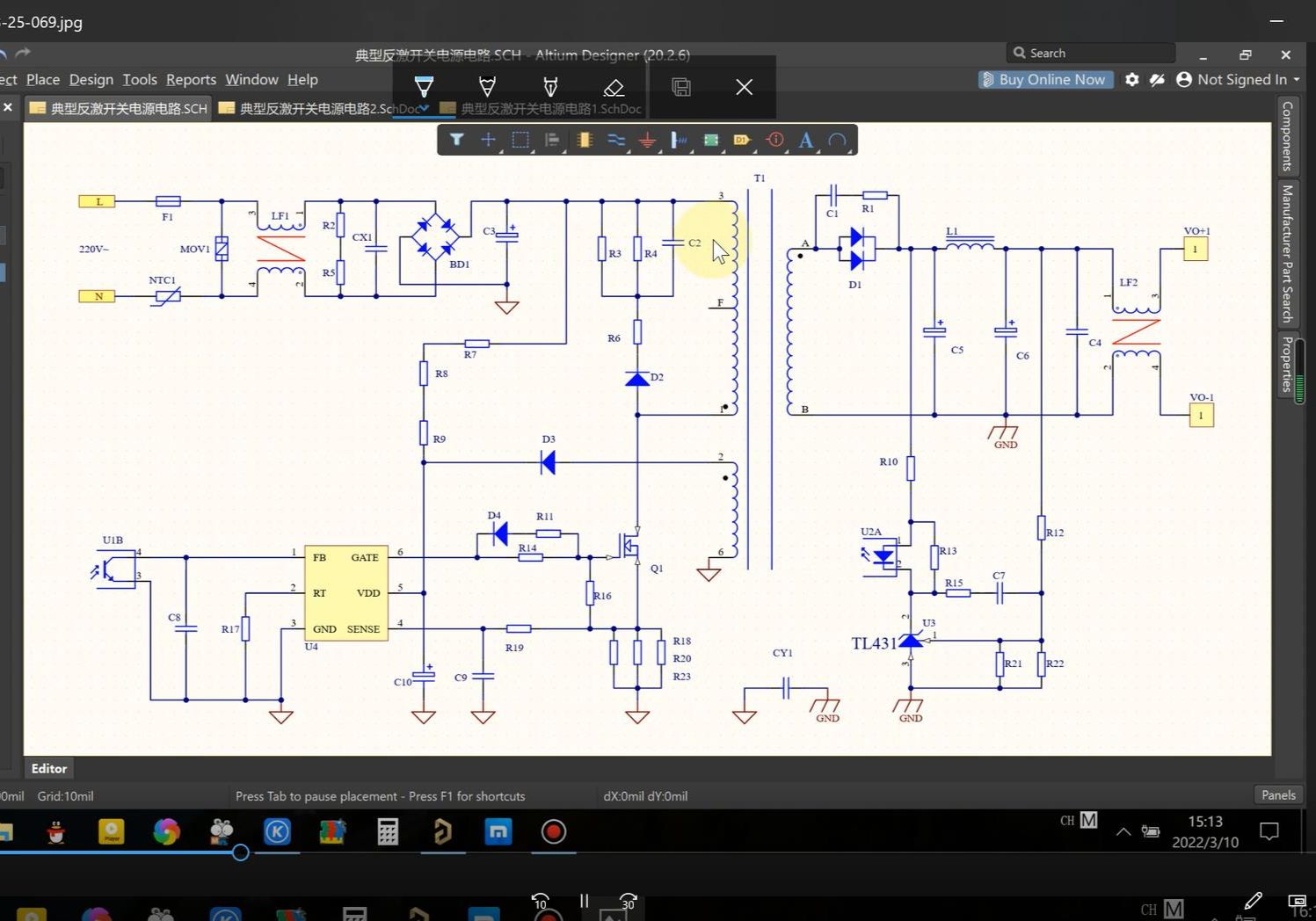

作为嵌入式工程师,既要懂的嵌入式软件设计,也要懂的硬件设计,至少能看懂硬件原理图,能够理解硬件的工作原理,这样我们才能更好的编写高效的嵌入式软件,再调试产品,解决设备故障时,就能够从软,硬件的角度来分析问题和解决问题。 以上就是我这次要和大家分享的关于嵌入式硬件设计的注意事项,希望对同学们有所帮助。

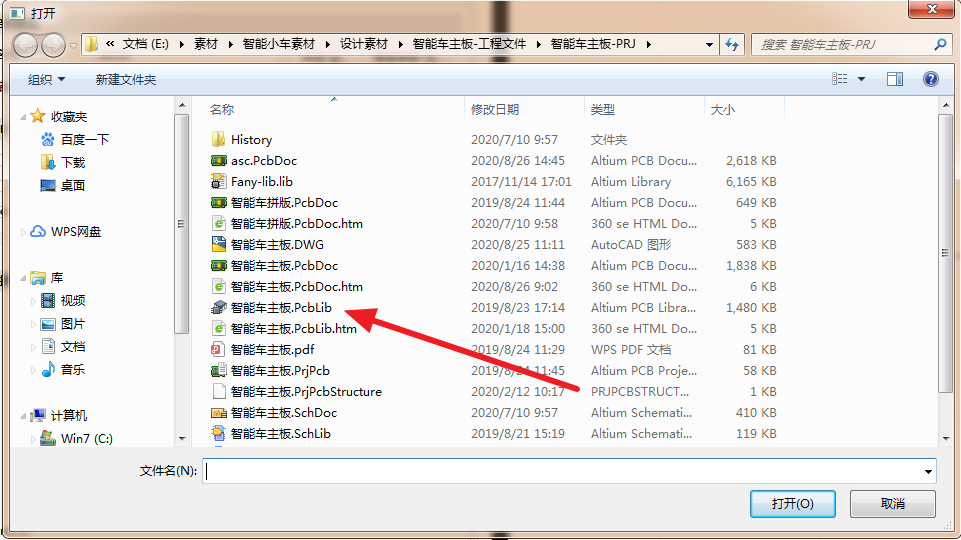

如果大家对嵌入式硬件设计不是特别理解,可以来凡亿教育课堂具体了解。

扫码关注

扫码关注