PCB培训时,会遇到各种各样的问题,下面小编给大家讲解一下PCB绘图技巧,希望对大家有帮助。

PCB绘图时,使用ERC出现“MultipleNetIdentifiers”错误提示:

解决办法:可能是由于不同的网络标号连在了一起,或同一根连线上给了不同的网络标号。

如果为单张原理图,在图上查找带有错误标号的位置即可;为多张原理图时,要查找所有图;尤其是多层原理图时,很有可能错误是在子图中。

1.原理图常见错误:

(1)ERC报告管脚没有接入信号。

a.创建封装时给管脚定义了I/O属性。譬如,把输入端口和输出端口连在一起就会报错。其实,若不用protel做电路仿真,就无需对管脚的I/O属性进行定义。

b.建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上。

c.建元件时pin方向反向,必须非pinname端连线。

(2)ERC报告重复的网络标号(Error:MultipleNetIdentifiers)。

可能是由于不同的网络标号连在了一起,或同一根连线上给了不同的网络标号。需要注意的是,PROTEL指出的错误处不一定是真正的错误处,也可能错在其他的原理图上(若是层次电路图时)

(3)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(4)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(5)当使用自己创建的多部分组成的元件时a,千万不要使用annotate。

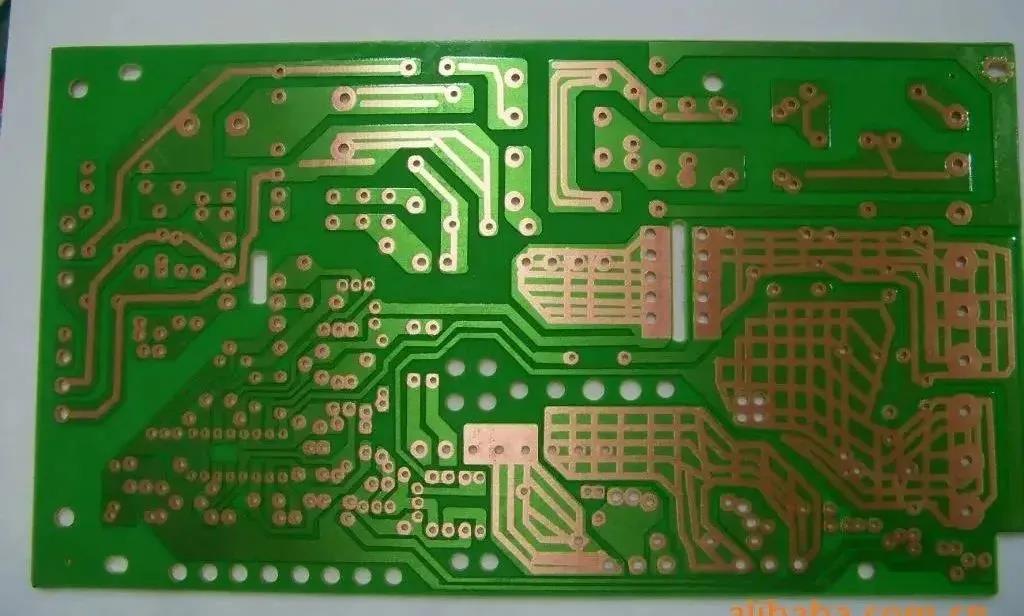

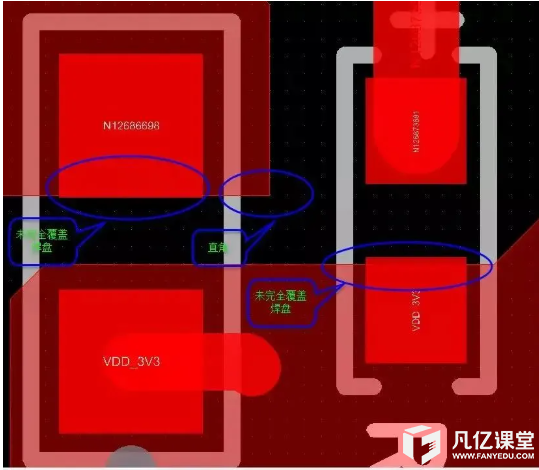

2.PCB中常见错误:

(1)网络载入时报告NODE或FootPrint没有找到。

a.在装载网络表时,事先没有加载对应的PCB封装库。

b.原理图中的元件使用了pcb库中没有的封装。

c.原理图中的元件使用了pcb库中名称不一致的封装。

d.原理图中的元件使用了pcb库中pinnumber不一致的封装。如三极管:sch中pinnumber为e,b,c,而pcb中为1,2,3;二极管:sch中pinnumber为a,k,而pcb中为1,2,改成一致就可以了。

(2)在PCB中导入元器件后,发现个别器件不在显示屏范围内,即时缩小图纸显示比例,也看不到,这往往是因为在创建PCB元器件封装时没有设定参考点所致,一般地,“set

reffrence”到“pin1”即可。

3.复制局部ProtelSch原理图,想把它贴到Word里方法如下(针对protel99,proteldxp应可以类比,未试过):

tools-preferences-graphicalediting:addtemplatetoclipboard的选项,去掉它就可以了。

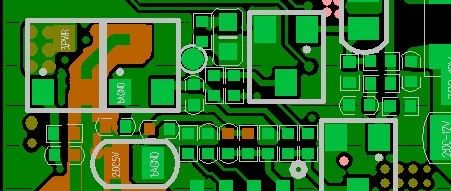

4.关于走线宽度

系统默认走线为10mil,一般可以设到8mil,再细的话(如低于6mil),一般性的小电路板厂家就不能制造了,找大厂做成本就高,具体情况具体衡量。注:100mil(英制)=2.54mm(公制)

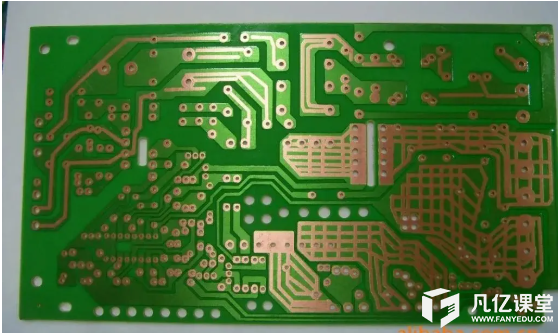

在进行pcb培训后,我们的就业地点可以自己选择,但是一般深圳、长沙、上海、广州等地的薪资水平或许比较高一点,推荐大家去那边。如果大家对于PCB培训有地点有要求的话,凡亿教育在深圳、长沙各地都可以进行pcb培训哦。凡亿教育致力于pcb行业发展,为pcb行业输送人才。

扫码关注

扫码关注

![Cadence17.4 GD32 ARM高速电路PCB硬件设计实战[第三部]](https://api.fanyedu.com/public/uploads/image/course/20200519/55b5b9f147397aa1097829400b322791.jpg)