异构集成 (Heterogeneous integration,HI) 和系统级芯片 (System on Chip,SoC) 是设计和构建硅芯片的两种方式。异构集成的目的是使用先进封装技术,通过模块化方法来应对 SoC 设计日益增长的成本和复杂性。

在过去的 20 年里,Cadence 一直支持电子行业以SoC方式帮助我们的客户追求更大的晶体管密度并不断突破摩尔定律的界限,一直到 2nm 甚至 1nm 制程节点时,我们也在持续致力于帮助他们顺利实现设计。现在,异构集成提供了一种具有成本效益的替代方案,并用事实证明,对于许多应用来说可能比单片SoC更为适合。

那么,我们来看看这两种设计工艺之间的区别以及各自的优势和注意事项。

1

系统级芯片 (SoC)

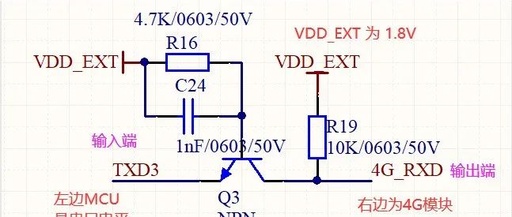

SoC 是一种集成电路 (IC),将计算系统的每个部分都整合到一个硅晶粒中。其中包括一个或多个中央处理单元 (CPU) 或处理器(低功率微控制器和/或应用处理器),每个都带有几个核心,以及图形处理单元 (GPU)、Wi-Fi、蓝牙或 4G/5G 蜂窝调制解调器、存储器,甚至可能还包括存储器等外围设备。

在过去 20 年里,SoC 的兴起和扩展是半导体技术中最具创新性和令人兴奋的变化之一。在过去,设计一个复杂的计算系统意味着使用离散的、现成的组件来设计一个系统。

由于 SoC 的所有部件都集成在一个晶粒上,SoC 在功率、性能和面积 (PPA) 方面提供了无与伦比的优化。它们的运行功率相对较小,能够非常迅速地执行计算功能,而且占用的物理空间也要小得多,这意味着最终设备的外形尺寸也可以更小。现在,全球数十亿台设备都依赖 SoC,从汽车到笔记本电脑,从智能手机到医疗器械。

但是,制造先进的单片 SoC,特别是如果采用最新的制程节点(7nm 及以下),成本变得越来越昂贵。自行业在 21 世纪前十年使用 FinFET技术以来,对于 28nm 以下的节点,每个晶体管的成本节节升高--有能力投资最新设计节点的少数代工厂也开始纷纷宣布涨价。

此外还要考虑项目和初期投入工程成本 (NRE, non-recurring engineering) 。为了实现某个 3nm 设计,可能需要一个由数千名工程师组成的设计团队工作数万小时,花费数亿美元,而这才仅仅完成了功能验证步骤。

如果要为面向大众市场的智能手机打造一款 SoC,那么这笔投资也许可以收回成本。但对于小众市场,例如国防/工业领域,市场需求只有 1000 件左右,再如此大费周折就有点得不尝失。

最后需要考虑物理限制。目前的 SoC 已经达到了光刻的极限:如果不采用昂贵的缝合技术,制造设备根本无法应对不断增长的芯片尺寸。随着芯片尺寸增加,缺陷风险也变得更高,导致晶圆的良率降低。

2

异构集成(HI)

异构集成为单片 SoC 提供了一种替代方案,对于复杂但成本预算有限的设计来说,异构集成已经成为一个非常有吸引力的选择。

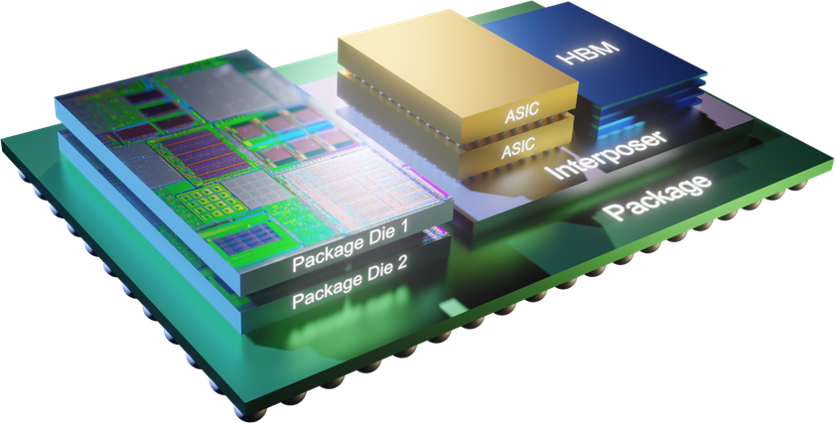

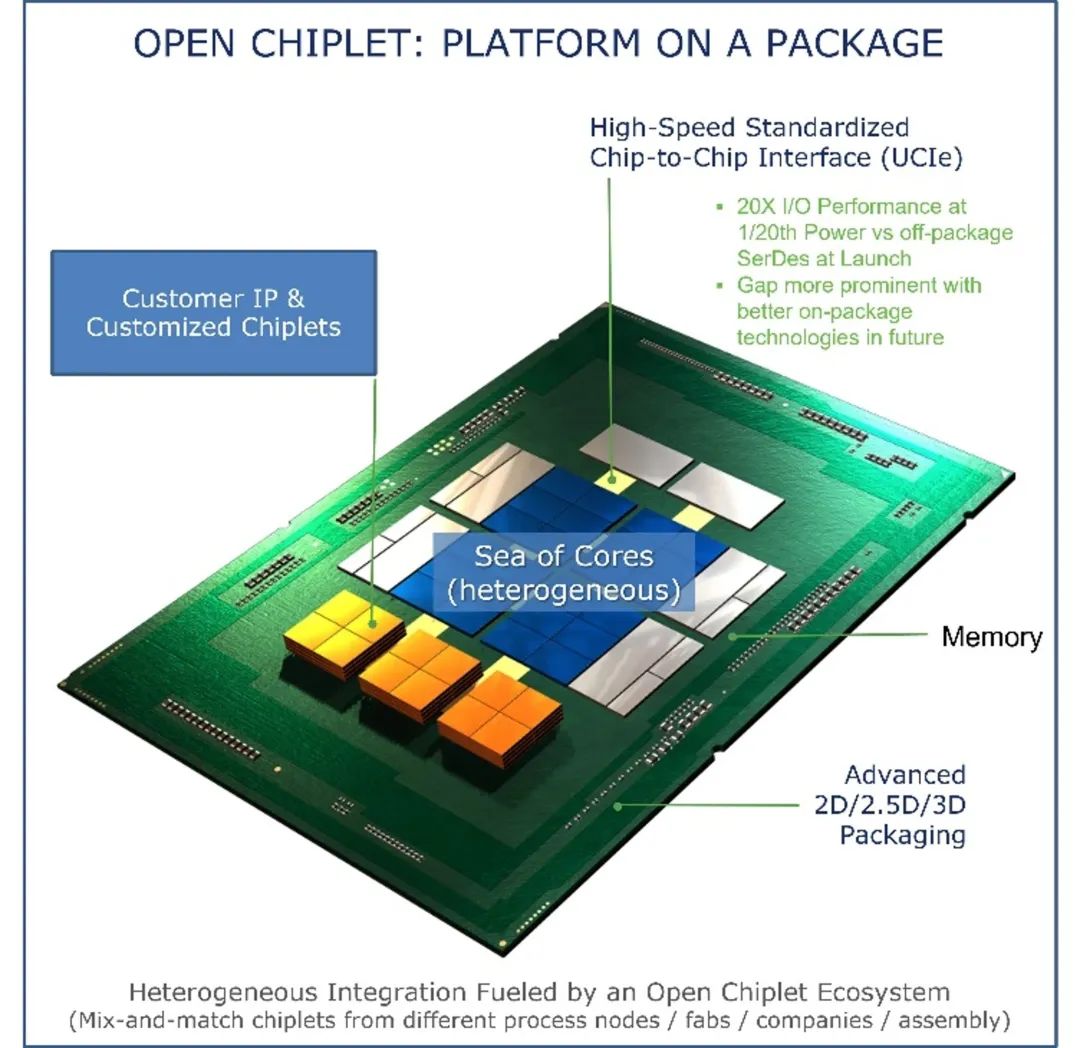

异构集成是指使用先进的封装技术,将较小的chiplet(芯粒/小晶片)整合到一个系统级封装 (System in Package,SiP) 中;chiplet是物理上经过实现和测试的 IP ,制成在芯片上并切割,可以执行特定的逻辑功能。

可以把 SoC 看作单片机,把异构集成看作模块化——整合来自不同芯片代工厂的不同 chiplets。每个 chiplet 都是单独制造的,并且远远低于光刻机可处理的极限尺寸,因此实际生产芯片的过程要简单得多。Chiplets 也可以针对任何制程节点进行组合设计;例如,异构集成有可能将 28nm 的 chiplets 与 2nm 的 chiplets 整合在一起。

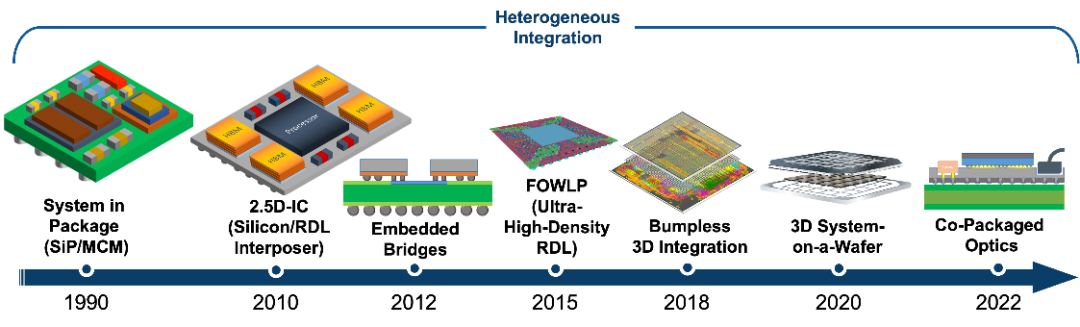

虽然先进异构集成仍处于发展的早期阶段,但在一个共同的基板(陶瓷、硅/玻璃或有机物)上并排集成不同的芯片和分立元件并不是什么新概念。多芯片模块 (multichip module,MCM) 和 SiP 等技术已经问世了几十年,每种技术都有各种不同的应用场景。

异构集成将 SiP 设计向前推进了一大步,将其与 2.5D/3D-IC、扇出型芯片级封装 (FOWLP)、硅和玻璃中介层以及嵌入式桥接器等尖端封装和互连技术相结合。

异构集成还能为 HPC 和服务器市场等应用提供更大、更强大的芯片。在这些应用中,封装本身可以直接集成大量的内存;而这在 SoC 上是根本不可能实现的。

然而,异构集成也有一些注意事项。设计工作并没有因为有了异构集成而变得简单,反而变得更为复杂。从单一的单片 SoC 过渡到系统级架构,需要重新考虑原本 SoC 可以有效应对的不良因素,如热、电和机械性张力。在尝试设计异质集成芯片之前,采用正确的工具、方法和团队协作方式是至关重要的。

异构集成还意味着信号路径延长、I/O 数量增多和外形尺寸更大——这些都是不利于实现高效PPA的因子。异构集成设计的芯片,其形状参数在 X 和 Y 平面积上会变大,如果实施 3D 堆叠,甚至 Z 方向高度也会变大,而这是不可避免的。

而且异构集成中,chiplets 的封装方式对芯片的成功至关重要。这意味着在设计阶段需要格外关注封装技术,无论是 2.5D、3D-IC,还是其他的封装技术。

系统级芯片和异构集成——

如何为设计项目选择?

这个问题的答案在很大程度上取决于具体的应用、设计预算,以及预期出货片的总产品数量。随着越来越多的应用范例不断涌现,它们需要使用强大的人工智能 (AI) 和用在边缘计算并采用高性能计算 (HPC) 的自主系统,因此仅采用SoC 技术可能会达到其能力的物理极限。先进异构集成自然而然地成为了下一步的选择。

然而,总会有很多应用在 PPA 方面无法达成妥协,在这种情况下,SoC 将仍然是最佳选择。

3D-IC 有望在网络、图形、AI/ML 和高性能计算等领域产生广泛影响,特别是对于需要超高性能、低功耗器件的应用而言。具体的应用领域包括多核 CPUs、GPUs、数据包缓冲器/路由器、智能手机和 AI/ML 应用。

从设计的角度来看,要实现真正的 3D 集成,需要对某些设计工具进行一些加强。尤其在架构分析、热分析、多裸片间的排置、时序、测试和验证方面的功能都需要提升。此外,还需要新的系统级功能,如顶层规划和优化、芯片裸片(die)之间和晶粒(chiplet)之间的信号完整性和 IC/封装协同设计。

扫码关注

扫码关注