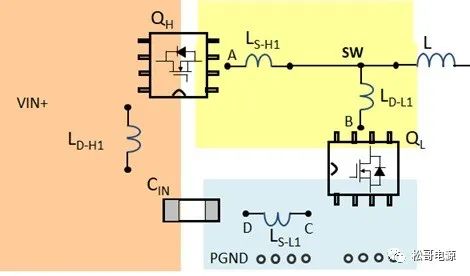

上篇《DCDC的Layout终极奥义》中,我举的BUCK的例子,给出了我自己的布局走线方式。

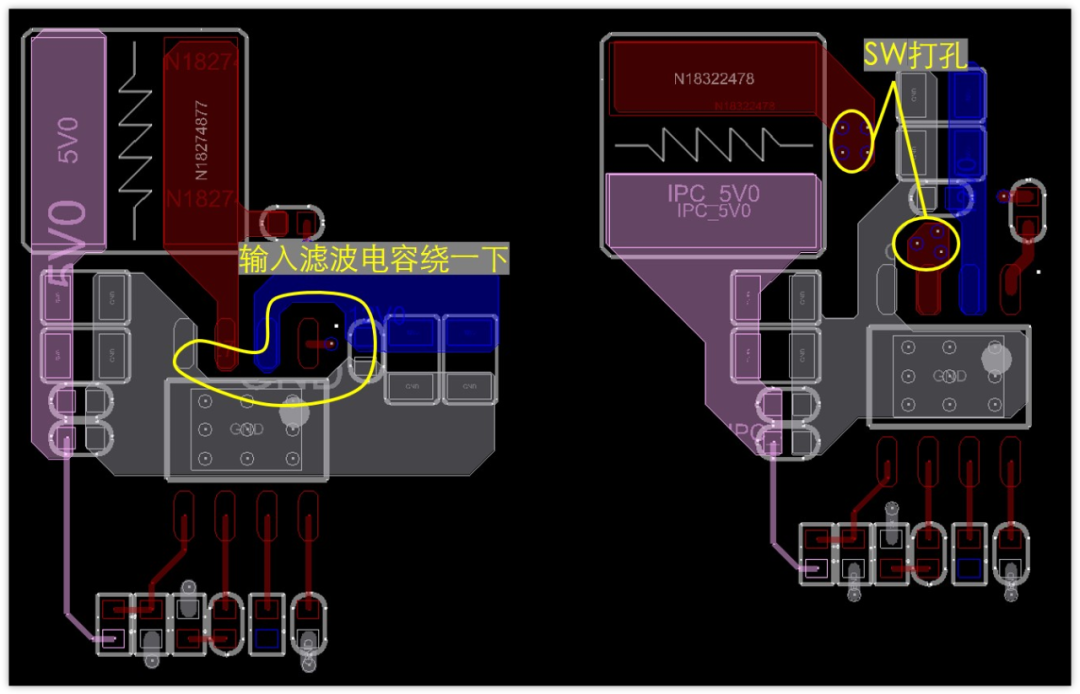

然后有两位兄弟留言说,他们会将Buck输入滤波电容按照最近的方式放置,开关节点SW打孔走出去,也就是下面这两种方式的右边那种。

这两种方式最大的区别就是SW的处理不一样,我之前也有想过,不过我无法确定哪种方式更好,因为各有优劣势,我不是很清楚影响有多大。

下面说下我的一些想法。

关于要让Buck的输入环路最小这一点,大家也都是同意的,问题就在于要不要做到极致?

留言的两位兄弟倾向于做到极致,那么就是输入滤波电容直接跨接到Vin和GND上,然后开关节点SW打孔换层,然后再打孔回来。这样的好处是做到了输入环路最小了,坏处是顶层SW打孔换层,然后再打孔换回顶层。

那么SW到底要不要打孔呢?或者能不能打孔呢?

首先我们要明白为什么有这个问题存在?或者说考虑了哪些方面才会觉得SW打孔不好?

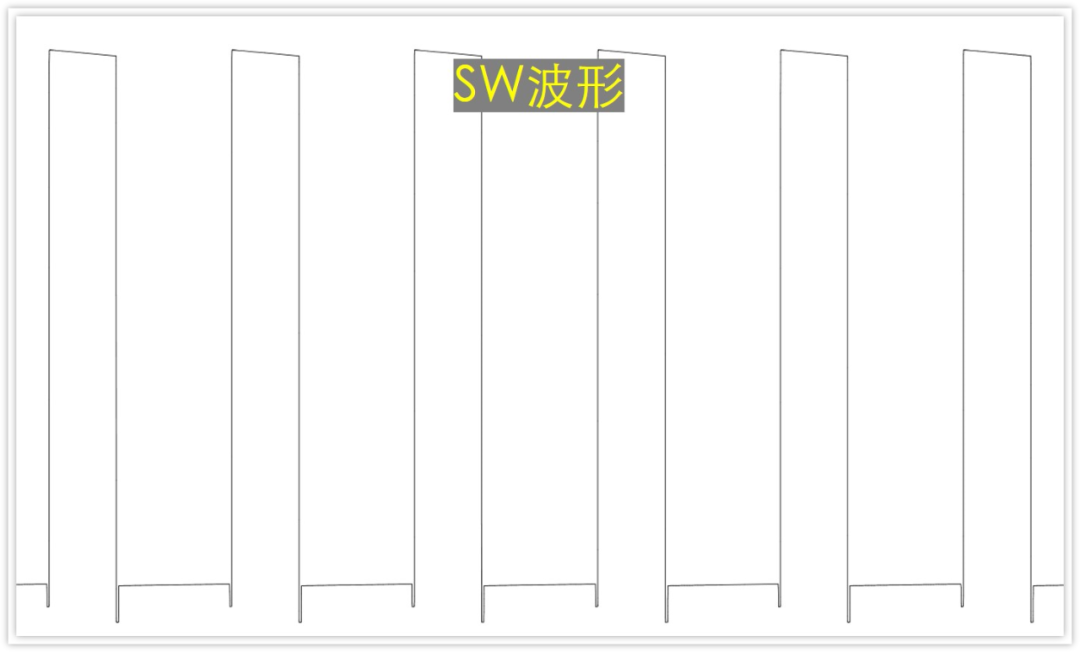

它存在的原因,是因为开关节点SW的电压是矩形波,在开关切换的时候,dV/dt很大,有很多的高频谐波分量,所以容易引起EMI问题。

但是如何引起EMI问题,我一直是不太明白。

怎么说呢?关于EMI,我们估计都有听说这么一句话:

dI/dt或者dV/dt很大的时候,会意味着存在很多的高频分量,很容易引起EMI问题。

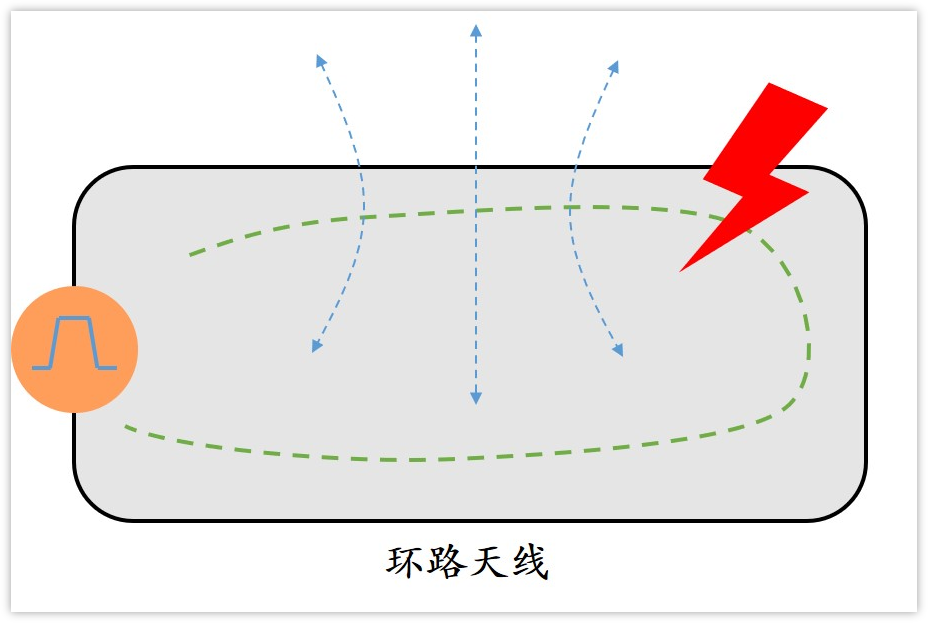

dI/dt很大导致EMI问题,这个相对来说好理解一点。电流会产生磁场,那么在这个环内产生的磁场会随电流变化而变化,dI/dt越大,那么环内的磁场也会剧烈变化,磁生电,电生磁,就形成电磁辐射了,这个辐射也叫做差模辐射,这种无意中形成的环形的辐射装置可以看成是环路天线。

我前面说我不太明白,就是我无法像电流环辐射那样,让dV/dt在脑子里面构成一幅辐射的图景。

不过就在上次我发了文章之后,也有一个兄弟在留言区推荐了MPS的一个视频。名称叫“MPS汽车电子中DCDC芯片的EMI设计”。

B站网址是这个(清晰度更高):

https://www.bilibili.com/video/BV1k64y1D76C

MPS官网也有(可以下载课件):

https://www.monolithicpower.cn/cn/support/videos/webinar-20200320-dcdc-emi.html

视频确实很不错,举了很多例子,兄弟们可以看看。

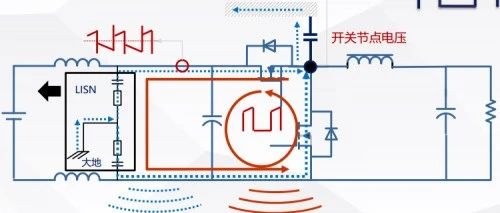

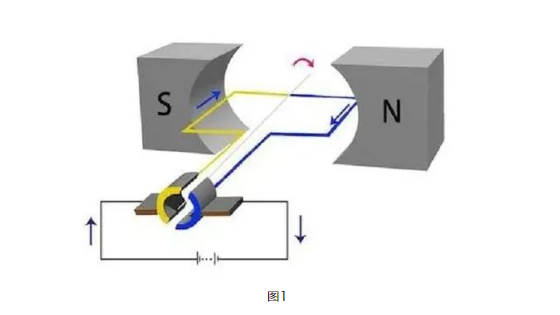

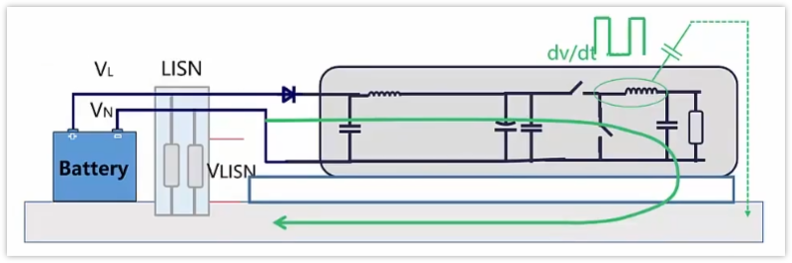

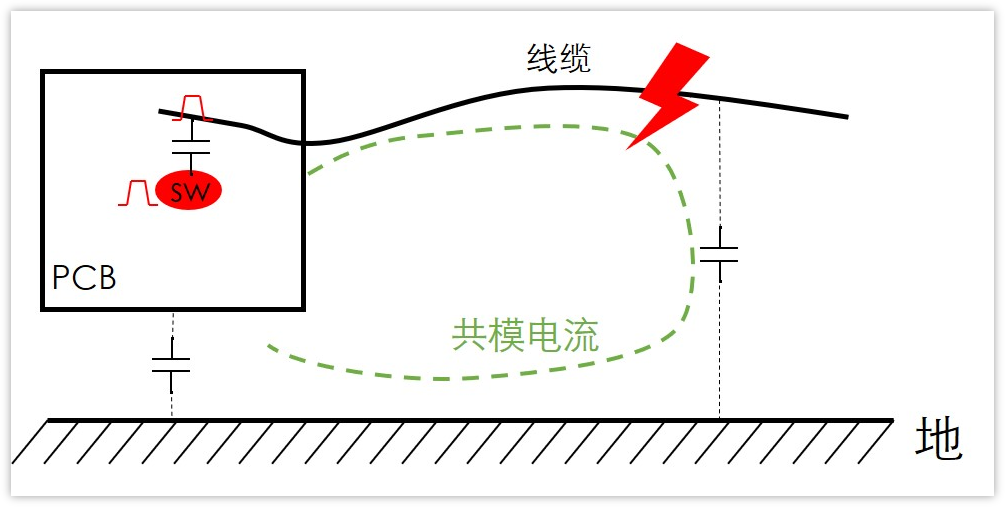

视频里面有下面这一张图:

这个图给了我启发:这个SW节点Layout一般是一块铜皮,与其它的导体(比如长的金属导体,或者是线缆—比如电源线)形成寄生电容,也就是说这个SW快速变化的电压会耦合到这些线材或是导体上面。

当然了,也会耦合到其它地方,只不过线缆一般比较长,是一个很好的天线,这种辐射一般叫共模辐射,最终它在我脑子里面大致是这样的。

这有什么用呢?

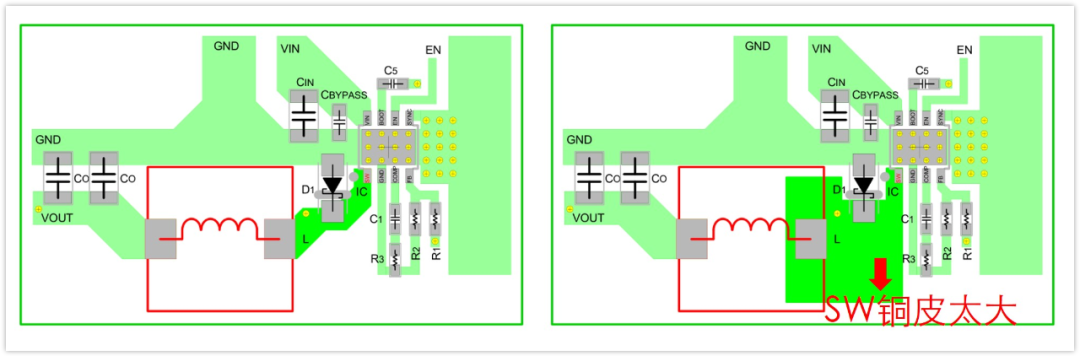

我们要减少辐射,那么就要减小SW的面积,这样SW与线缆之间的寄生电容就更小,耦合到线缆的噪声电压也就越小了,因此可以降低辐射。从这个角度来说,Layout我们尽量减小SW的面积。

当然,另一方面,SW节点也是要流过大电流的,过流能力是必须要保证的,走线不能太细。

总的来说,就是要减小不必要的SW的铜皮,比如下图,右边这个铺铜就不好。

回到SW打孔的问题,SW打孔走线,必然比直接连接电感有更大的面积,也就是会增加共模辐射的风险。

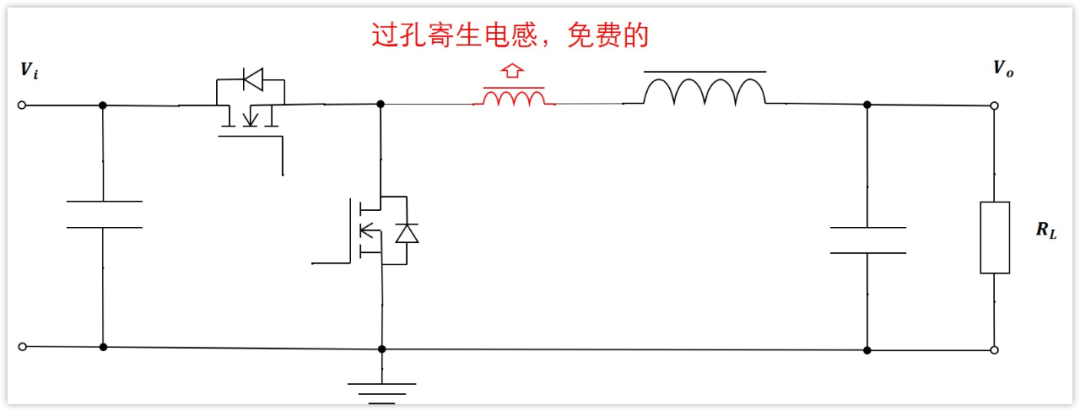

这里还有一点值得说明下,有人会认为:SW打过孔,会有寄生电感存在,这个不好。

其实这是没有关系的,很容易看出来,这个寄生电感是跟原本就有的功率电感是串联到一起的,那么这个过孔电感就可以合并到原来的功率电感里面,仅仅只是让原来的功率电感感量增大了一丢丢,这个自然没有什么影响。

或者用一个兄弟留言的话说:这个SW过孔就相当于是免费增大输出电感了。

总的来说,文章前面提到的2种Buck的Layout情况

SW不打孔,输入滤波电容稍微绕一下:输入环路没有做到最小,差模辐射会大些。

SW打孔,输入滤波电容最近:输入环路做到了最小,但是SW的面积必然会加大,共模辐射可能会大些。

至于具体用哪种,我觉得不用过多纠结,随便挑一个就行,本来就不一定超标,其它相关的注意事项注意了,一般也不会有问题。

以上就是我个人的理解,如果有不同意见或者是补充,可以留言指出。

推荐PCB-Gerber分析小工具

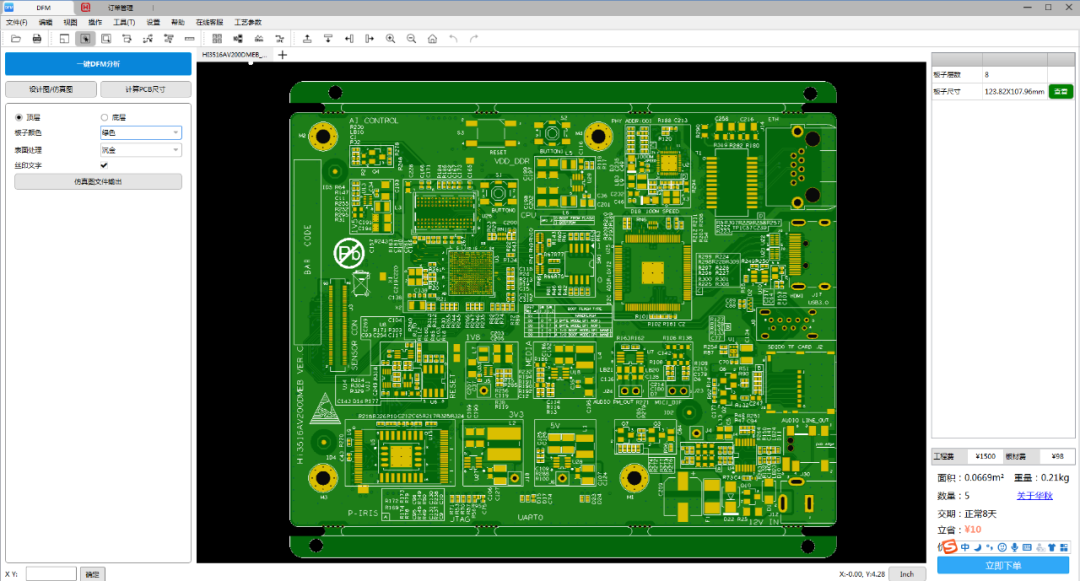

1、它可以模拟出实物的效果,下面展示下

2、它可以分析PCB板的缺陷:包括开短路,最小线宽,线距等等,还能准确定位到具体位置。

3、它可以直接导入PCB源文件,也可以导入Gerber文件进行分析,也就是说不用每次都导入Gerber文件进行分析。可以支持导入PCB源文件,包括Allegro,Pads,AD等常用软件。

4、可以一键导出Gerber文件,坐标文件,也可以导出丝印图pdf文件等等。

DFM工具(PC客户端)下载链接:

https://dfm.elecfans.com/uploads/software/promoter/hqdfm_ly0112.zip

最近这个软件也出了web版本,不想下载客户端的可以使用网页版(网页版体验一般,最好下载客户端版本)

网页版地址:

https://dfm.elecfans.com/viewer/

这个软件菜单都是中文的,基本上打开,看下菜单就会用吧。如果需要用到更多功能,这里有个视频教程:

链接:

https://pan.baidu.com/s/1MoEraza2P0mHnlVQmXCmrg

提取码:

0iq9

扫码关注

扫码关注