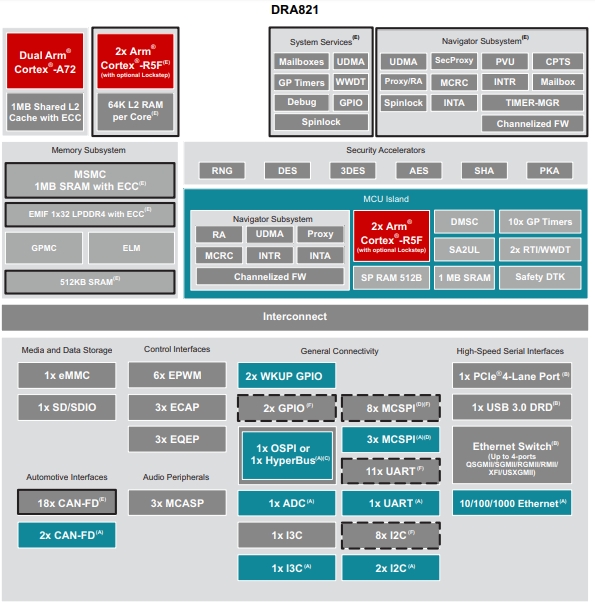

DRA821 Jacinto™ 处理器

1、说明

Jacinto™ DRA821x 处理器基于 Armv8 64 位架构,针对具有云连接能力的网关系统进行了优化。片上系统 (SoC) 设计可通过集成(尤其是系统 MCU、功能安全和安全性特性以及可实现高速通信的以太网交换机)降低系统级成 本和复杂性。集成式诊断和功能安全特性满足 ASIL-D 和 SIL-3 认证要求。实时控制和低延迟通信由 PCIe 控制器 和支持 TSN 的千兆位以太网交换机提供支持。

多达四种通用 Arm® Cortex®-R5F 子系统可以处理简单的时序关键型处理任务,从而使 Arm® Cortex®-A72 核心 不受高级应用和基于云的应用的影响。

功能安全:

• 以功能安全合规型为目标(在部分器件型号上)

– 专为功能安全应用开发

– 将提供使 ISO 26262 和 IEC 61508 功能安全系统设计满足 ASIL-D/SIL-3 要求的文档

– 系统功能符合 ASIL-D/SIL-3 要求

– 对于 MCU 域,硬件完整性符合 ASIL-D/SIL-3要求

– 对于 MAIN 域的扩展 MCU (EMCU) 部分,硬件完整性符合 ASIL-D/SIL-3 要求

– 对于 MAIN 域的其余部分,硬件完整性符合ASIL-B/SIL-2 要求

– 在 EMCU 和 MAIN 域的其余部分之间提供 FFI隔离

– 安全相关认证

• 计划 的 ISO 26262 和 IEC 61508 认证

• 符合 AEC-Q100 标准(以 Q1 结尾的器件型号)

2、器件选型

① DRA821U4TGBALMR 双核 Arm Cortex-A72、四核 Cortex-R5F、4 端口以太网交换机和 PCIe 控制器

架构:MCU,MPU

核心处理器:ARM® Cortex®-A72,ARM® Cortex®-R5F

I/O 数:141

闪存大小:-

RAM 大小:1.5MB

外设:DMA,PWM,WDT

连接能力:Ethernet, I2C, I3C, MCAN, MMC/SD/SDIO, SPI, UART, USB

速度:2GHz,1GHz

主要属性:-

工作温度:-40°C ~ 125°C(TJ)

封装/外壳:433-BFBGA,FCBGA

供应商器件封装:433-FCBGA(17.2x17.2)

② DRA821U2CGBALMR ARM® Cortex®-A72,ARM® Cortex®-R5F 处理器 IC 433FCBGA

架构:MCU,MPU

核心处理器:ARM® Cortex®-A72,ARM® Cortex®-R5F

I/O 数:141

闪存大小:-

RAM 大小:1.5MB

外设:DMA,PWM,WDT

连接能力:Ethernet, I2C, I3C, MCAN, MMC/SD/SDIO, SPI, UART, USB

速度:-

主要属性:-

工作温度:-40°C ~ 105°C(TJ)

封装/外壳:433-BFBGA,FCBGA

供应商器件封装:433-FCBGA(17.2x17.2)

3、应用

• 汽车网关

• 车辆计算

• 车身控制模块

• 远程信息处理控制单元

• V2X/V2V

• 工厂自动化网关

• 通信设备

• 工业运输

• 楼宇自动化网关

注:本文部分内容与图片来源于网络,版权归原作者所有。如有侵权,请联系删除!

扫码关注

扫码关注

![Cadence17.4 GD32 ARM高速电路PCB硬件设计实战[第二部]](https://api.fanyedu.com/public/uploads/image/course/20200518/92b8de8dc1073a42c2d24b16c709e55e.jpg)