随着电子技术的飞速发展,高速PCB已成为各类电子设备中不可或缺的一部分,而PCB的布线设计则直接影响着电子产品的性能表现,在告诉电路中,更需要注意布线的设计,因此本文将介绍关于接口电路和时钟信号的告诉PCB布线技巧,帮助小伙伴们更好理解和应用实践中。

1、接口电路

接口变压器等隔离器件初次级互相隔离,无相邻平面等耦合通路;

接口电路的布线遵循先防护、后滤波的原则;

接口差分信号线严格遵循差分走线规则:并行、同层、等长;不同差分对之间距离满足3W原则,且旁边没有本接口信号以外的布线;

接口变压器与连接器之间的网络长度小于1000mil;

有外出电缆(大于3M)的接口变压器与对应的连接器之间的平面层挖空;网孔区域内应没有其他无关的信号线;

单板拉手条孔金属化,并接PGND;

接口芯片的电源地参考器件手册处理,如果需要分割时,数字部分不能扩展到对外接口信号线附近。

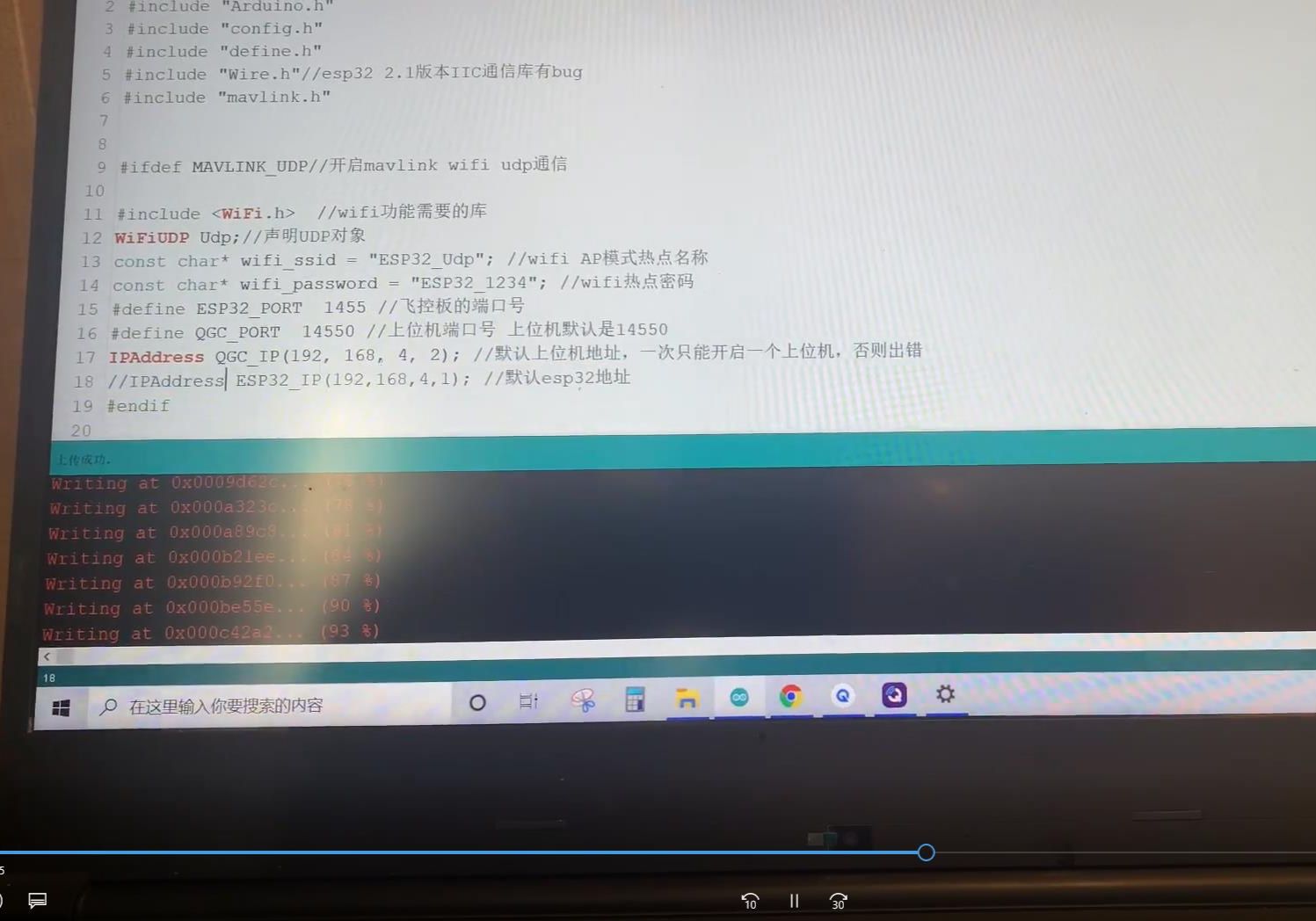

2、时钟信号

①EMC

时钟信号尽量少打孔,尽量避免和其他信号线并行走线,且远离一般信号线,避免对信号线的干扰,同时应避开板上的电源部分,以防止电源和时钟相互干扰;

当一块电路板上用到多个不同频率的时钟时,两根不同频率的时钟线不可并行走线;

时钟线还应尽量避免靠近输出接口,防止高频时钟耦合到输出的CABLE线上并沿线发射出去。

②时钟芯片

若板上有专门的时钟发生芯片,其下方不可走线,应在其下方铺铜,必要时还可对其专门割地处理;

对于很多芯片都有参考的晶体振荡器,这些晶振下方也不应走线,要铺铜处理;

同时可将晶振外壳接地。

③通用原则

时钟信号尽量走在内层,走线长度尽量短,同时要求有完整地平面回流,未跨分割或跨分割位置做桥接处理;

晶振及时钟驱动电路区域Top层无其他布线穿过;

晶振、时钟驱动芯片的滤波电路的布线遵照前述电源滤波布线要求;

时钟信号线周围避免有其他信号线(推荐满足3W);

当时钟信号换层且回流参考平面也改变时,可以考虑在时钟线换层过孔旁放置一接地过孔;

时钟布线与IO接口、拉手条的间距大于1000mil;

时钟信号与相邻平行布线的平行长度越短越好;

时钟线无线头,若因为测试需要,则线头越短越好。

④其他

走线优先级最高;

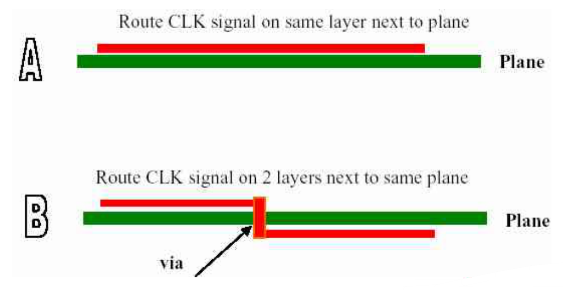

尽量不打孔走在同一层上,紧邻平面层,若要换层,需参考同一个平面层;

对时序要求的多个时钟尽量走在同一层上;

除fanout外,尽量不打过孔;

时钟信号距离其他信号的间距一定要保证,如果可以遵循4W原则。

扫码关注

扫码关注

![电子设计:[开源]全自动抓球-分色-投篮!视觉机器人的场地任务赛玩法~OpenMV_麦克纳姆轮_智能小车](https://api.fanyedu.com/uploads/image/d2/3f92982b0f701f43d0efeb9eb8fc21.png)