之前我们聊了可测性设计的四个常见问题及解决方法,接下来将更新下篇,希望能够帮助到小伙伴们,以及若是想看上篇,可点击右侧链接《可测性设计中常见问题及解决方法(上)》。

5、有内部生成的异步复位、置位信号;

内部生成的异步复位、置位信号的处理:有些设计存在内部生成的异步复位、置位信号,如果不对这些信号进行控制,则在扫描过程中,极有可能改变寄存器的状态,从而破坏扫描链中的数据,为避免这种问题,应加入相应的控制逻辑,以保证在扫描模式下这些异步信号不会影响扫描寄存器的状态。

6、在扫描模式下,在三态总线上有冲突;

三态缓冲的处理:有些设计中存在三态缓冲单元,在扫描时这些三态缓冲不应出现输出冲突的现象。

此外,全扫描只检查0与1,无法检查高阻,因此输出总线上不应为高阻态,在扫描时恪尽职守所有三态缓冲使能信号,然后通过上下拉电阻给总线固定值,从而避免输出总线上的高阻态,但这种方法消耗功耗过大,所以常见方法是在扫描时只允许一个三态缓冲使能。

7、设计中存在锁存器;

锁存器的处理,若DC设计中存在锁存器,讲给扫描测试带来问题,若锁存器的使用是不可避免,则需要在扫描测试时使这些锁存器保持使能状态,这样看起来就像是“透明的”,数据直接可以通过锁存器来传递。

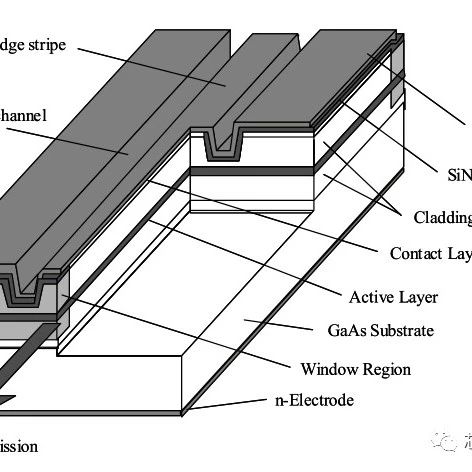

若一个设计中包含大量锁存器,且希望对这些锁存器进行扫描测试,则可以将它们置换为LSSD(电平敏感扫描设计)单元,然后单独组成扫描链。

LSSD是锁存器扫描设计中最常用的方法,在LSSD扫描单元中,两个锁存器构成了master slave对。

8、存在存储器等无法扫描测试的电路;

存储器的处理:在设计中,存储器是很常见的,存储器是无法进行扫描测试,一般采用BIST方法进行测试。在进行扫描测试时,可将存储器看做是一个黑盒子,扫描链可绕开存储器。

9、存在反馈环路。

反馈环路的处理:在设计中应尽量避免组合反馈环路,这是因为反馈环路会导致静态时序分析、DFT等难以处理,并可能会潜伏着错误。

扫码关注

扫码关注