一个芯片的功耗过大,是会引发多种问题,如性能变差、温度升高降低芯片可靠性、极大限制便携式产品的使用时间及电池寿命,所以工程师要尽量降低芯片的功耗影响,尤其是高性能设计或便携式应用,那么如何降低IC设计的功耗问题?

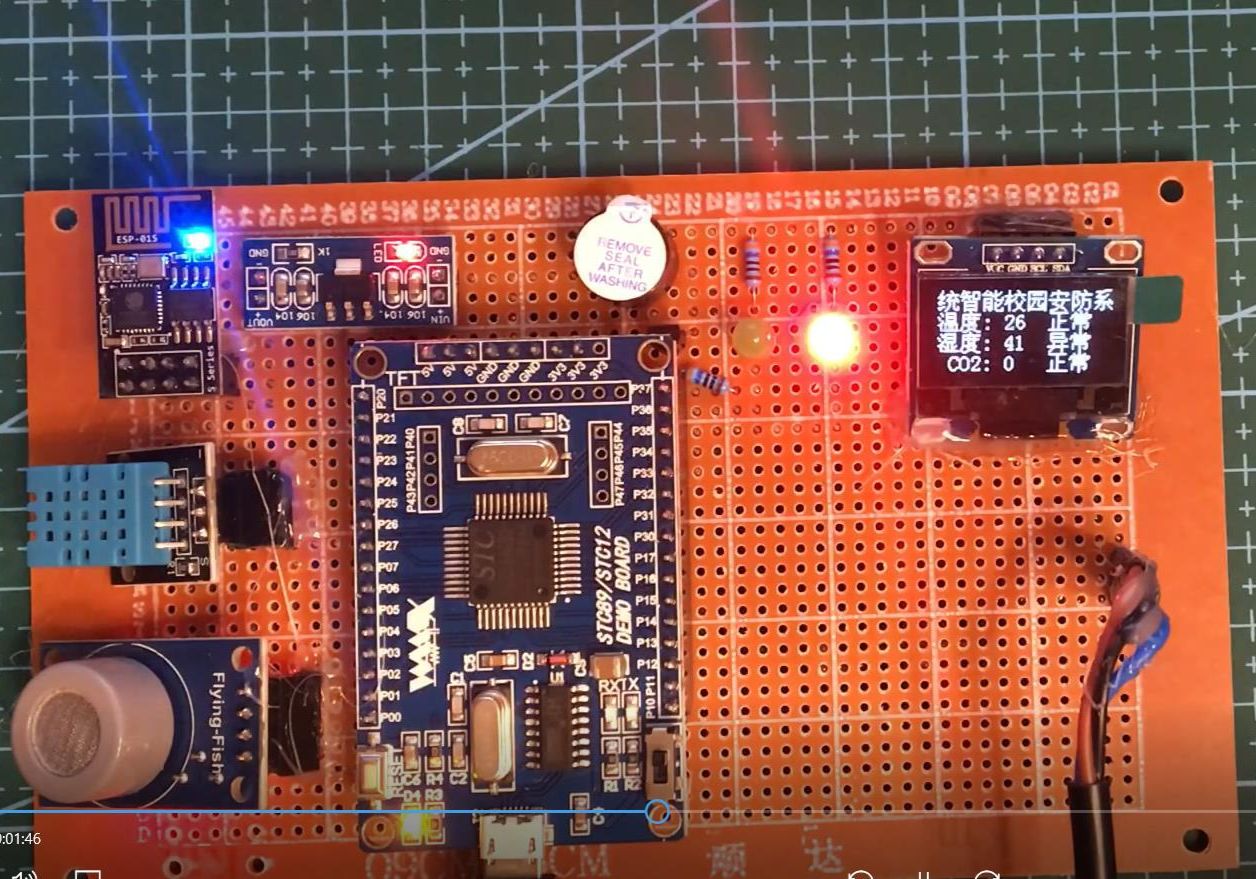

工程师对于高性能设计或便携式应用,必须采用低功耗芯片,如数字信号处理器、手机芯片等。

针对如何降低芯片的功耗问题,电子工程师必须采用低功耗设计技术,而低功耗设计是可以从系统级、逻辑电路级、物理级着手。具体做法如下:

在系统级,进行软硬件划分时,要综合考虑那种方案是能得到更少的功耗,要选择功耗最小的算法,可考虑并行运算、流水线等手段、降低功耗;可采用多电压设计方案来降低功耗;可设置省电模式,以便在系统不工作时降低功耗。

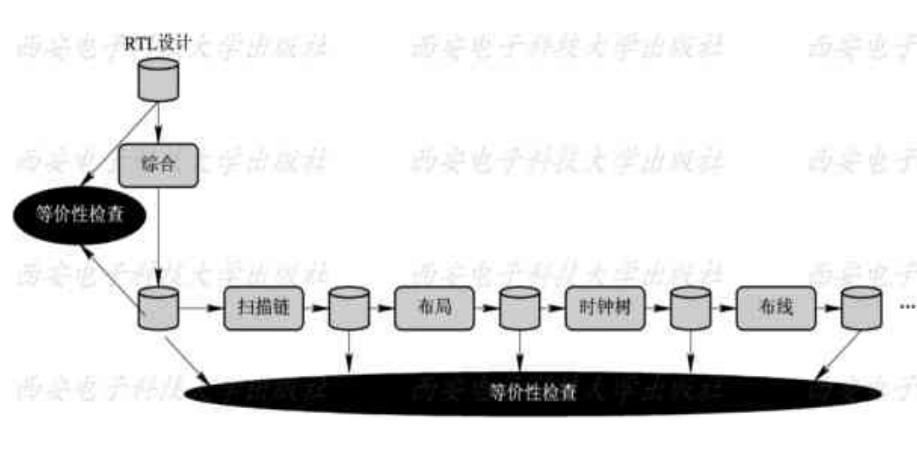

在RTL级,可考虑采用时钟门控、操作数隔离等技术来降低功耗。

在逻辑综合时,可考虑采用插缓冲、相位分配等技术来降低功耗。

在进行布局布线时,也要考虑到功耗的影响,可以将翻转率高的节点用寄生电容较小的金属层来布线,以减少整体功耗。

此外,电子工程师还可考虑采用新的材料、新的封装技术来境地功耗,以消除功耗的影响。

芯片速度的提高,工艺水平的进步,便携式应用的增加,封装技术发展的相对迟缓,这些因素使低功耗设计在IC设计中越来越重要,低功耗设计技术可能会导致速度变慢、芯片面积增加、设计周期延长,但这总比需要依靠封装、风扇甚至液氮等降温更好。

在进行低功耗设计前,首先要进行功耗分析,了解设计中哪部分消耗功耗最大,何种功耗所占比例最大,接下来才能决定研究降低功耗的设计方法。

在实际应用中,通常在门级和经过级进行功耗分享,有些工具也支持RTL级的功耗分享,以帮助工程师尽早了解设计中功耗的情况。

利用功耗分析工具可得到峰值功耗与平均功耗,影响温度的是平均功耗,下面将列出Synopsys与功耗分析有关的工具。

power compiler:对动态功耗和泄漏功耗进行优化;

primepower:对峰值功耗和平均功耗进行分析;

JupiterXT:生成电源网格;电源网络分析

Astro Rail:电压降及电子迁移分析。

扫码关注

扫码关注

![电子设计:[2021电赛F题]OpenMV模板匹配实用教程,8数字同时识别40帧+,源码程序一行一行讲解,包教包会](https://api.fanyedu.com/uploads/image/f9/db2f5ce7a4caa6438d4267bfa894c0.png)