- 全部

- 默认排序

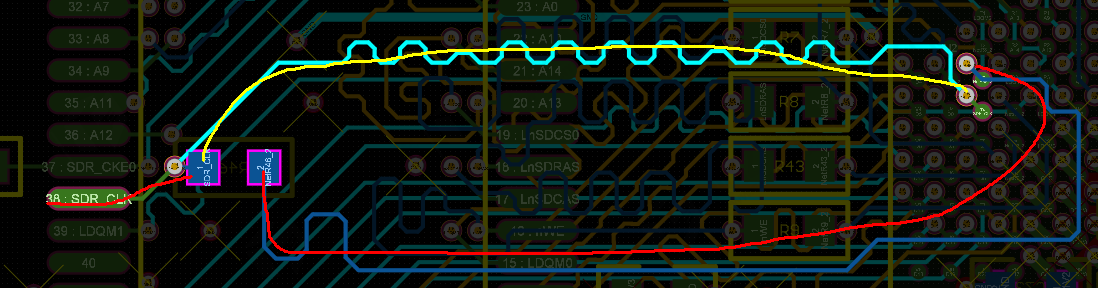

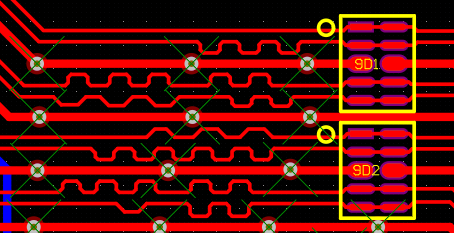

时钟信号等长错误地址线等长组有几个信号等长不到目标长度,电阻到芯片段加入一起等长应避免走线造成信号回路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.ta

提起差分信号,很多电子工程师都不会陌生,得益于高速数字信号传输中的广泛应用,差分信号的走线在PCB设计中具有重要地位,为了确保差分信号的完整性,工程师需要遵循一些特定的规则,身为工程师的你知道有哪些规则吗?1、相对路径长度匹配差分信号对的两

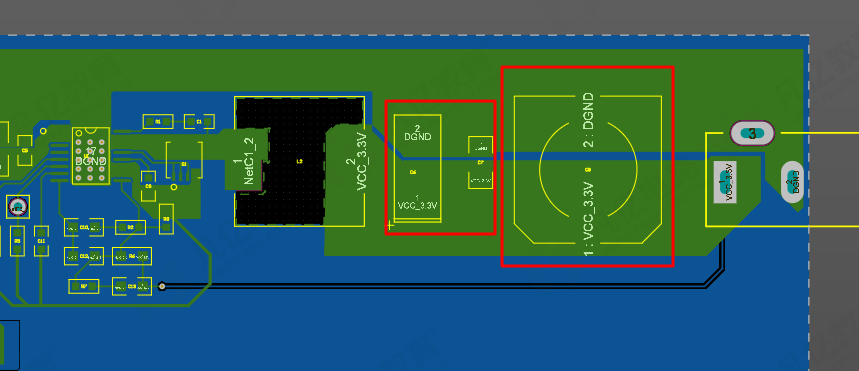

器件遵循先大后小原则摆放,大电容放到前面小电容放大电容后相邻电路电感应朝不同方向垂直放置焊盘出线避免从长边、四角出线,铺铜、走线尽量避免直角锐角器件尽量中心对齐,相邻器件尽量朝一个方向放置以上评审报告来源于凡亿教育90天高速PCB特训班作业

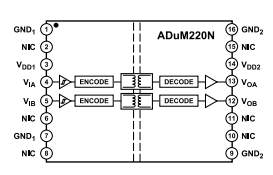

1、ADUM220N0BRWZ 可靠的 5.0 kV rms 双通道数字隔离器、0 个反向通道和 7.8mm 爬电距离ADuM220N 是一款采用iCoupler®技术的双通道数字隔离器。该隔离器件将高速、互补金属氧化物半导体(CMOS)与

随着时代高速发展,国家开始意识到半导体的重要性,多次办不相关法规政策,扶持本土半导体企业发展,加大半导体人才培养,最终取得一定的成果。据外媒报道,得益于中美竞争战及时代发展,2022年中国申请的半导体专利占比高达71.7%,而2003年中国

差分等长不耦合,差分对间等长可以用差分等长命令上面也要包地处理RJ45:提交作业的时候铺一下铜走线不要从电阻中间穿过以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://

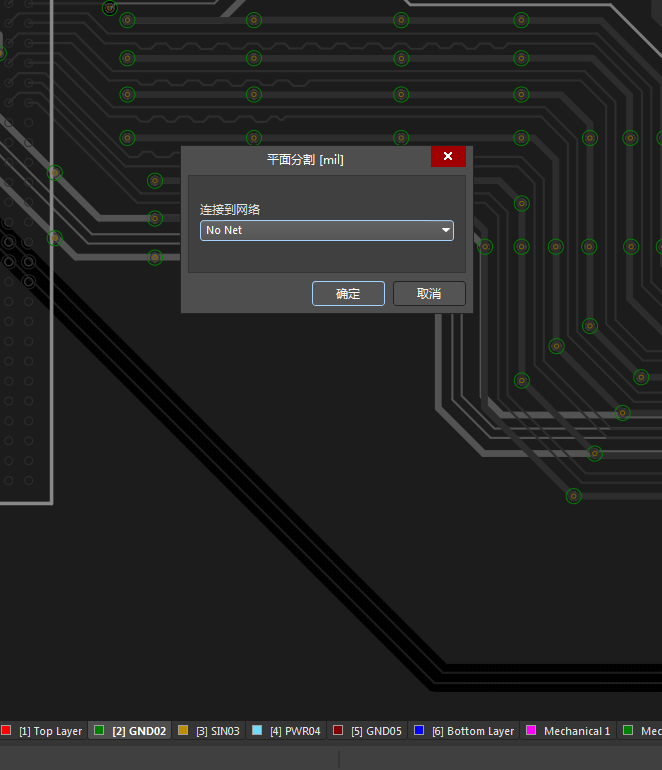

DD3 四片:注意不要出现这种锐角走线:负片层并未赋予网络:注意设计完了之后检查下走线的连接性:并未保证3W间距原则:差分对内等长注意规范:差分对内等长误差为5MIL:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特

差分对内等长误差不满足+-5mil这里可以这样出线这里要这样连接以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm?s

地负片层并未赋予网络:差分对内等长注意规范:上述一致原因:差分对内等长5MIL:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/it

随着科技高速发展,半导体器件日益小型化、智能化等,尺寸的减小,必然带来更加严重的功率密度和热量问题,这些问题若是不及时处理,既有可能影响这些器件的性能、可靠性和寿命。因此,如何提高晶体管的散热能力,是很多科学家及机构的研究重点。近日,日本的

扫码关注

扫码关注