- 全部

- 默认排序

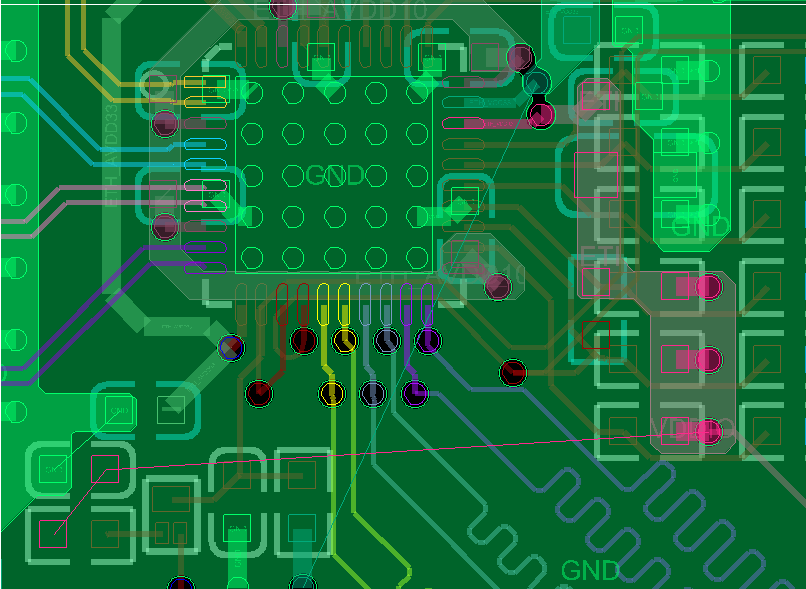

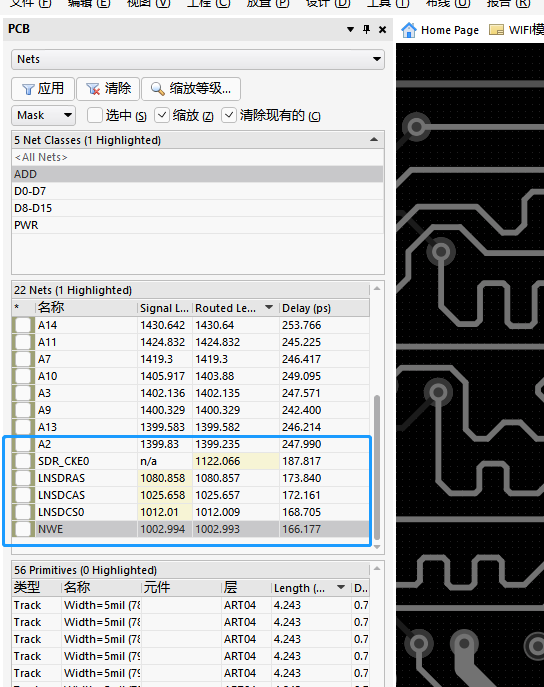

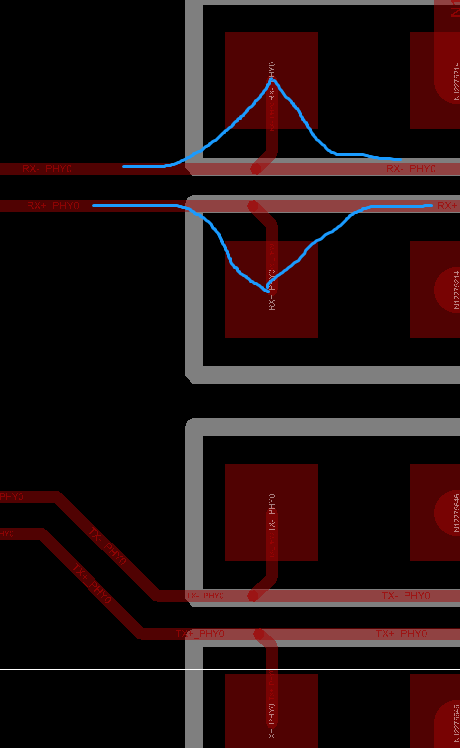

这里有未连接的线路变压器下未挖空处理这两组差分对内误差要小于5mil晶振背面不允许走线和放置器件,并且晶振需要包地处理变压器这里的线除了差分要不小于20mil这个间距要大于1mm这里走线不满足载流以上评审报告来源于凡亿教育90天高速PCB特

随着信息高速发展,越来越多人选择在手机、电脑等多种电子设备设置密码,但设置密码后是否保证隐私信息是安全了吗?不一定!近日,来自格拉斯哥大学的研究团队发现:若黑客使用人工智能辅助的热成像技术,来盗窃刚输入不久的密码,且成功率很高,这意味着若是

随着现代高速数字电路急速发展,差分信号传输已成为当代电子工程师必须掌握的重点技术之一,它可以有效抵消信号传输过程中的共模噪声,在差分信号传输中,如何正确匹配差分阻抗是至关重要的,所以本文将讨论如何在PCB布线阶段中正确匹配差分阻抗?在PCB

高速PCB设计在现代电子产品中越来越重要,而高速信号的传输问题也日益成为PCB工程师面临的问题之一,那么在高速PCB设计中如何解决高速信号传输中的问题?也许本文能给你一些参考。一般来说,高速信号传输中会出现多种问题,如时钟抖动、时序失真、瞬

当今电子设备高速发展,高性能高数据处理量必然带来愈发严重的电磁问题,电磁干扰(EMI)正是其中之一,EMI是无法消除的,但可通过技术及电路设计来降低EMI的影响,下面将讨论如何在电路设计中减少EMI影响。首先,需要了解下什么是EMI,简单来

这个差分需要优化一下。这里过孔打到焊盘上了晶振需要包地处理走线也要走类差分变压器这里的走线除了差分都要大于20mil时钟要包地处理这里等长不要有直角长度也要大于3w以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班

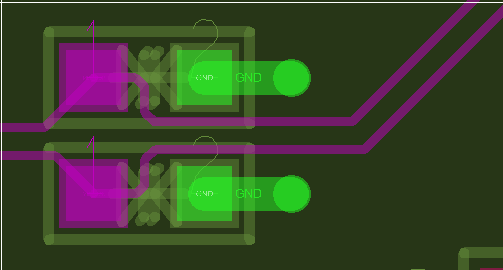

等长存在报错,电阻另一端需要看成一根进行等长2.此处一层连通无需打孔3.滤波电容尽量靠近管脚放置4.过孔需要盖油处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://

差分出线方式可以在优化一下2.差分对内等长误差5mil3.TX和RX未添加等长组进行等长,等长误差100mil4.自己后期再地平面铺一个整版地铜对地进行连接以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以

熟悉硬件/单片机的工程师,想必对PCIe接口不陌生吧!PCIe是一种高速串行总线接口,主要功能是数据传输,被广泛应用计算机、工业控制等多种领域。若是遇见PCIe的PCB项目该如何做?不如来看看这篇文吧!本文将介绍PCIe接口的PCB设计技术

做好心理准备。- 1 -今天,看到北京人社部率先发文表示:企业效益不好亏损较大可合法进行降薪。这个表述还是比较罕见的,因为在三十多年的高速发展中:大家对加薪的预期已经比较习惯了,对降薪反而没有什么心理准备。一个很普遍的场景就是,大家会用未来的收入增长来做当下的消费决策,比如买房,很多人程序员在这上面

扫码关注

扫码关注