- 全部

- 默认排序

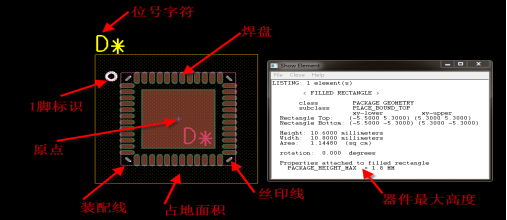

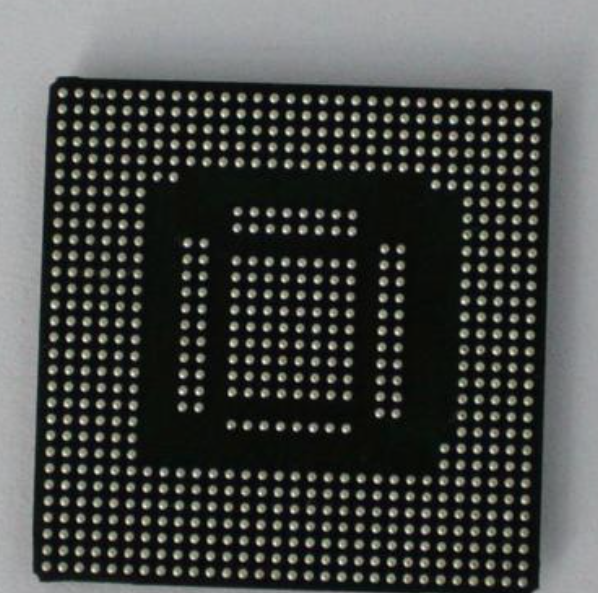

答:一个完整的PCB封装是由许多不同元素组合而成的,不同的器件所需的组成元素也不同。一般来说,封装组成元素包含:沉板开孔尺寸、尺寸标注、倒角尺寸、焊盘、阻焊、孔径、热风焊盘、反焊盘、管脚编号(Pin Number)、管脚间距、管脚跨距、丝印线、装配线、禁止布线区、禁止布孔区、位号字符、装配字符、1脚标识、安装标识、占地面积、器件高度。在Cadence Allegro软件中,以下元素是必须要有的:焊盘(包括阻焊、孔径等内容)、丝印线、装配线、位号字符、1脚标识、安装标识、占地面积、器件最大高度、极

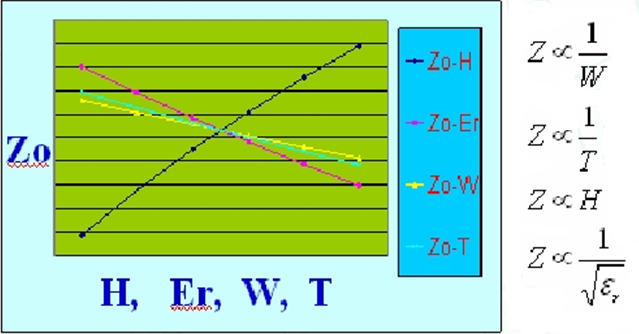

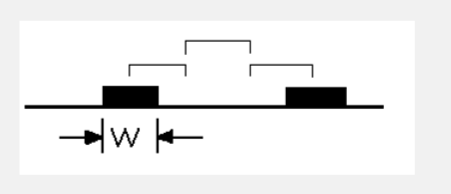

答:一般来说,影响PCB特性阻抗的因素:介质厚度H、铜的厚度T、走线的宽度W、走线的间距、叠层选取的材质的介电常数Er、阻焊的厚度。一般来说,介质厚度、线距越大阻抗值越大;介电常数、铜厚、线宽、阻焊厚度越大阻抗值越小。这些因素与特性阻抗的关系如图1-20所示。 图1-20 影响PCB特性阻抗分布图第一个:介质厚度,增加介质厚度可以提高阻抗,降低介质厚度可以减小阻抗;不同的半固化片有不同的胶含量与厚度。其压合后的厚度与压机的平整性、压板的程序有关;对所使用的任何一种板材,要取得其可生产的

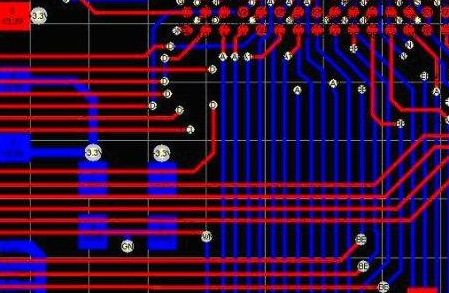

答:在进行阻抗、层叠设计的时候,主要的依据就是PCB板厚、层数、阻抗值要求、电流的大小、信号完整性、电源完整性等,一般参考的原则如下:l 叠层具有对称性;l 阻抗具有连续性;l 元器件面下面参考层尽量是完整的地或者电源(一般是第二层或者倒数第二层);l 电源平面与地平面紧耦合;l 信号层尽量靠近参考平面层;l 两个相邻的信号层之间尽量拉大间距。走线为正交;l 信号上下两个参考层为地和电源,尽量拉近信号层与地层的距离;l&nbs

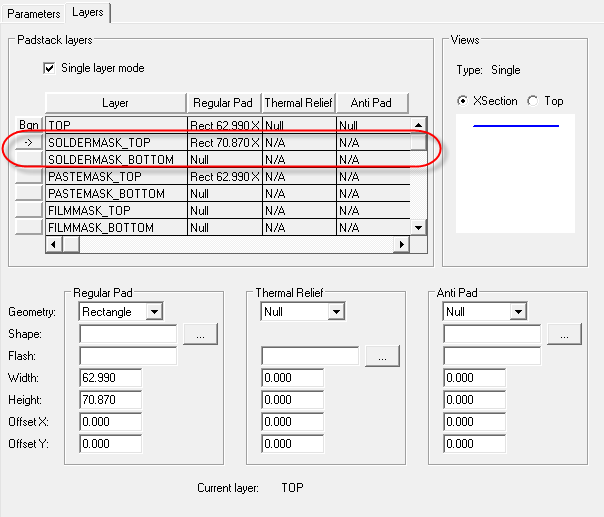

答:焊盘设计阻焊的原则如下:Ø 阻焊开窗应该比焊盘大6mil以上;Ø PCB设计的时候贴片焊盘之间、贴片焊盘与插件之间、过孔之间要保留阻焊桥,最小的宽度为4mil;Ø PCB走线、铺铜、器件等到阻焊开窗的距离要6mil以上;Ø 散热焊盘应该做开全窗处理,并在焊盘上打上过孔;Ø 金手指的焊盘的开窗应该做开全窗处理,上端跟金手指上端平齐,下端要超出金手指下面的板边,金手指顶部的开窗与其它走线、铺铜、器件的间距要大于20mil;Ø 我们在Al

答:1)需要塞孔的过孔在正反面都不做阻焊开窗;2)需要过波峰焊的PCB板卡,BGA下面的过孔都需要做塞孔处理、不开窗;3)BGA器件的pintch间距≤1.0mm,BGA下面的过孔都需要做塞孔处理、不开窗;4)BGA器件加的ICT测试点,测试焊盘直径32mil,阻焊开窗37mil。

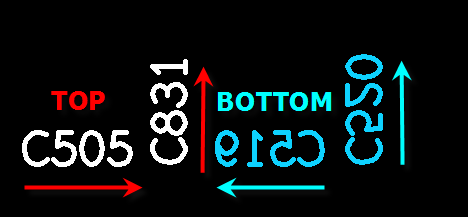

答:一般情况下,我们推荐位号字符在与阻焊不干涉的情况下,推荐位号字符与SMD焊盘、插装焊接孔、测试点、Mark点至少保证6mil的间距,位号字符之间部分重合是可以的,任何位号字符由于重叠导致的无法辨认必须进行调整。位号字符的方向设定,一般推荐在正视的情况下,位号字符的排列是从左到右,从上到下的,如图1-30所示,TOP面与Bottom面的位号字符排列。 图1-30 TOP面与Bottom面的位号字符排列示意图

答:1)BGA器件与外围其它器件保持至少间距3mm,有空间的情况下做到5mm;2)QFN、QFP、PLCC、SOP器件之间保持间距2.5mm;3)QFP、SOP器件与Chip、SOT器件之间保持间距1mm;4)QFN、PLCC器件与Chip、SOT器件之间保持间距2mm;5)PLCC表面贴脚座与其它元器件之间保持间距3mm;6)插件器件正面(不需要焊接的面)与其它元器件保持间距1.5mm;7)插件器件背面(焊接面与)其它元器件保持间距3mm,最好插件器件里面不要放置贴片的元器件,返修非常困难;8

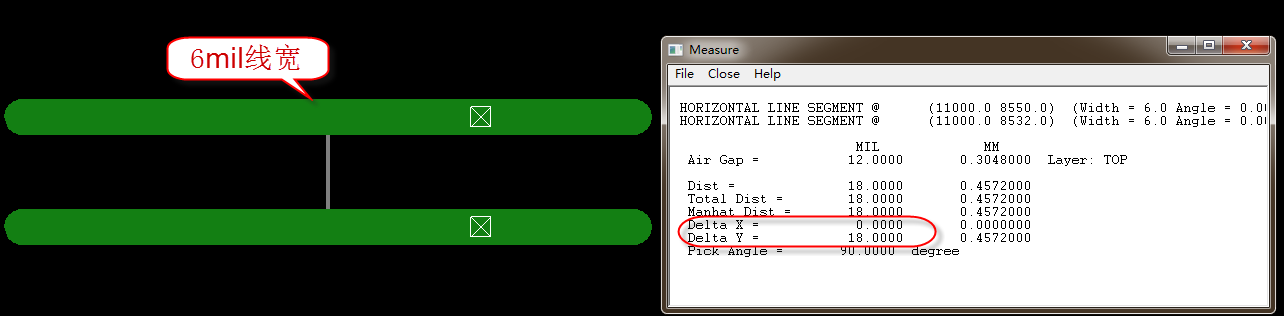

答:为了信号走线的质量,不产生串扰,我们保持信号走线与信号走线之间的间距为3倍线宽,这个间距指的是走线的中心到中心的间距,因为我们的线宽英文是width,所以这个规则我们通常就叫做3W原则。当我们的走线的中心间距不少于3倍线宽时,可以保证70%的线间电场不互相干扰,如果信号需要达到98%的线间电场不互相干扰,可以使用10W规则。3W原则是一种设计者无须其他设计技术就可以遵守PCB布局的原则。但这种设计方法占用了很多面积,可能会使布线更加困难。使用3W原则的基本出发点是使走线间的耦合最小。这种原则

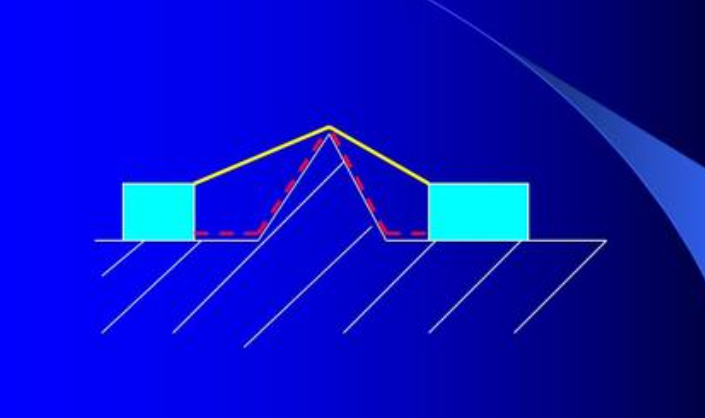

答:第一,3W原则,在PCB设计中很容易体现,保证走线与走线的中心间距为3倍的线宽即可,如走线的线宽为6mil,那么为了满足3W原则,在Allegro设置线到线的规则为12mil即可,软件中的间距是计算边到边的间距,如图1-38所示. 图1-38 PCB中3W原则示意图第二,20H原则,在PCB设计的时候,为了体现20H原则,我们一般在平面层分割的时候,将电源层比地层内缩1mm就可以了。然后在1mm的内缩带打上屏蔽地过孔,150mil一个,如图1-39所示。 图1

答:沿绝缘表面测得的两个导电零部件之间,在不同的使用情况下,由于导体周围的绝缘材料被电极化,导致绝缘材料呈现带电现象,此带电区的半径即为爬电间距。爬的意思,可以看做一个蚂蚁从一个带电体走到另一个带电体的必须经过最短的路程,就是爬电距离。电气间隙,是一个带翅膀的蚂蚁,飞的最短距离。

扫码关注

扫码关注