- 全部

- 默认排序

★掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程★掌握DDR3设计的知识要点★掌握3W原则的PCB设计★了解T点拓扑结构及设计规则★掌握蛇形等长走线,阻碍线的使用★掌握叠层阻抗计算的方法★了解常见EMC的PCB处理方法

1. 掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程 2. 掌握DDR3设计的知识要点 3.掌握3W原则的PCB设计 . 了解菊花链拓扑结构及设计规则 . 掌握蛇形等长走线

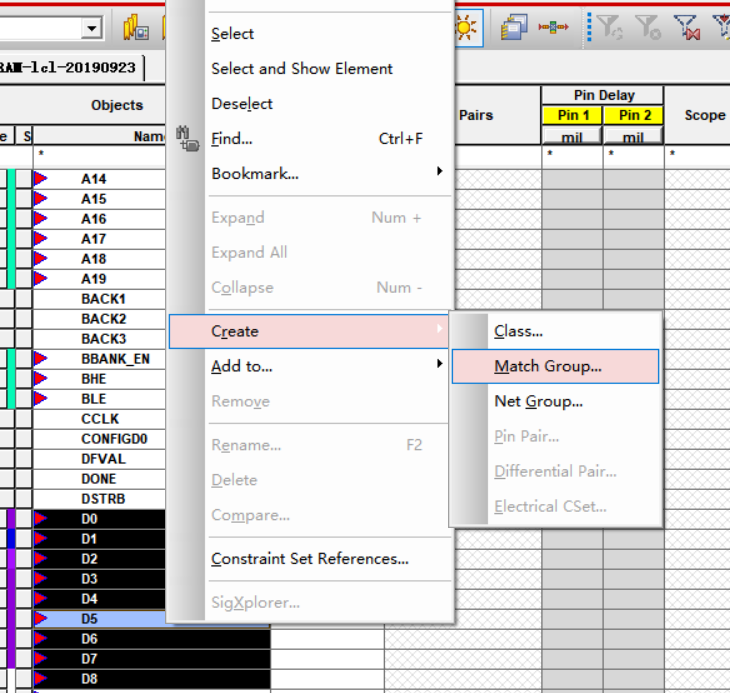

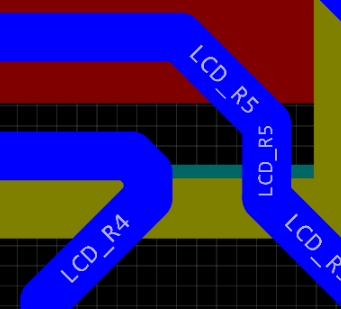

SDRAM信号线等长处理

在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。

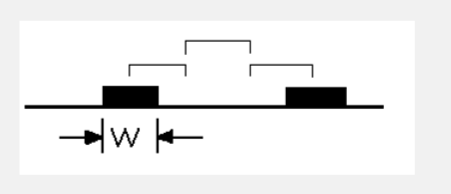

答:为了信号走线的质量,不产生串扰,我们保持信号走线与信号走线之间的间距为3倍线宽,这个间距指的是走线的中心到中心的间距,因为我们的线宽英文是width,所以这个规则我们通常就叫做3W原则。当我们的走线的中心间距不少于3倍线宽时,可以保证70%的线间电场不互相干扰,如果信号需要达到98%的线间电场不互相干扰,可以使用10W规则。3W原则是一种设计者无须其他设计技术就可以遵守PCB布局的原则。但这种设计方法占用了很多面积,可能会使布线更加困难。使用3W原则的基本出发点是使走线间的耦合最小。这种原则

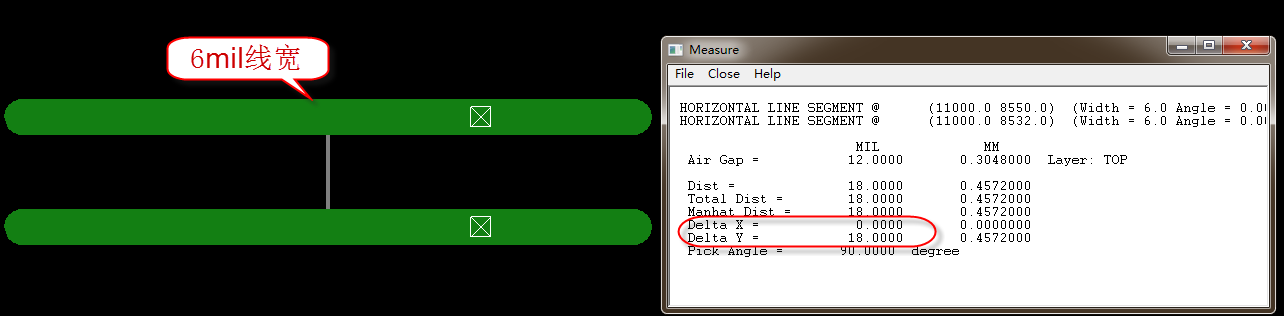

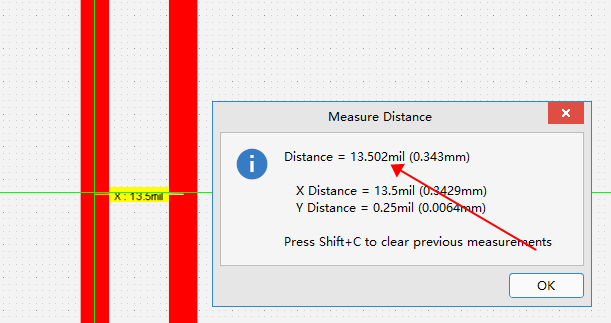

答:第一,3W原则,在PCB设计中很容易体现,保证走线与走线的中心间距为3倍的线宽即可,如走线的线宽为6mil,那么为了满足3W原则,在Allegro设置线到线的规则为12mil即可,软件中的间距是计算边到边的间距,如图1-38所示. 图1-38 PCB中3W原则示意图第二,20H原则,在PCB设计的时候,为了体现20H原则,我们一般在平面层分割的时候,将电源层比地层内缩1mm就可以了。然后在1mm的内缩带打上屏蔽地过孔,150mil一个,如图1-39所示。 图1

答:为了信号走线的质量,不产生串扰,我们保持信号走线与信号走线之间的间距为3倍线宽,这个间距指的是走线的中心到中心的间距,因为我们的线宽英文是width,所以这个规则我们通常就叫做3W原则。

答:第一,3W原则,在PCB设计中很容易体现,保证走线与走线的中心间距为3倍的线宽即可,如走线的线宽为4.5mil,那么为了满足3W原则,在AD设置线到线的规则为9mil即可,那么中心距是13.5mil,如图1-38所示.

差分线这里需要调整走线尽量不要有直角锐角这里是输出走线应该加粗处理最好铺铜处理。SD卡所有信号线要做等长处理,以时钟线为目标,目标控制在300mil以内。这个差分在这里另一根就断了,不耦合对内也不等长。很多的线间距都不满足3W原则自己调整一

这里器件干涉了,调整一下这个网口所有层都需要挖空处理电感所在层内部铜皮需要挖空这里部分走线不满足3W原则,不满足地方有点多就不一一指出了这根线等长不满足要求需要调整一下这个等长这个边要大于等于3w差分对内没等长不满足+-5mil这个RJ45

扫码关注

扫码关注