- 全部

- 默认排序

答:orcad创建封装库时,放置管脚的Shape的含义是管脚的长度以及一些特殊含义,其表示的含义解释如下:Clock:时钟信号,管脚的长度是标准长度;Dot:低电平有效信号,管脚的长度是标准长度;Dot-Clock:低电平有效的时钟信号,管脚的长度是标准长度;Line:普通信号,管脚的长度是标准长度;Short:普通信号,管脚的长度比标准的长度要短一些;Short Clock:时钟信号,管脚的长度比标准的长度要短一些;Short Dot:低电平有效信号,管脚的长度比标准的长度要短一些;Short

答:根据器件规格书(Datasheet)制作封装时,一般做出来的封装焊盘管脚长度需要做适当的补偿,即适量地对器件原先的管脚加长一点,具体的补偿方法,是根据器件的管脚类型来补偿的,可按以下办法:第一类,无引脚延伸型SMD封装,如图4-100所示: 图4-100 无引脚延伸型SMD封装示意图A—零件实体长度 X—补偿后焊盘长度 H—零件脚可焊接高度

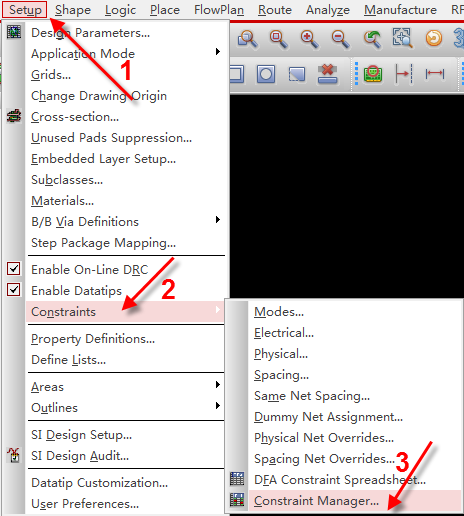

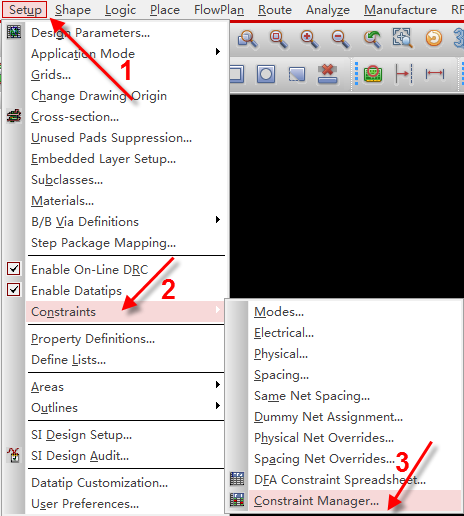

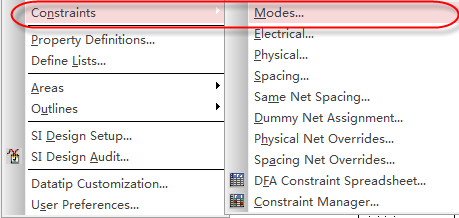

答:我们在设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。一般情况下如果信号是从一个点传输到另一个点,中间没有任何的串阻、串容,这个绝对传输延迟的方法还是非常有效而却直观的。具体在PCB中设置绝对传输延迟的方法如下所示:

答:我们在Allegro软件中,不论是做绝对传输延迟还是做相对传输延迟,从所有的等长列表中可以看到,它的本质都是从一个元器件的管脚连接到另一个管脚的长度,也就是我们所说的Pin-Pair到Pin-Pair的长度。我们创建等长集合,其实也是创建Pin-Pair的集合,这里,讲解一下,Allegro软件中如何创建Pin-Pair,具体操作如下:

答:所谓的Xnet,是指在无源器件的两端,两个不同的网络,但是本质上其实是同一个网络的这种情况。比如一个源端串联电阻或者串容两端的网络。在实际设计情况中,我们需要对这种进行Xnet的设置,方便进行时序等长的设计,一般信号传输要求都是信号的传输总长度达到要求,而不是分段信号等长,这时采用Xnet就可以非常方便的实现这一功能,在Allegro软件中添加xnet的具体步骤如下所示:

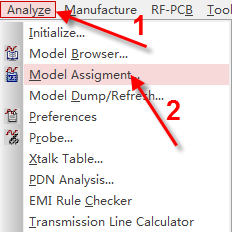

答:我们在时序等长时,除了考虑信号线的走线的长度以外,在高速设计领域里还需要考虑封装本身的引脚长度。所谓封装引脚长度,指的就是元器件封装内部的引脚长度,这个长度一般芯片的厂家会提供这数据,我们要做的就是将数据导入到规则管理器中,与等长一起处理,具体的操作步骤如下:

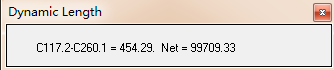

答:使用Allegro走线的时候,可以动态地显露走线的长度信息,具体操作的步骤如下所示:首先,点击Setup-User Preferences,在弹出的User Preferences Editor选项卡中勾选

在设计原理图库原件的时候,原件过小。但是器件管脚长度过长,显得器件很不协调。第一步:执行快捷键命令PP放置管脚,如图1所示。图1第二步:双击管脚,弹出属性框,在PIN length处修改既可。如图2所示。图2

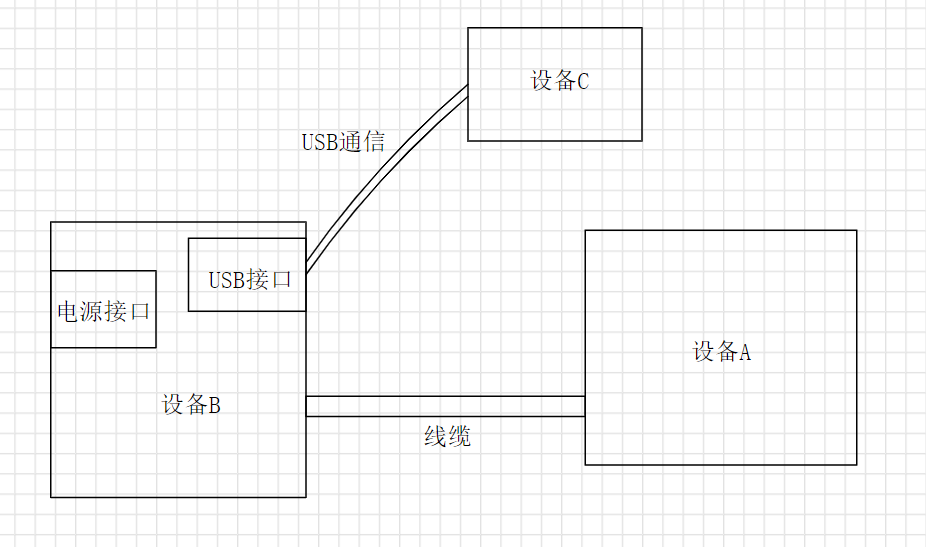

#凡亿7月星企划#整体系统框架如下,设备B接受适配器供电,通过线缆与设备A通信。设备A的USB信号通过线缆,经过设备B的USB口,与设备C通信。线缆长度2M,USB通信线长1M。在测试设备B的眼图时不通过(Far end fail),如下:

扫码关注

扫码关注