- 全部

- 默认排序

等长线是为了减少信号相对延时,常用在高速存储器的地址和数据线上,简单来说:等长线的作用,就是让信号传输的速度一致。在pads软件中只能在routet里面才能建立匹配长度的网络组,并进行等长的工作。

本视频的讲解主要是讲解关于我们如何进行高亮我们的对应的网络,以及如何高亮我们的对应的其它网络,以及如何测量我们的此网络的线段的长度的一个小技巧的操作过程。

我们在进行PCB设计的时候,会碰到需要去标注板框的长度跟宽度。而且有时候还限制了必须要用MM或者MIL的单位,那么这个时候我们如何去进行单位的切换呢?其实很简单,跟我们平时在属性框输入参数值要切换单位的时候操作是一样的,我们就以AD19软件为例,进行这项操作的分析。

2024年全国大学生电子大赛手把手教你做电赛项目扫码领取课程素材2024年7月11日,凡亿教育开展第三届电赛特训营,本次直播题目是制作一个“同轴电缆长度与终端负载检测装置”(23年全国电赛本科B题),直播过程会完整地讲解项目设计方案、原理图

差分走线,信号换层过孔数量,等长长度把控,阻抗控制要求,跨分割的损耗,走线拐角的位置形状,绕线方式对应的插损和回损,布局不妥当造成的一系列串扰和叠层串扰,布局不恰当操作焊盘存在的stub。

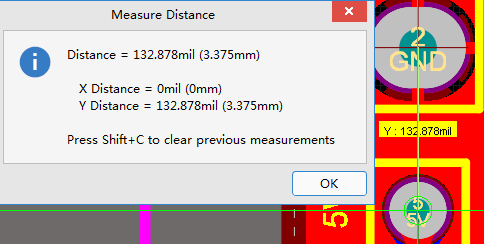

一、点到点距离的测量 这种测量主要用于对某两个对象之间大概距离的一个评估。执行菜单命令“报告-测量距离”(快捷键“Ctrl+M”或者“RM”),激活点到点距离测量命令,再用鼠标单击起点和终点位置,系统测量之后会弹出一个标出X轴与Y轴长度的报告,如图11-19所示。

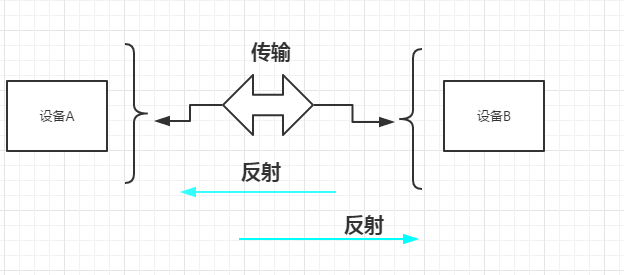

我们在用allegro进行PCB设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。

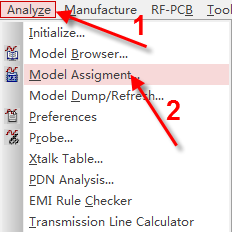

所谓的Xnet,是指在无源器件的两端,两个不同的网络,但是本质上其实是同一个网络的这种情况。比如一个源端串联电阻或者串容两端的网络。在实际设计情况中,我们需要对这种进行Xnet的设置,方便进行时序等长的设计,一般信号传输要求都是信号的传输总长度达到要求,而不是分段信号等长,这时采用Xnet就可以非常方便的实现这一功能,在Allegro软件中添加xnet的具体步骤如下所示:第一步,执行菜单命令Analyze-Model Assigment,进行模型的指定,如图5-112所示; 图5-11

扫码关注

扫码关注