- 全部

- 默认排序

答:过孔的两个寄生参数是寄生电容和寄生电感。过孔本身存在着对地的寄生电容,如果已知过孔在铺地层上的隔离孔直径为D2,过孔焊盘的直径为D1,PCB板的厚度为T,板基材介电常数为ε,则过孔的寄生电容大小近似可以用以下公式来计算:C=1.41εTD1/(D2-D1)。过孔的寄生电容会给电路造成的主要影响是延长了信号的上升时间,降低了电路的速度。比如说,对于一块厚度为50Mil的PCB板,如果使用内径为10Mil,焊盘直径为20Mil的过孔,焊盘与地铺铜区的距离为32Mil,则我们可以通过上面的公式近似

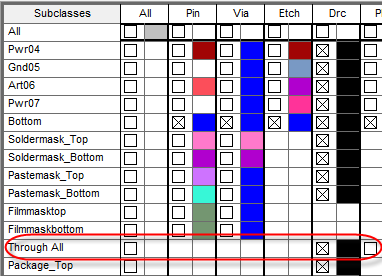

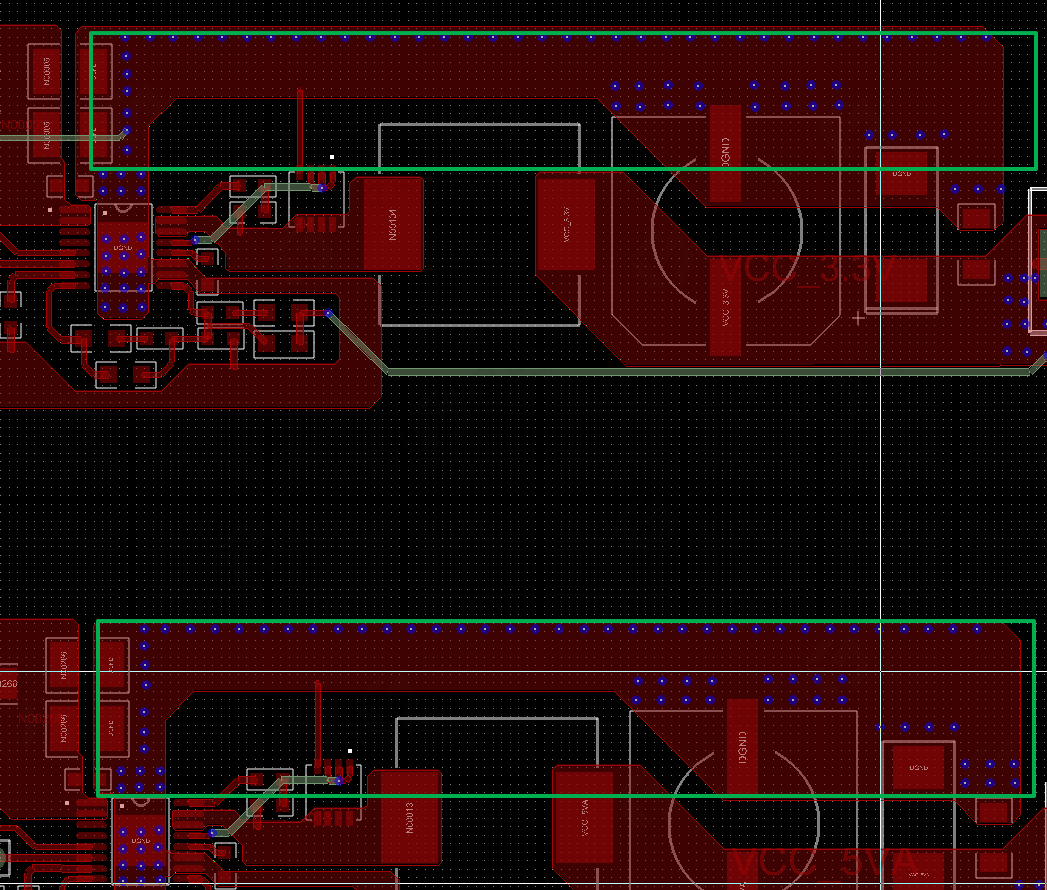

答:我们在PCB设计完成之后,都需要对整板铺地铜处理,然后在铺的地铜上面放置地过孔,但是有这样一个现象,相同的地过孔放重叠了,并不会产生DRC错误,我们应该如何设置,才可以让相同网络的重叠过孔产生DRC错误呢,这里讲解一下,具体操作如下所示:

1.底层没有铺地铜。 2.铺铜都放错层,铜皮放到机械层,铜皮没有网络。3.很多过孔和走线没有网络。4.存在大量飞线,焊盘存在开路。请认真对待每一次作业,不是从参考上复制布局交上来就没事了。以上评审报告来源于凡亿教育90天高速PCB特训班作业

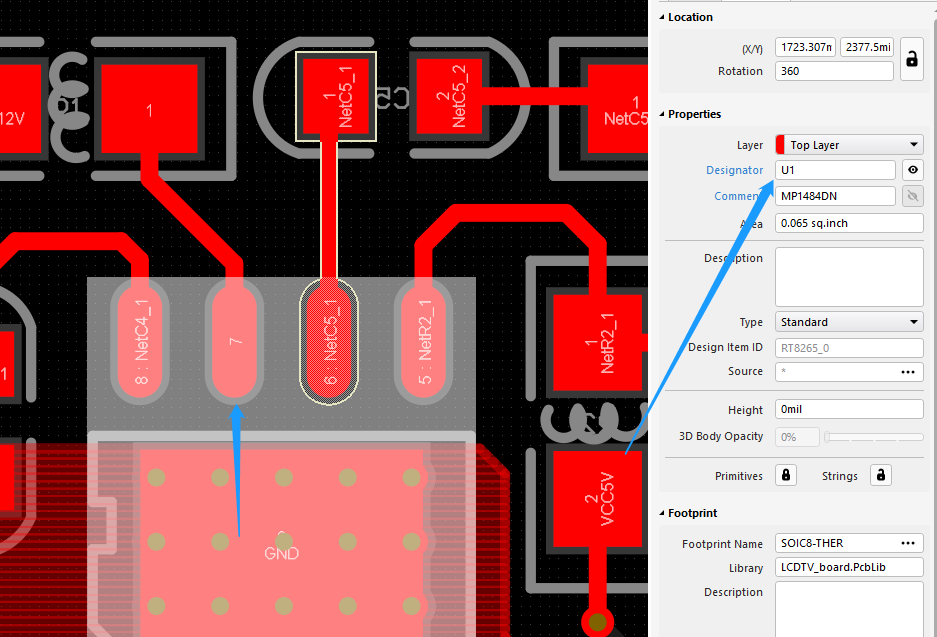

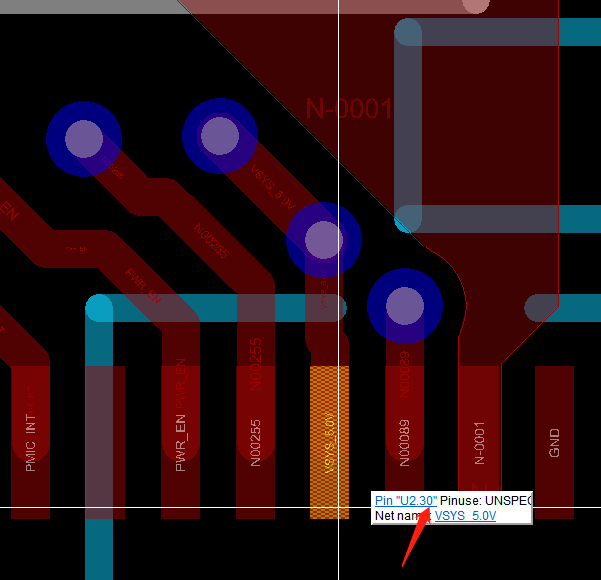

此处网络未导入pcb2.走线未从焊盘中心出线3.器件摆放尽量中心对齐处理4.后期自己在顶底层铺地网络进行连接如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm?spm=a1z

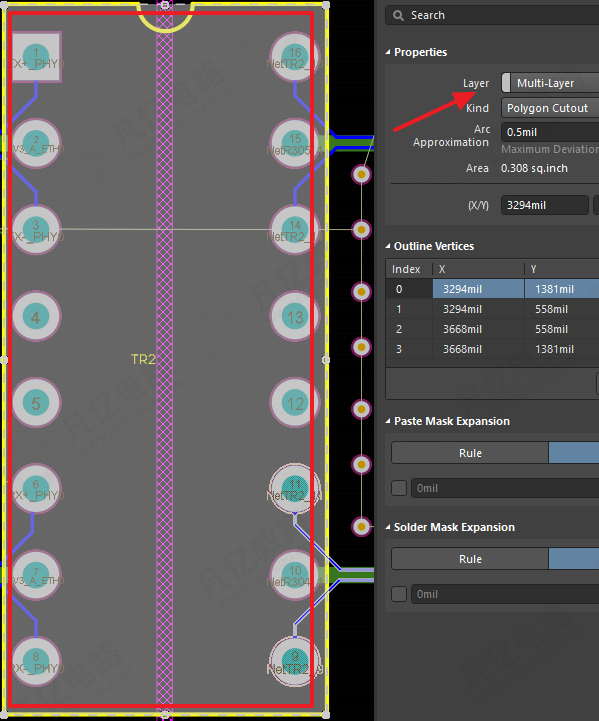

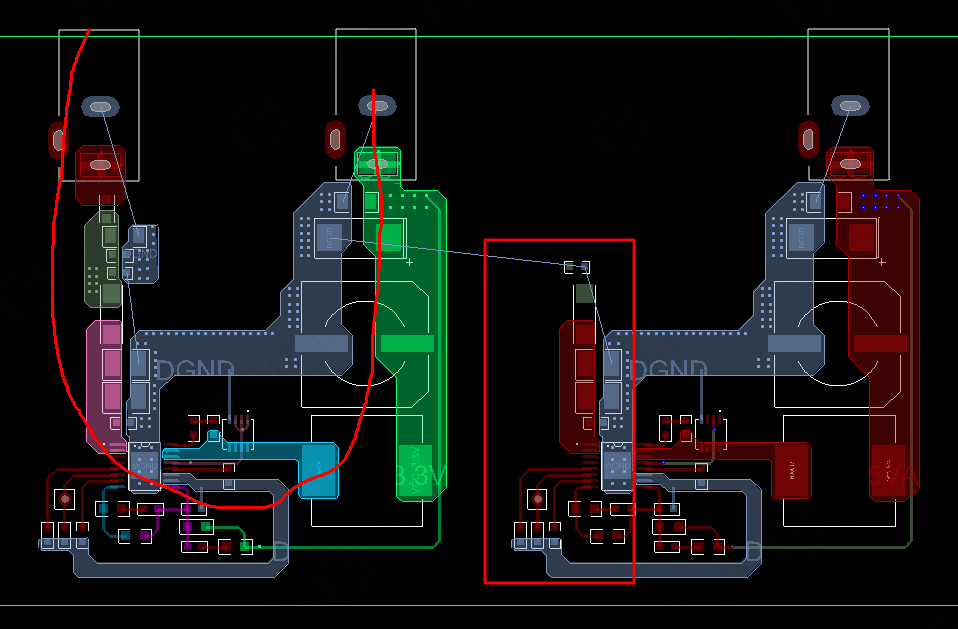

1.变压器下方需要在所有层单独放置铺铜挖空,例如顶层放一个底层再放一个铺铜挖空。2.电源电容的输入输出都需要加粗载流。3.顶底层需要整版铺地铜处理4.TX等长组需要建立xSignals,前后段合并一起等长5.差分对内等长误差要控制在5mil

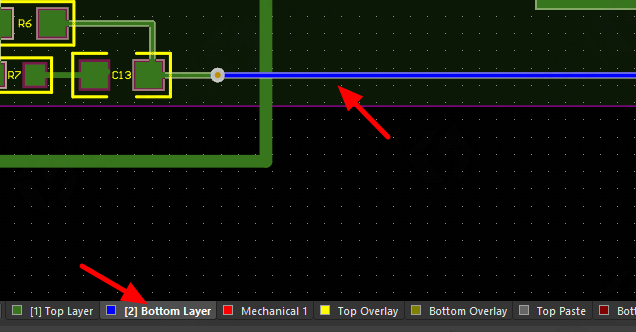

1.应单点接地,只到一个点打孔,所有地网络都连接到芯片散热焊盘下方打孔连接大铜皮。2.下方电路没有电源输入存在开路,最前放电容电源和地没有连接。3.多余打孔,底层没有连接。4.底层没有铺大地铜,底层应该整版铺地铜。5.相邻电感应朝不同方向布

ROOM框导入不需要就进行删除:电感下面不要放置器件,自己整体调整下,可以塞到IC下面去:注意铜皮不要存在直角:电感内部都挖空处理:注意反馈信号加粗8-12MIL:铜皮尽量把焊盘都包裹住:注意整板是铺地铜进行回流,而不是铺电源信号,自己处理

此处不满足载流2.此处存在开路3.输出打孔要打在滤波电容后面5.反馈线要从滤波电容后面取样,走10mil即可6.电感所在层的内部需要挖空处理,背面尽量不要放置器件7.电源网络需要再底层铺铜进行处理,剩下的地方铺地以上评审报告来源于凡亿教育9

1.底层没有铺地铜,导致多处地网路飞线没处理2.多处铺铜没有网络,多处飞线没有连接3.dcdc需要单点接地,地网络没有打孔,应在芯片下方打孔和大地铜连接4.电源没有连接,多处过孔没有网络5.地网络没有连接,6.铺铜、走线避免直角锐角7.走线

1.dcdc布局应尽量一字型或L形布局,第二路dcdc的电源没有连通2.地信号没有连通,底层应整板铺地铜3.dcdc需要保持单点接地,地网络都连接到芯片下方打孔,其他地方gnd网络不打孔。4.没有和其他铜皮连接的孔,电源打孔没有和其他层铜皮

扫码关注

扫码关注