- 全部

- 默认排序

MODE有效折射率结果与Uranus等人的结果非常接近。对于这种对数值网格的微小变化(以及实际制造缺陷)非常敏感的结构,计算损耗则更加困难,并且需要进行一些收敛测试才能找到更准确的结果。收敛测试我们首先将感兴趣的两种模式复制到全局DE

其他类设计软件通常是通过网格来对齐元件、过孔、走线的,嘉立创EDA提供非常方便的对齐功能,如图1所示,可以对选中的元件、过孔、走线等元素实行向上对齐、向下对齐、向左对齐、向右对齐、水平等间距对齐、垂直等间距对齐。1、执行菜单命令“布局-对齐

在PCB设计中,覆铜是极为关键的环节,若是处理不当,很容易直接影响到电路板的性能和功能,按其类型,覆铜可分为网格覆铜和实心覆铜,今天来对比这两个覆铜方式,看看哪个更适合我们的项目。网格覆铜 VS 实心覆铜网格覆铜:优点:提供较好的散热性能:

在电子工程中,覆铜是一种常见的处理方式,用于增强电路板的导电性能和信号完整性,一般来说,腹痛基本上可分为网格覆铜和实心覆铜,若设计电路板该如何选?1、网格覆铜和实心覆铜是什么?网格覆铜:在电路板上使用网格状的铜箔,通常用于地线和电源线。这种

随着半导体集成度越来越高,片上系统越来越复杂,很多电子工程师不得不去学习PCB设计,本文将介绍10条PCB设计黄金法则,且广泛适用于各种PCB项目,下面一起来看看吧!1、选择正确的网格,将其设置并始终使用能够匹配最多元件的网格间距。2、保持

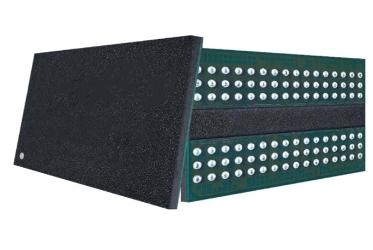

SMART DDR3(L) SDRAM组件与行业广泛兼容,并提供x8和x16配置。这些1.35v(DDR3L)和1.5V(DDR 3)器件采用标准78和96引脚网格阵列封装,时钟速度为1866 Mbps,密度为1Gb、2Gb和4Gb。KTD

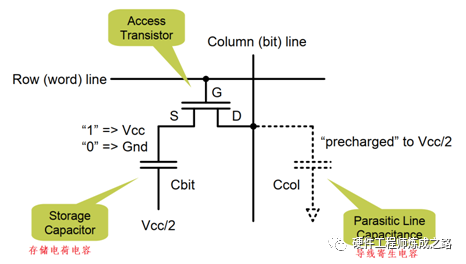

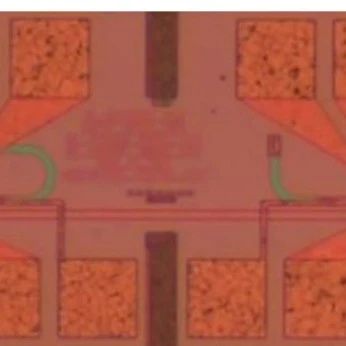

最近想对DDR了解多一点,看标准的时候发现有些概念还是不清楚,比如预充电Precharge是什么?刷新Refresh,又是为什么?要知道这些问题的答案,就需要知道DDR内部存储单元结构,通过查阅资料,总结如下,分享给大家。 DDR SDRAM Bit CellsDDR SDRAM是类似一个网格阵列,

简介元胞自动机(CA)是数学模型,由网格单元组成,每个单元都处于有限的状态之一。每个单元的状态都会根据一组规则在离散的时间步长内更新,这些规则取决于该单元及其相邻单元的状态。从生物过程到计算系统,CA 在各种系统建模中都有应用。惠普实验室(Hewlett Packard Labs)的研究人员最近取得

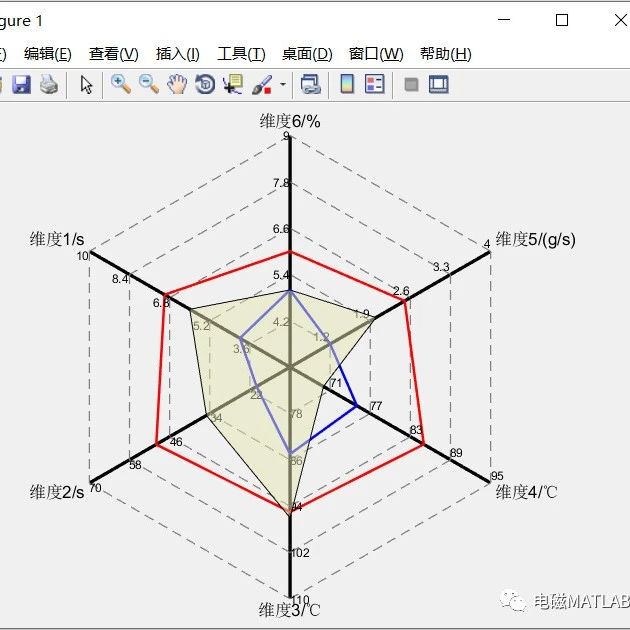

什么是雷达图?雷达图也称为网络图、蜘蛛图、星图、蜘蛛网图,它被认为是一种表现多维数据的图表。它将多个维度的数据量映射到坐标轴上,每一个维度的数据都分别对应一个坐标轴,这些坐标轴以相同的间距沿着径向排列,并且刻度相同。连接各个坐标轴的网格线通常只作为辅助元素,将各个坐标轴上的数据点用线连接起来就形成了

什么是雷达图?雷达图也称为网络图、蜘蛛图、星图、蜘蛛网图,它被认为是一种表现多维数据的图表。它将多个维度的数据量映射到坐标轴上,每一个维度的数据都分别对应一个坐标轴,这些坐标轴以相同的间距沿着径向排列,并且刻度相同。连接各个坐标轴的网格线通常只作为辅助元素,将各个坐标轴上的数据点用线连接起来就形成了

扫码关注

扫码关注