最近想对DDR了解多一点,看标准的时候发现有些概念还是不清楚,比如预充电Precharge是什么?刷新Refresh,又是为什么?要知道这些问题的答案,就需要知道DDR内部存储单元结构,通过查阅资料,总结如下,分享给大家。

DDR SDRAM Bit Cells

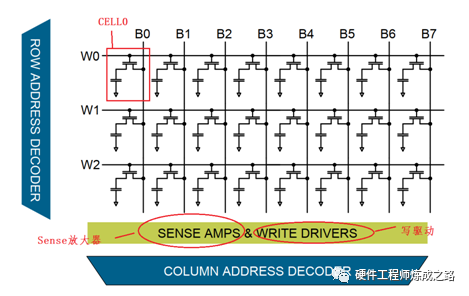

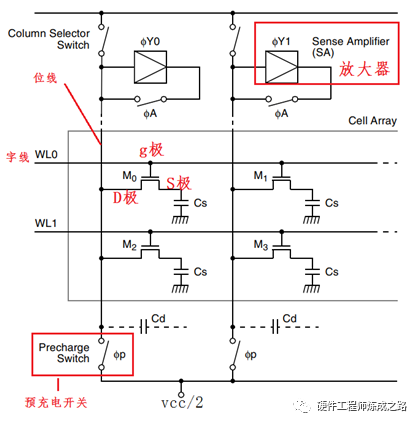

DDR SDRAM是类似一个网格阵列,其中基本存储单元称之为cell。

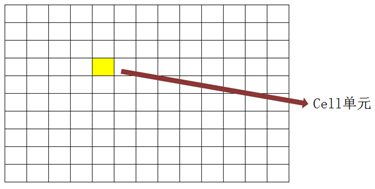

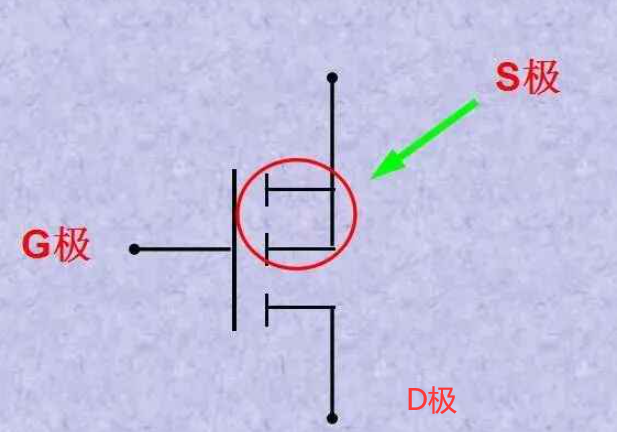

每个Cell包含一个电容Cbit和一个FET管,能个存储一个bit的数据。如下图。Row(word)line称为字线,也就是DDR的行地址线,它连在了FET的g极。通过控制字线电压就可以控制FET的开启与关闭了,也就可以对Cbit电容进行充电或者是放电了。

Cbit里面如果存储有电荷,即S端电压为VCC,那么就是存储的1,否则就是存储的0。

Ccol为寄生电容。

Cell是如何读写的呢?

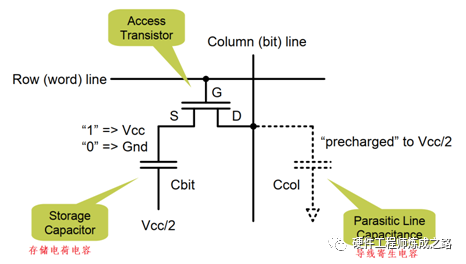

以上图Cell0为例子

读过程

1---首先关闭所有字线,W0,W1…Wn。让所有FET均不导通。

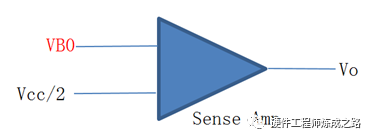

2---然后将位线B0通过预充电开关Precharge(图中未画出)拉到Vcc/2,即VB0=Vcc/2。(这个操作就是预充电Precharge)

3---再断开预充电开关PrechargeSwitch,停止充电。

4---将W0置为高电平Vcc,此时Cell0的FET导通。

如果原来存储的是1,Cbit电压大于VB0,那么Cbit会对字线B0充电,使得VB0>Vcc/2,此时VB0经过放大器SenseAMP后放大电压到VCC电平,即读出1。

如果原来存储的是0,Cbit电压小于VB0,于是字线B0会对Cbit充电,使得VB0,此时VB0经过放大器SenseAMP后电压被拉直GND,即读出0。

写过程

写0

1---首先将位线B0拉低

2---然后将W0拉高,打开FET,Cbit通过B0放电置GND

3---拉低W0,完成写入0

写1

1---首先将位线B0拉高

2---然后将W0拉高,打开FET,Cbit通过B0充电至VCC

3---拉低W0,完成写入1

DDR为什么要刷新

其实了解了Cell结构,这个答案就很清楚了,DDR的数据保存就是通过Cbit电容保存电荷,因为漏电流的存在,如果长时间不操作Cell,那么电荷就会漏光,保存的数据就没有了。

所以为了保存住数据,需要定期对Cell单元里面的数据进行读取,然后再写入,这个过程就叫刷新。

扫码关注

扫码关注

![[电赛F题]OpenMV模板匹配实用教程,8数字同时识别40帧+,源码程序一行一行讲解,包教包会](https://api.fanyedu.com/uploads/image/4c/467e8ec5a8f7051ce168e8033567d6.jpg)