- 全部

- 默认排序

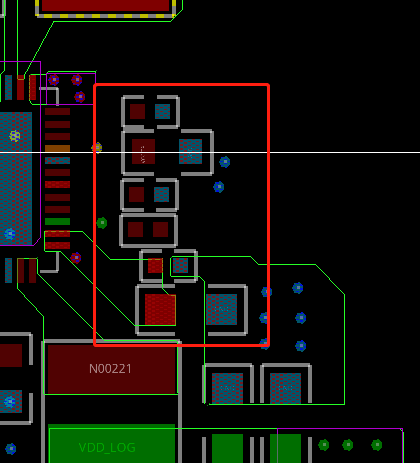

铜皮全部是直角,尽量全部都修改为钝角的:主干道器件摆放需要整体中心对齐:电感当前层内部需要挖空:焊盘出线需要从两长边拉出:电源输入输出对应的地在中间的IC焊盘上打孔过孔,进行单点接地:地直接优化下铺铜连接进来:其他的没什么问题了。以上评审报

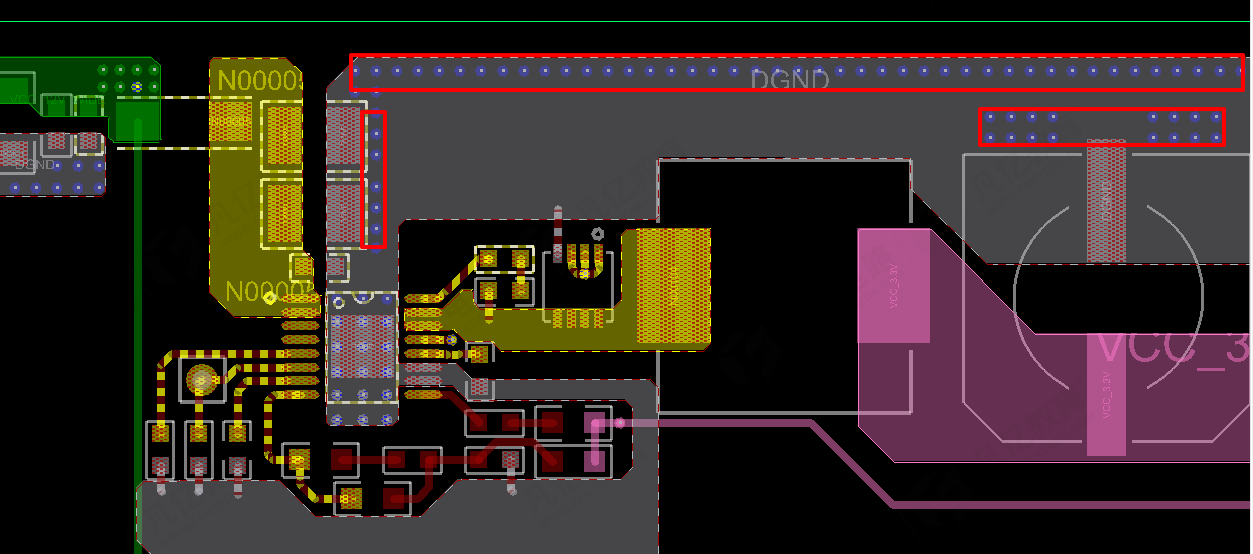

1.dcdc需要单点接地,gnd网络需要连接到一起在芯片下打孔。2.相邻电感不能平行摆放,需要朝不同方向垂直放置。3.下面一路dcdc电源输入需要加粗,加宽载流从第一个器件输入。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了

在PCB设计中,很多电子工程师会将重点集中在敏感元件、电源等,但线缆和接插件的布局布线同样也至关重要,因为它们直接联系到电路板的性能和可靠性,本文将整理总结一些关于线缆和接插件的PCB Layout设计规范,希望对小伙伴们有所帮助。1、PC

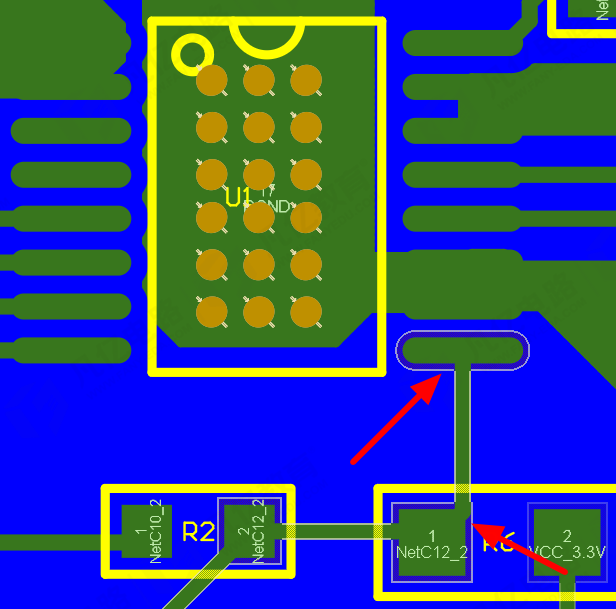

电感底部不能放置器件,以及走线,自己优化吧电感下面的器件塞到芯片底部:布局需要改动。器件并未对齐,并且都干涉了:器件是需要整体的中心对齐放置。上述一致原因的布局问题:布局需要优化,中心对齐好,器件之间不要干涉。DCDC电源主干道的电容是要靠

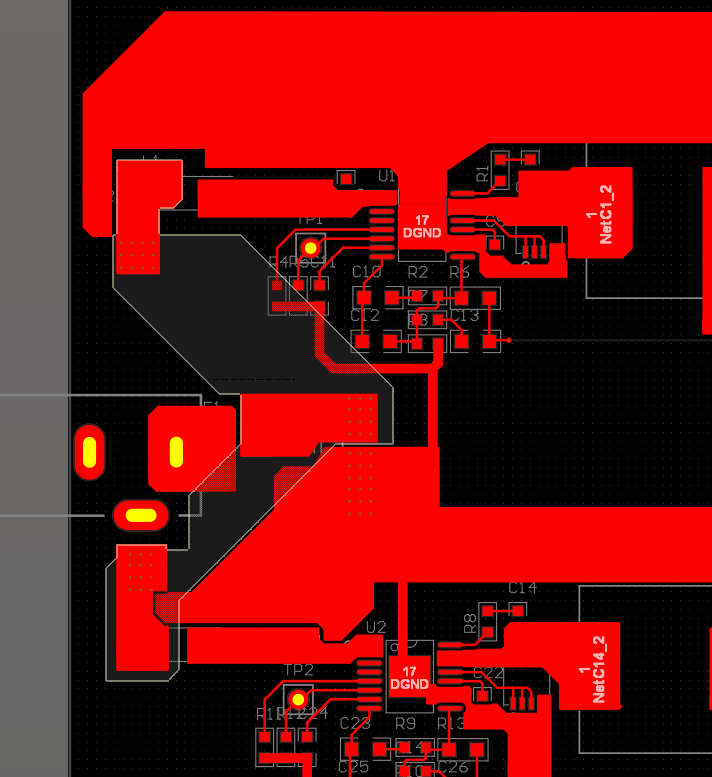

1.焊盘出线应该从焊盘长方向出线,小器件应从焊盘中间出线,避免焊接问题2.地网络铺铜需要加粗和电源一样宽3.两个测试点存在飞线4.相邻大电感应朝不同方向垂直放置5.连接到9号焊盘的走线是反馈信号,不需要加粗以上评审报告来源于凡亿教育90天高

我们在测试过程中往往优先考虑的是被测件(DUT)的状态,而忽略了测试系统的稳定性及可靠性,因此有时候观察到的现象可能会与我们预期的相反,情况变得更为糟糕,这种情况常常令人沮丧,项目进度也会停滞不前。可是如果因为排查出最根本的原因而使情况变得更糟时,距离真相也就不远了!有一次,当我对一块DCDC PC

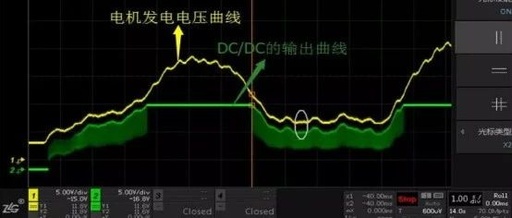

电机控制板的24V电源在给电机供电的同时也通过DCDC输出12V给其他电路供电。在没有电池时,电机发电为控制板供电,而电机的转动并非是匀速的,产生了波动较大的电压,如下图1所示,黄色线为电机反向发电电压,绿色则为MP2451输出的电压。图1 电机发电曲线和DCDC的输出曲线由上图可以看出,电机的发电

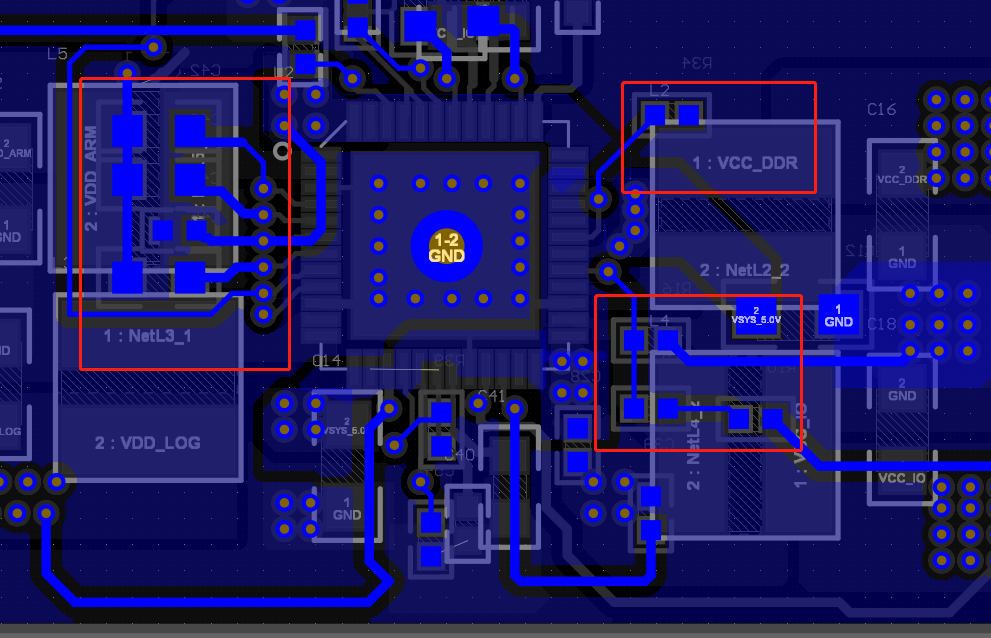

DDR电路简介RK3588 DDR 控制器接口支持 JEDEC SDRAM 标准接口,原理电路16位数据信号如图8-1所示,地址、控制信号如图8-2所示,电源信号如图8-3所示。电路控制器有如下特点:1、兼容 LPDDR4/LPDDR4X/

随着PCB板逐渐高密度化、性能化,导致信号速度的提高和板子尺寸的缩小,信号完整性(SI)和电源完整性(PI)分析变得愈发重要,但调试难度也大大增高。“了解SI&PI仿真?SI&PI仿真有何用?如何做好SI&PI仿真?”等已成为很多工程师需要

注意布局的时候器件整体中心对齐:底层器件也注意对齐:打孔也需要对齐:5V电源走线加粗或者铺铜连接好:铺铜连接之后不需要再走线连接了:注意电感内部当前层需要挖空,放置一个keepout区域:过孔都没有对齐等间距:LDO电路的电源信号也需要加粗

扫码关注

扫码关注