- 全部

- 默认排序

跨时钟域信号的验证要点

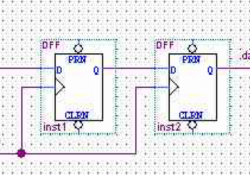

同步时序电路和异步时序电路是数字电路的重要内容,也是小白学习数字电路时重点学习的电路设计课程之一,但如果我们遇见异步时钟域数据同步问题,我们该怎么办?处理跨时钟域问题的核心在于要保证下级时钟对上级数据采样的setup时间或hold时间满足要

很多电子工程师在设计时域电路中,总会遇见很多很多问题,其中之一就是多时域设计中如何处理信号跨时域?这个问题曾劝退很多萌新,今天我们将回答这个问题。不同的时钟域之间信号通信时需要进行同步处理,这样可以防止新时钟域中第一级触发器的亚稳态信号对下

对FPGA工程师来说,可靠性设计是极其重要的,若是没处理好FGPA的触发器,没有满足特定的时序关系,导致FPGA电路不可靠,极有可能产生亚稳态问题,很容易打乱设计步伐,因此,了解FPGA设计的时钟域和亚稳态是很有必要的。一般来说,亚稳态意味

扫码关注

扫码关注