很多电子工程师在设计时域电路中,总会遇见很多很多问题,其中之一就是多时域设计中如何处理信号跨时域?这个问题曾劝退很多萌新,今天我们将回答这个问题。

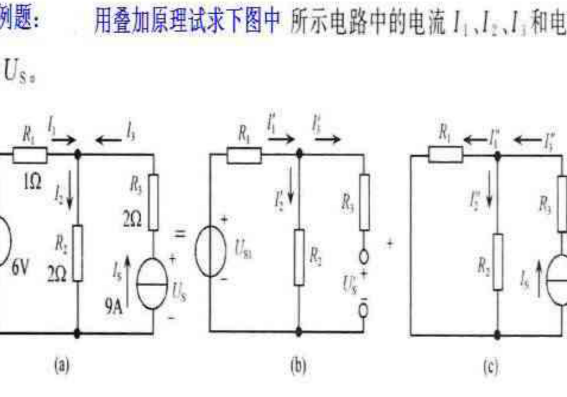

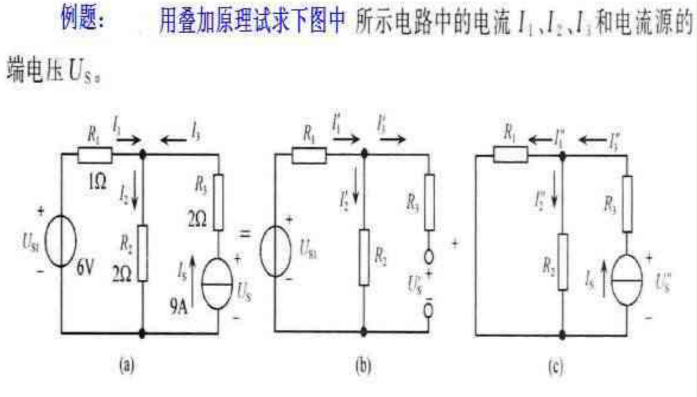

不同的时钟域之间信号通信时需要进行同步处理,这样可以防止新时钟域中第一级触发器的亚稳态信号对下级逻辑造成影响,其中对于单个控制信号可以用两级同步器,如电平、边沿检测和脉冲,对多位信号可以用FIFO,双口RAM,握手信号等。

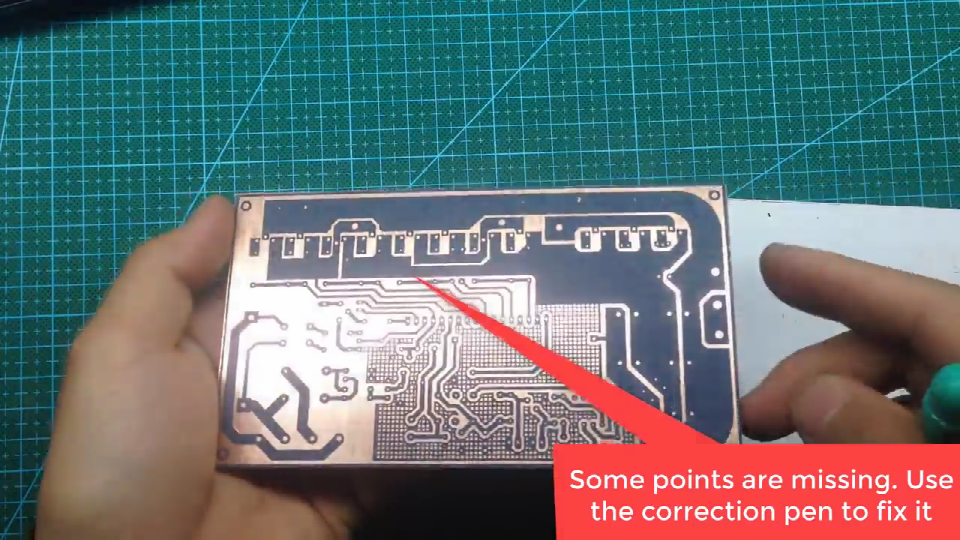

跨时域的信号要经过同步器同步,防止亚稳态传播。例如:时钟域1中的一个信号,要送到时钟域2,那么在这个信号送到时钟域2之前,要先经过时钟域2的同步器同步后,才能进入时钟域2。这个同步器就是两级d触发器,其时钟为时钟域2的时钟。这样做是怕时钟域1中的这个信号,可能不满足时钟域2中触发器的建立保持时间,而产生亚稳态,因为它们之间没有必然关系,是异步的。这样做只能防止亚稳态传播,但不能保证采进来的数据的正确性。所以通常只同步很少位数的信号。比如控制信号,或地址。当同步的是地址时,一般 该地址应采用格雷码,因为格雷码每次只变-一位, 相当于每次只有一个同步器在起作用,这样可以降低出错概率,象异步FIFO的设计中,比较读写地址的大小时,就是用这种方法。如果两个时钟域之间传送大量的数据,可以用异步FIFO来解决问题。

我们可以在跨越Clock Domain时加上一个低电平使能的Lockup Latch以确保Timing能正确无误。

扫码关注

扫码关注