- 全部

- 默认排序

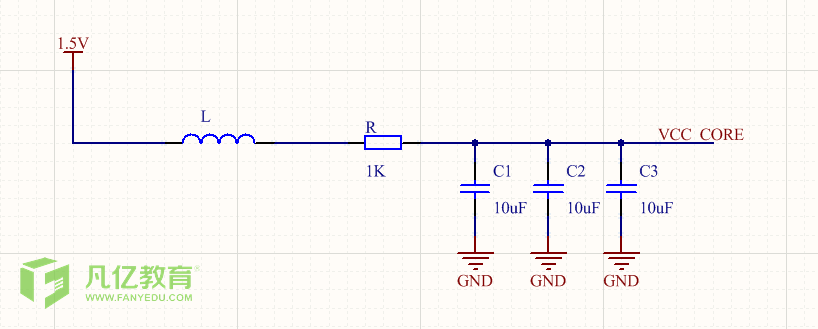

假设下图是一个单板上的PHY芯片的核心电源滤波电路设计。 * 根据这个PHY芯片的资料,这个电源对噪声等方面的干扰特别明显,所以这个设计中不仅采用了,LC滤波电路。还在电感L的后面串联了一个1欧的电阻R。LC滤波电容能滤除高频段噪声。而在这个电路中的这个电阻R不但能衰减高频段噪声,而且能衰减低频段噪声。可以作为一个全频段的衰减器,这种电路设计方法一般用于对噪声特别敏感的电源,如时钟的电源等等。但是单板的长时间运行发现,电阻R经常爆裂。 * 电路设计中选用的电阻R,尺寸是040

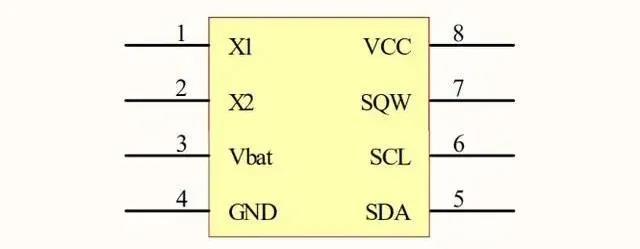

工程师在开发一个电路系统,往往会需要用到中央处理器,比如单片机、FPGA、或者DSP等等;当然一些简单的纯硬件电路项目方案例外,如充电器、热水壶等等。 作为单片机研发设计的项目,它的最小电路工作系统包含电源电路、复位电路、时钟频率电路;其中电源电路与复位电路,相信工程师都非常容易理解与设计。然而时钟频率电路,由于不同的开发项目功能需求不一样,设计的方案选择也不尽相同,很难得到有效的统一设计。

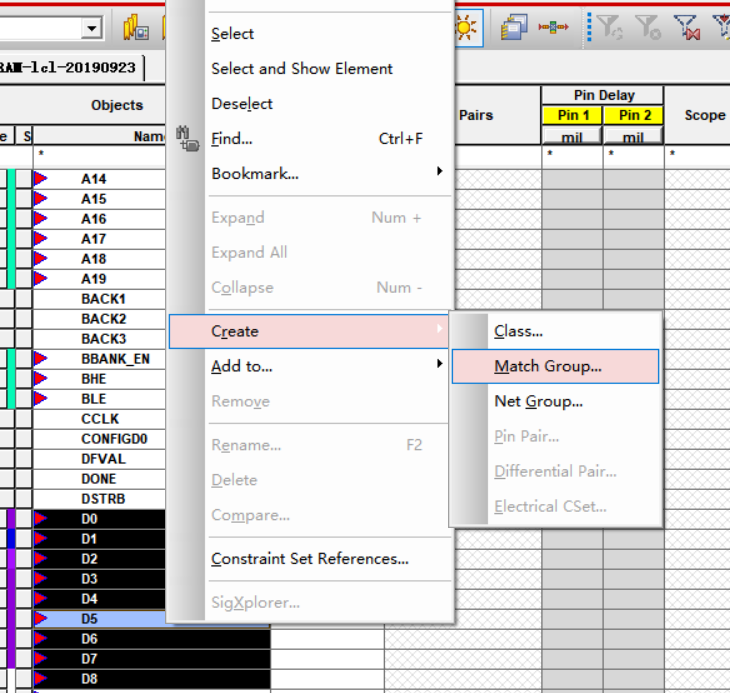

SDRAM信号线等长处理

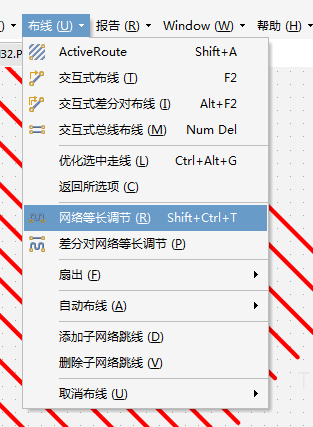

在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如DDRr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

电子设计当中,经常用到差分走线,如USB的D+与D-差分信号,HDMI的数据差分与时钟差分等。虽然现在很多设计者都是在PCB中添加差分,但是还是有许多设计者习惯在PCB中就添加好差分。那么,如何在原理图中添加差分标识呢?

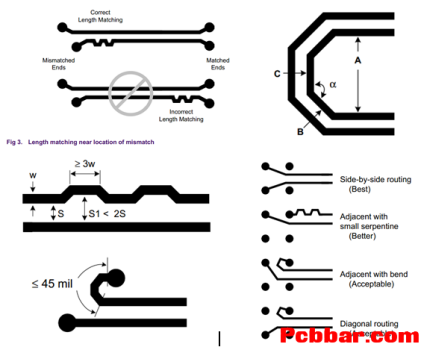

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

至于USB,SATA,PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方时钟包含在数据中发出,数据接收方通过接受到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制

SDRAM芯片引脚介绍

以 Micron公司容量为512Mb(512兆位),规格为8M×16×4的某款 SDRAM为例,介绍 SDRAM的引脚定义。(1) CLK:时钟信号,为输入信号。 SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。(2) (2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有两个,其是关闭时钟以进入省电模式,其二是进入自刷新( SELF REFRESH)状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。在电路设计中需注意,应为C

答:PCB设计中常用的存储器有如下几种:Ø SDRAM,Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与 EDO内存相比速度能提高50%;Ø DDR, Dual Data Rate双倍速率同步动态随机存储器,严格的说DDR应该叫DDR SDRAM,人们习惯称

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

扫码关注

扫码关注