在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

1. 等长设置

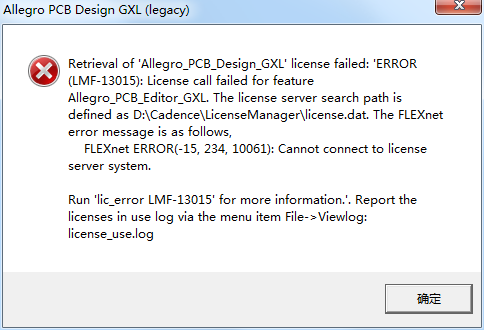

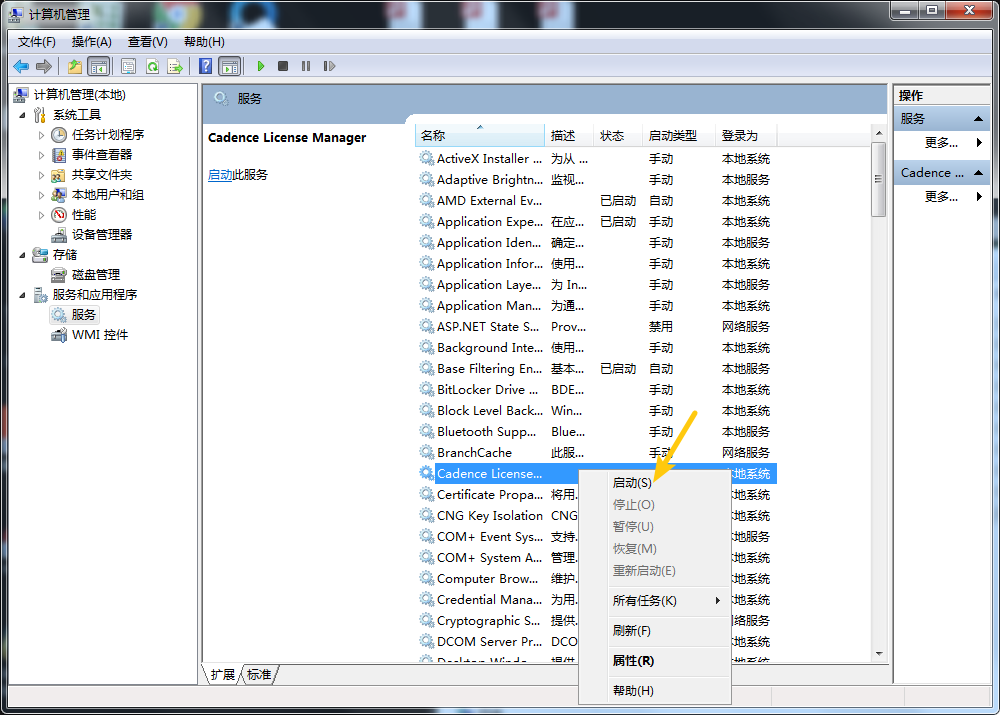

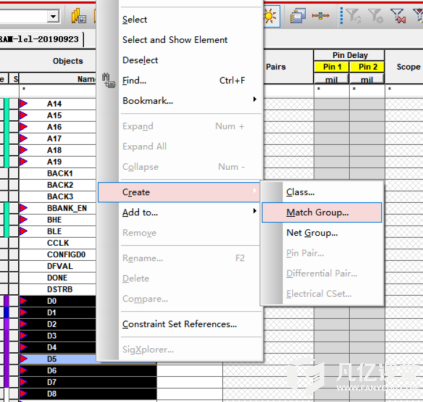

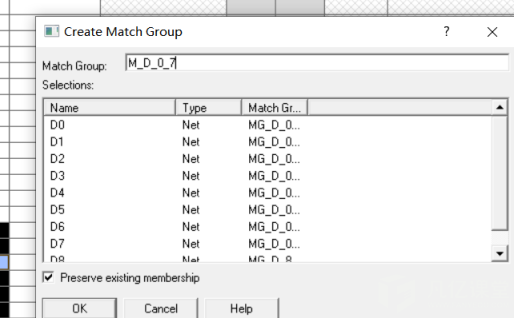

对于SDRAM数据线,直接创建match group。先选择整组网络,单击右键并执行create→match group命令,如图:

弹出create group对话框,在match group文本框中输入名称,如:MG_D_0_7;

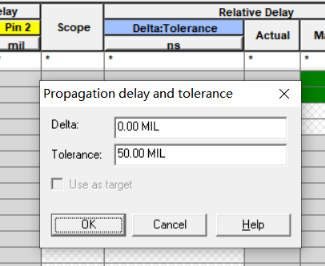

单击ok,成功建立一个match grou:MG_D_0_7,在MG_D_0_7对应的delta:tolerance中单击鼠标右键并选择change命令,弹出propagation delay and tolerance对话框,在delta文本框中输入0,在tolerance文本框中输入50(这里设置的就是误差范围),如图:

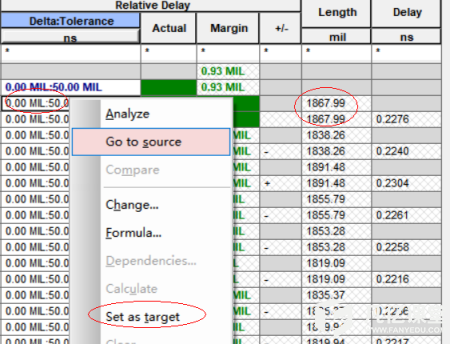

在length中选择最长的一根网络设置为基准线,在对应的delta:tolerance上单击右键单击并选择set as target,将其设置为基准值,如图:

用同样的方法把其他信号线的等长也设置好 。

扫码关注

扫码关注