- 全部

- 默认排序

很多数字芯片工程师工作内容基本上是以搭配不同的基本逻辑门电路组合来实现不同功能需求为主,这非常考验工程师们的逻辑运算能力及空间思维,而这过程必然要涉及到门电路的主要性能及技术指标,所以今天我们将以逻辑门电路的主要性能及技术指标为主角,重点看

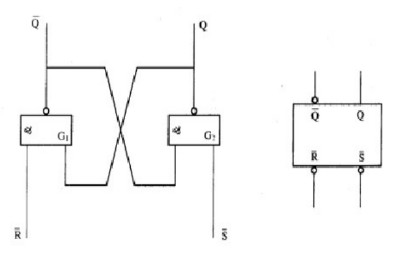

对于数字电路,人们更为熟悉的是逻辑运算门电路,但对于时序电路却鲜为人知,它们的区别在于:前者在某一时刻的输出状态只取决于当时的输入状态;而后者的输出状态不仅与当时的输入有关,还取决于电路原来的状态,其中之一是RS触发器。1、基本RS触发器如

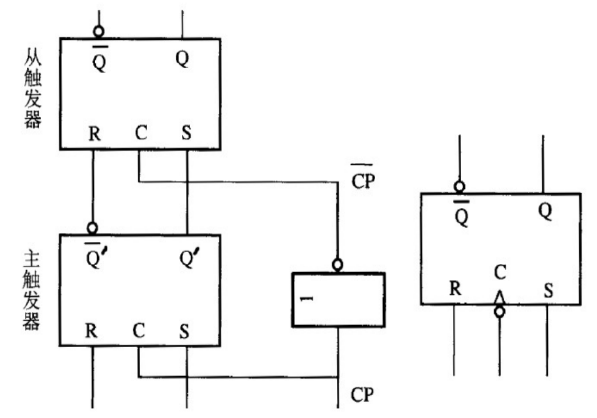

触发器作为数字电路的关键电子器件之一,经常用于逻辑运算等,应用广泛,也是数字芯片工程师需要重点了解并运用的基础知识之一,今天我们将以主从触发器为主,谈谈我们为什么需要主从触发器,它有什么作用?一般来说,触发器的用途之一是构成技术电路,如图所

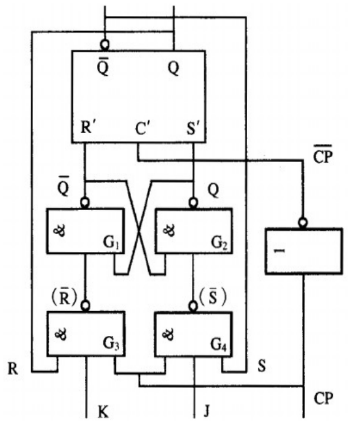

触发器作为数字电路的逻辑运算核心设备,但却鲜为人知,尤其是JK触发器、D触发器和T触发器,很多小白都不知道这几个触发器是干什么用的,有什么用,今天将以这些触发器为主,重点聊聊它们的特点及应用。1、JK触发器将主从式触发器的输出端Q和Q'分别

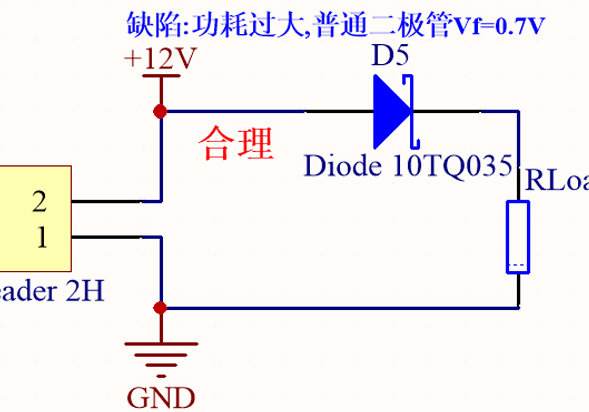

由于文章篇幅所限,该文分为上下两段,欲看上篇文章,可点击右侧《工程师如何处理开关电源的电磁兼容性?(上)》。减小开关电源的内部干扰,实现其自身的电磁兼容性,提高开关电源的稳定性及可靠性,应从以下几个方面入手:注意数字电路与模拟电路单点接地、

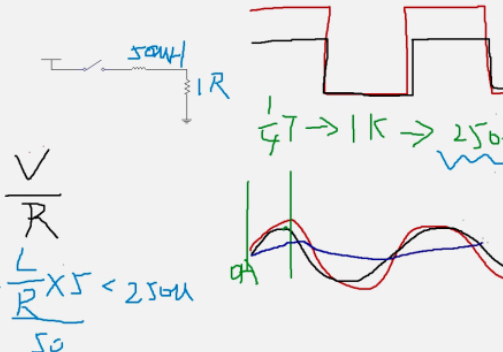

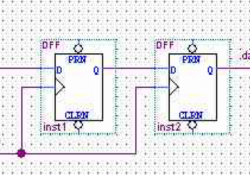

对于电子工程师来说,毛刺是数字电路设计中存在的麻烦问题,它的存在会影响电路工作的稳定性个可靠性,严重时甚至会干扰到整个数字电路系统的误动作和逻辑运行。所以工程师是如何来消除数字电路的毛刺问题?1、在输出端增加D触发器这是工程师普遍使用的传统

同步电路是数字电路中常见的电路设计方法之一,但部分小白对该类电路不甚了解,甚至遇见该类设计是惘然无措,所以本文将重点分析同步电路的设计准则,并分享电路设计的优点。同步电路是指所有电路在同一个公共时钟的上升沿或下降沿的触发下同步地工作。但在实

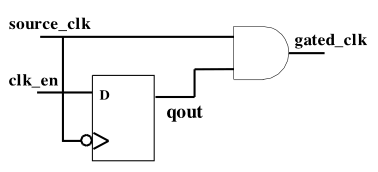

一般来说,很多工程设计都是通过同步时序电路来完成整个系统的设计,由于时钟的特点,时钟在同步电路设计中具有非常重要的作用。目前在电路设计中常见的是种类型主要分为全局时钟、内部逻辑时钟和门控时钟。1、全局时钟全局时钟即同步时钟,它是通过FPGA

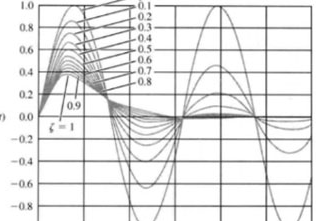

小白在设计数字电路,如同步/异步时序电路时常常会碰到毛刺或者亚稳态的问题,但很多小白对亚稳态问题措手不及,经常搞错电路导致系统崩溃,所以本文将归纳总结,分析数字电路中的亚稳态。在同步电路或异步电路中,如果触发器的setup时间或hold时间

同步时序电路和异步时序电路是数字电路的重要内容,也是小白学习数字电路时重点学习的电路设计课程之一,但如果我们遇见异步时钟域数据同步问题,我们该怎么办?处理跨时钟域问题的核心在于要保证下级时钟对上级数据采样的setup时间或hold时间满足要

扫码关注

扫码关注