- 全部

- 默认排序

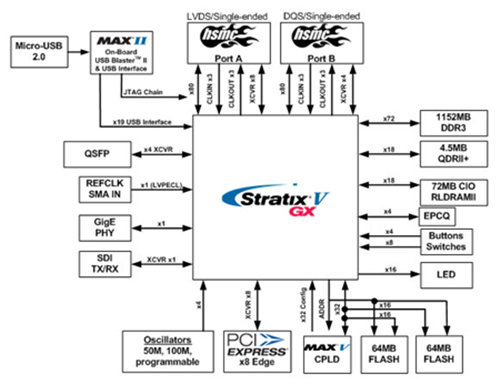

Stratix V FPGA具有1.6 Tbps串行交换能力,采用各种创新技术和前沿28-nm工艺,突破带宽瓶颈,降低了宽带应用的成本和功耗。Stratix V FPGA系列采用TSMC 28nm高性能(HP)工艺进行制造,提供110万逻辑

概述Stratix® V FPGA系列采用TSMC 28nm高性能(HP)工艺进行制造,提供110万逻辑单元(LE)、53-Mbits嵌入式存储器、3,680个18x18乘法器,以及工作在业界最高速率28 Gbps的集成收发器。器件还采用了

Stratix V 摘要Stratix® V FPGA具有1.6 Tbps串行交换能力,采用各种创新技术和前沿28-nm工艺,突破带宽瓶颈,降低了宽带应用的成本和功耗。Stratix V FPGA系列采用TSMC 28nm高性能(HP)工艺

概述Stratix® V采用TSMC高性能28nm HKMG工艺制造,该工艺提供的性能比其它28nm工艺高出35%,这使得它可提供速度最快、功效最高的收发器。这一工艺也使得Stratix V的系统总功耗比前一代Stratix IV低30%。

Stratix V FPGA具有1.6 Tbps串行交换能力,采用各种创新技术和前沿28-nm工艺,突破带宽瓶颈,降低了宽带应用的成本和功耗。Stratix V FPGA的主要性能突破包括:集成66个28Gbps串行收发器(每通道功耗仅20

Stratix V系列FPGA采用新的存储器体系结构,降低延时,高效实现FPGA业界最好的系统性能。Stratix V FPGA为网络设备生产商提供存储器接口解决方案,支持在互联网上迅速有效的传送视频、语音和数据。Stratix V FPG

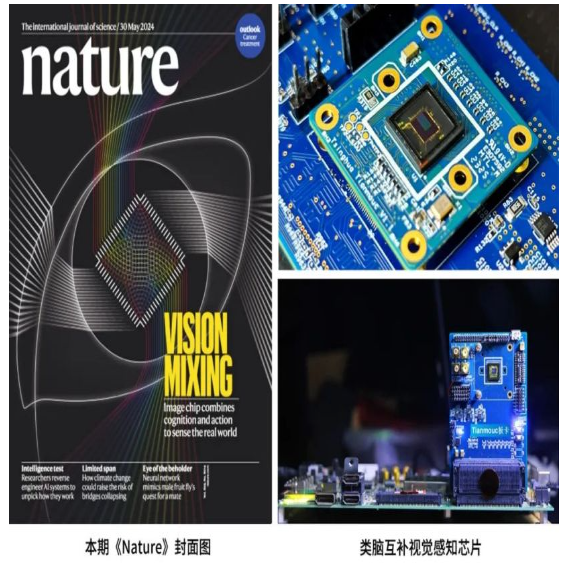

随着时代发展,芯片种类以惊人速度增长,其中之一是视觉感知芯片,可帮助设备或仪器来接收外界信息,分析数据等,然而这些芯片往往有“功耗墙”和“带宽墙”限制,在应对突发事件很容易湿疹、失效或有高延迟等问题,严重影响系统的稳定性和安全性,但这个问题

Agilex™ FPGA 家族基于10纳米技术,可为各种计算密集型和带宽密集型应用提供定制加速和连接,同时提高性能并降低功耗。 Agilex™ FPGA 家族采用异构 3D 系统级封装 (SiP) 技术,集成了首款基于 10 纳米制程技术的

Arria® 10 GT FPGA 采用 20 纳米工艺,收发器性能在芯片到芯片通信中高达 25.78 Gbps,在背板通信中高达 12.5 Gbps,具有多达 115 万个等效逻辑单元。Arria® 10 GT FPGA优势收发器带宽提升

随着5G、物联网和云数据中心对高带宽的巨大需求,400G以太网的关注已经持续了几年。思科、Arista和瞻博网络等供应商正在开发和测试400G以太网技术。作为互连光网络的关键硬件设备,400G收发器将成为行业主流,这一点毫无争议。本文将全面

扫码关注

扫码关注