- 全部

- 默认排序

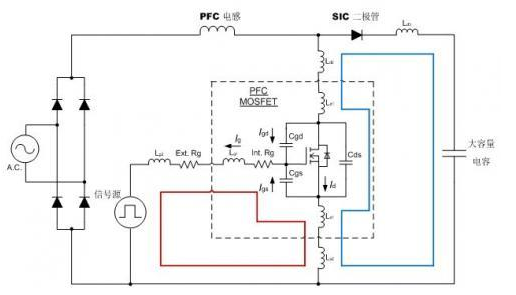

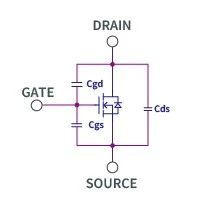

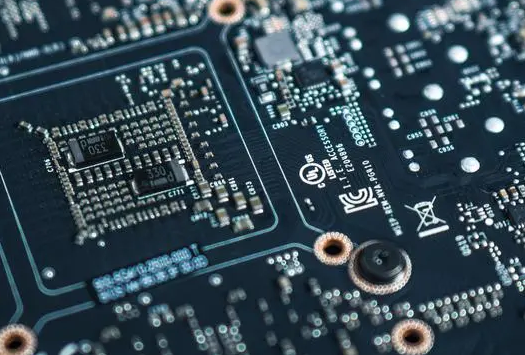

关于MOSFET的寄生容量和温度特性MOSFET的静电容量功率MOSFET在构造上,如图1存在寄生容量。功率MOSFET在构造上,如图1存在寄生容量 MOSFET的G (栅极) 端子和其他的电极间由氧化膜绝缘,DS (漏极、源极) 间形成PN接合,成为内置二极管构造。Cgs, Cgd容量根据氧化膜的

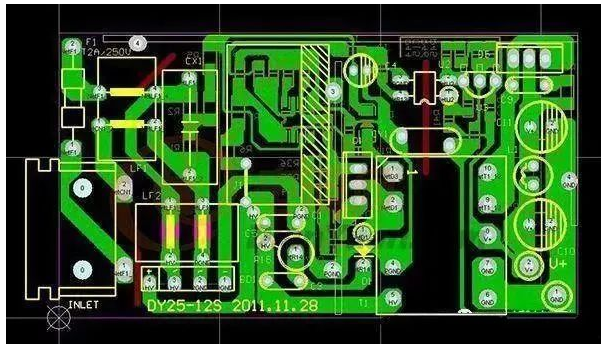

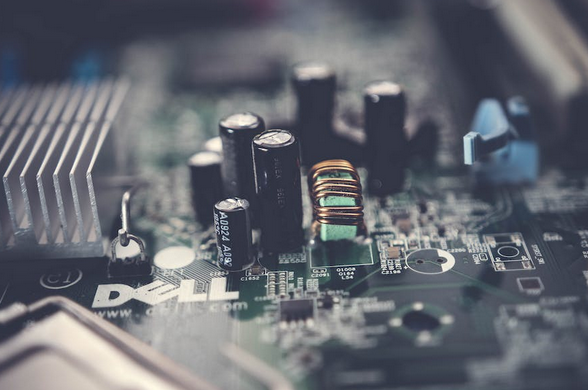

许多设计人员习惯于根据电路模型来思考系统行为。这些模型和电路图在某种程度上都是正确的,但是它们缺少一些确定系统行为的重要信息。电路图中缺少的信息是实际PCB布局的几何形状,它决定了系统中的元素如何相互电和磁耦合。那么,是什么导致真正的PCB

寄生电容在集成电路是无处不在,但若电路设计对电容敏感度低可忽略寄生电容带来的影响,但若电路设计要求芯片速度快或频率高,寄生电容将十分重要,所以若是遇见这个情况,该如何减小寄生电容带来的影响?首先需要知道的是,若模拟电路频率一旦超频率20MH

在高速PCB设计中,寄生电感和噪声问题是常见的挑战,寄生电感是指电流在导体中产生的磁场所形成的电感,将影响信号的传输速度和稳定性,尤其是在高速PCB中更加明显,噪声问题也一样会对信号传输和系统性能产生负面影响。因此,在高速PCB设计中,需要

SiC MOSFET沟槽结构将栅极埋入基体中形成垂直沟道,尽管其工艺复杂,单元一致性比平面结构差。但是,沟槽结构可以增加单元密度,没有JFET效应,寄生电容更小,开关速度快,开关损耗非常低;而且,通过选取合适沟道晶面以及优化设计的结构,可以实现最佳的沟道迁移率,明显降低导通电阻,因此,新一代SiC

同步BUCK降压变化器是应用非常广泛的一种电源结构,其工作频率由早期的低于100KHz,提高到200KHz、300KHz、350KHz、500KHz、1MHz,甚至更高,工作频率的提高带来的好处是电源系统的体积降低,但是,缺点就是开关损耗会增加。功率MOSFET在进一步减小导通电阻、降低导通损耗的同

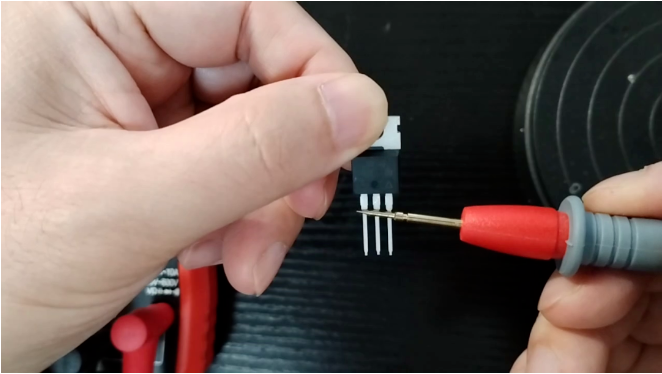

利用场管内部的寄生二极管的单向导通特性对场管的好坏进行判断。第一步 将三个脚进行短接放电这样做的目的对场管内部的寄生电容进行放电,防止有压差,使它内部产生导通,使得测量有误。第二步 测量内部二极管万用表打到二极管档,然后用两个表笔对这个 M

在高频电路设计中,寄生电容的存在是很重要的,它是指在电路中不期望存在的电容,通常是由电路元件之间的绝缘层、导线、接头等产生,它的存在会导致电路的频率响应、增益和相位等特征发生变化,甚至无法正常工作,所以降低RF电容的寄生电容是很有必要的。1

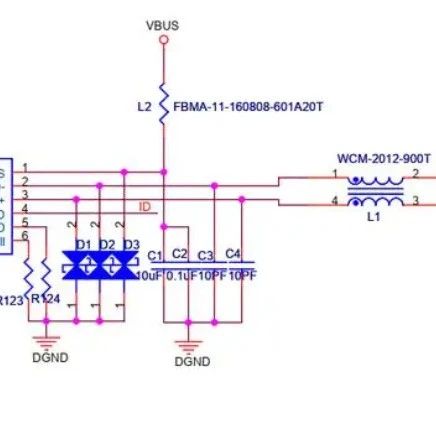

USB接口的EMC设计

在提到干扰对USB的影响时,差分数据传输与简单的同轴电缆相比具有很大的优势。在感性干扰效应(磁场)情况下,导线的绞合可以弥补干扰效应。●USB控制器的输入/输出不是完全对称的,因此USB信号显示出共模干扰。●Layout与HF/EMC不兼容,寄生电容和缺少波阻匹配会产生共模干扰。●电路设计(USB滤

扫码关注

扫码关注