- 全部

- 默认排序

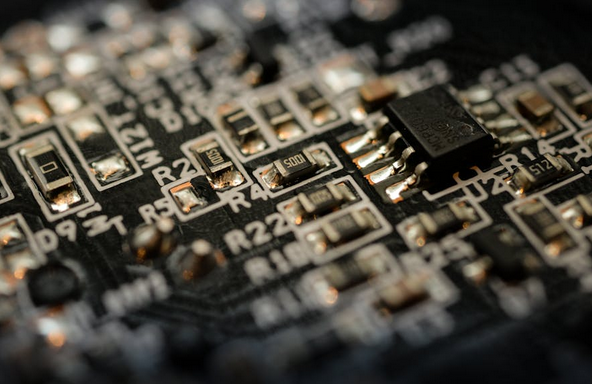

在PCB设计中总会遇见各种各样的问题,其中之一是走线遇到分叉,若不好好处理分叉问题,将降低电路板的可靠性和电磁兼容性,那么如何处理?1、确定分叉点的位置首先,明确分叉点处的具体需求和限制,如信号类型、频率、电流大小等。评估分叉点周围的空间布

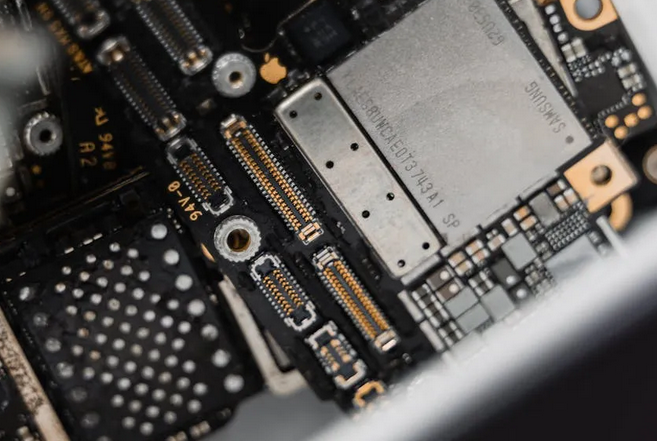

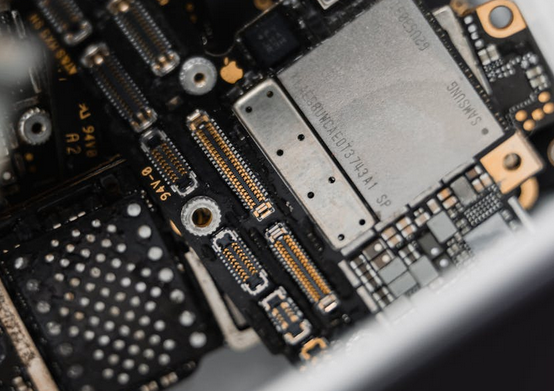

BGA(Ball Grid Array)封装芯片的特点之一是拥有高密度引脚布局,这种特点在维修及更换过程中影响很大,特别是植锡环节,那么有没有一些方法可以提高植锡概率?1、准备工作涂抹适量助焊膏于IC表面。使用电烙铁清除残留焊锡,避免使用吸

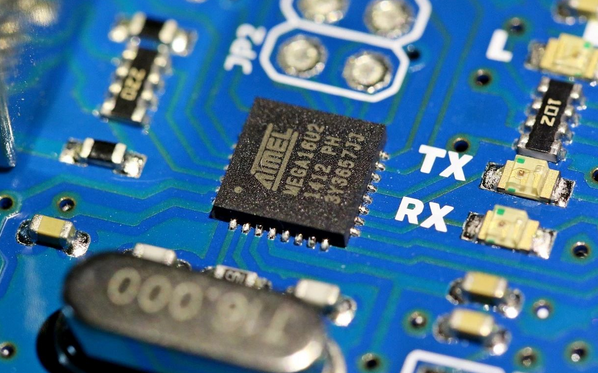

随着时代发展,芯片逐渐高密度化、高性能化,随之而来是愈发严重的电磁干扰问题,对电子工程师来说,做好电磁兼容性(EMC)设计是很有必要的,而EMC设计离不开去耦电容的配置,那么如何配置?1、电源入口大容值电解电容在电源输入端直接跨接一个10u

在高性能电子设备中,散热、噪声等问题往往是电子工程师最为头痛的首要问题,若是处理不当,很容易影响系统稳定性和可靠性,缩短其使用寿命,尤其是采用PCBN(聚晶立方氮化硼)基板或类似高性能材料制成的印制板(PCB),那么如何针对PCBN做好散热

电源效率测试

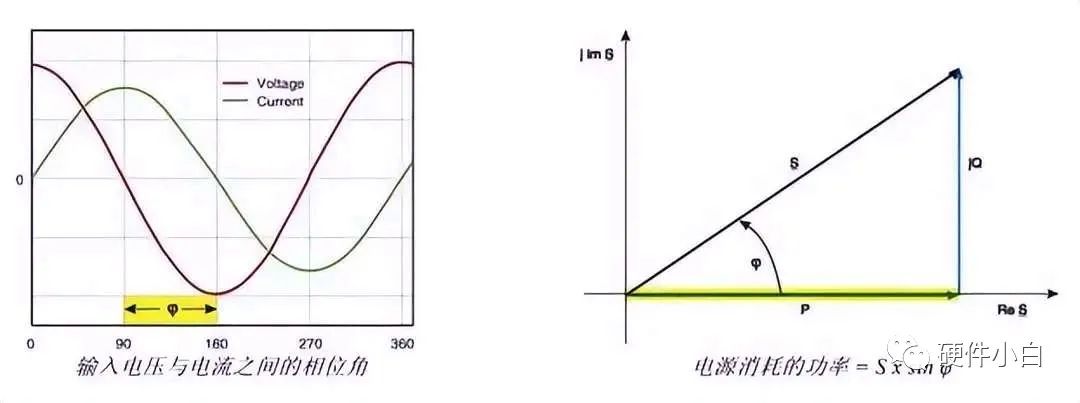

效率是电源测试中十分常见的测试项,高效的电源表现是众多厂家一直追求的目标。在芯片的规格书中,通常都会提供几种常见的输入输出应用下的效率曲线。当实际的应用范围与规格书上不同,或者在demo板的基础上我们进行了其它改动的时候,就需要重新进行效率测试。今天,就给大家详细讲一讲如何进行效率测试,以及相关注意

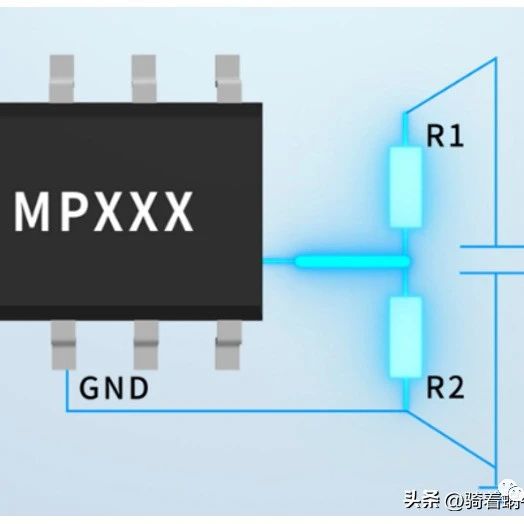

在 DC/DC 变换器中,反馈 (FB) 分压电阻的规格常给设计人员带来各种设计挑战,例如如何确定所需的电阻或调节参数(如输出电压、上分压电阻或下分压电阻)。 图 1 显示了 FB 上/下分压电阻的各种幅度组合。图 1:FB 上/下分压电阻的各种幅度组合本文将探讨 FB 分压电阻的设计规范,包括待机

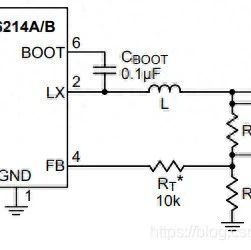

如下图为典型的DCDC电路:芯片是台湾省立琦科技的。上图为DCDC典型应用电路,CIN为输入滤波电容,CBOOT是上管驱动“自举”电容,L是储能电感,R1和R2是反馈电阻,CFF是前馈电容,COUT是输出滤波电容,RT是内部运放补偿器件。一、理论分析没有前馈电容如果没有前馈电容,内部补偿DC-DC转

在手工焊接时,总会遇到五花八门的问题,其中之一是要焊接有磁性的元件,如电感器、变压器等,这些磁性元件的吸引力不仅容易导致元件位置偏移,还可能吸附微小金属碎屑,影响焊接质量及电路性能,所以如何应对?1、预先固定元件在焊接前,使用镊子或专用夹具

在PCB设计中,链路设计的存在可以确保信号完整性和系统稳定性,优秀的链路设计不仅能减少信号衰减、串扰和反射,也能提升整体电路的性能和可靠性,本文将针对单端/差分信号谈谈其链路设计。1、单端信号的链路设计要点垂直布线:尽量使所有走线相互垂直,

元器件的防尘防水性能测试是评估其在恶劣环境条件下可靠性的关键环节。以下是关于防尘防水性能测试的介绍,包括测试标准、方法和重要性。一、测试标准1. IP等级(Ingress Protection Rating):- IP等级是国际电工委员会(

扫码关注

扫码关注