在PCB设计中,链路设计的存在可以确保信号完整性和系统稳定性,优秀的链路设计不仅能减少信号衰减、串扰和反射,也能提升整体电路的性能和可靠性,本文将针对单端/差分信号谈谈其链路设计。

1、单端信号的链路设计要点

垂直布线:尽量使所有走线相互垂直,减少平行走线以减少耦合干扰。

增大线间距:增加走线之间的间距,降低串扰效应。

优化层间距离:减小走线到邻近电源/地层之间的距离,增强屏蔽效果,降低噪声。

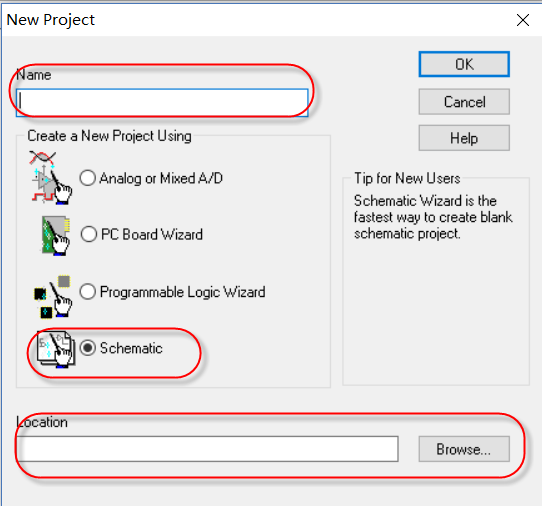

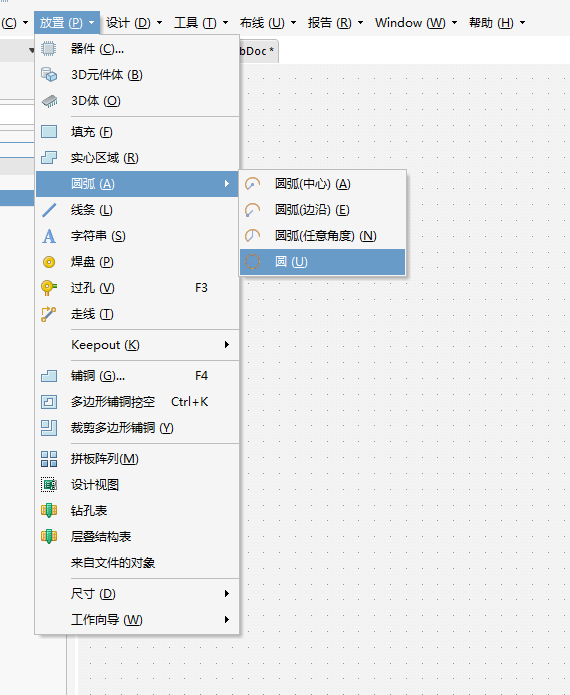

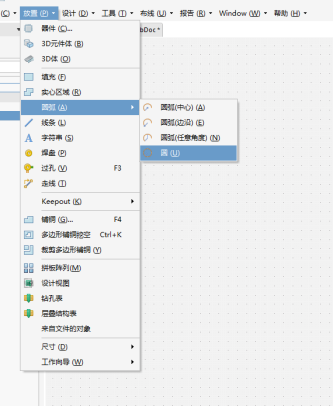

时钟线设计:时钟线保持笔直,避免不必要的弯折,弯折处使用圆弧过渡;减少换层,避免过孔,以维持阻抗连续性。

参考层配置:时钟线最外层紧邻地层,内层时钟线应被两个参考层包裹,提供良好屏蔽。

2、差分信号的链路设计要点

差分对间距:差分对间的间距应大于对内间距的2倍,以减少外部干扰。

对内间距与参考层距离:对内间距等于到参考层距离的3倍,确保差分信号的平衡性。

保持间距一致:差分对内的间距尽可能保持不变,以维持稳定的差分阻抗。

最小化偏差与相位差:确保差分线对内的偏差和相位差最小,提升信号质量。

避免过孔:尽量减少差分线上使用过孔,以免破坏差分信号的完整性。

本文凡亿教育原创文章,转载请注明来源!

扫码关注

扫码关注