- 全部

- 默认排序

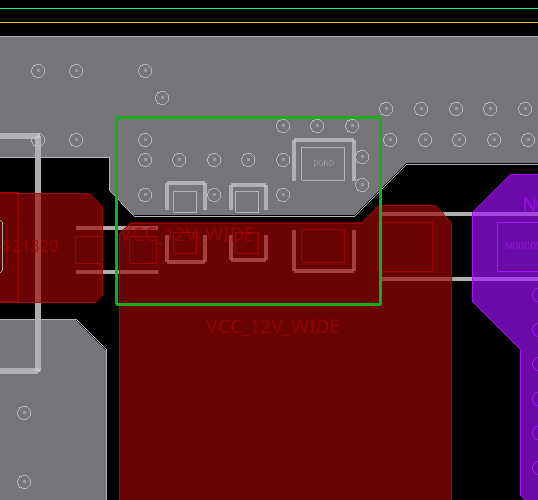

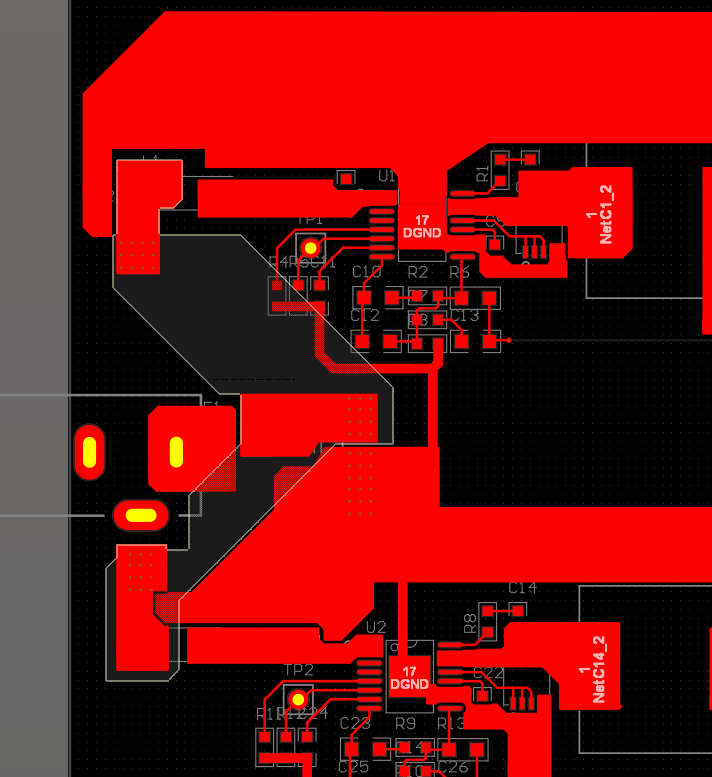

看下原理图此处三个电容位置是否有问题:看下哪个电容才是输入主干道上的电容,重新理解清楚再去放置。输入主干道上的电容是先大后小,放置有问题,自己去修改:电感当前层内部注意挖空:注意主干道电源不要打那么多孔,如果是输入就打第一个输入口;如果是输

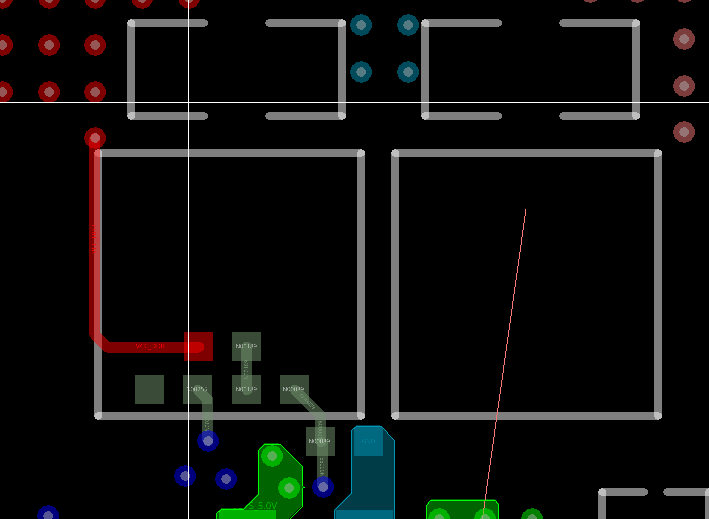

注意电感底部不要放置器件以及走线,需要重新优化下底层的布局以及布线:电感注意当前层内部挖空:电源输出对应的GND打孔数量一一对应上:此处顶层完全可以走线,不用打孔了:多处上述问题,自己去修改下。LDO信号也是需要加粗满足载流大小,看下具体大

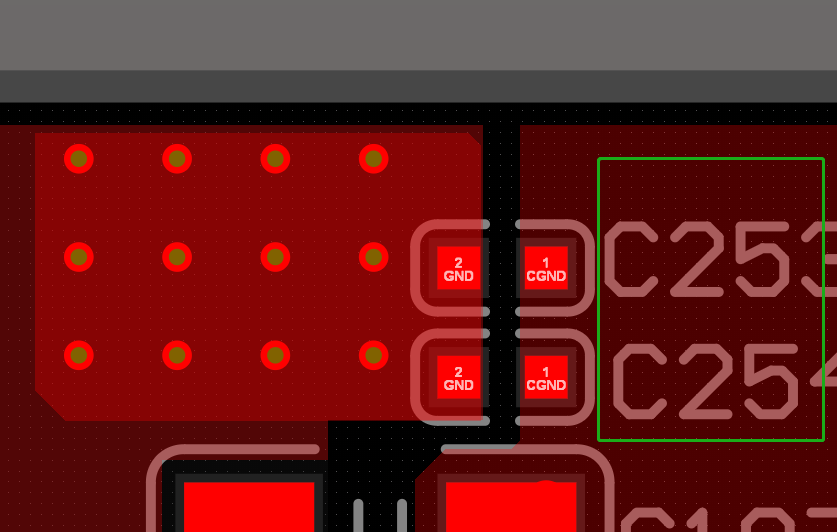

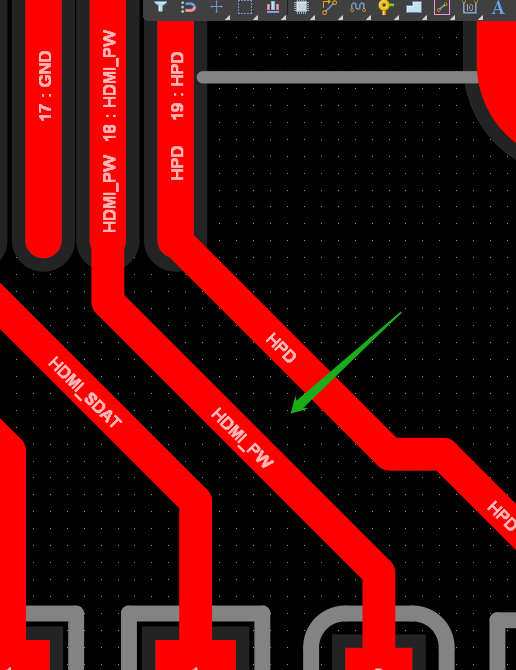

跨接器件两边多打点回流地过孔进行回流:电源地跟机壳地之间至少满足2MM间距:从焊盘拉差分走线需要保持耦合,优化下:差分间距都不一样了,没保持耦合,注意修改,重新走差分线:不要出现直角:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审

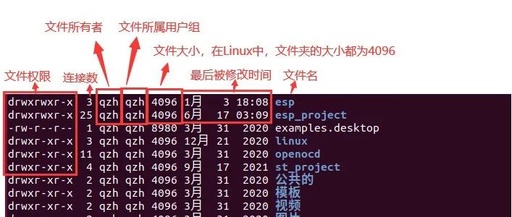

嵌入式 Linux入 门第二课, linux 文件系统、文件类型及权限管理。...... 矜辰所致前言一、Linux 文件属性1.1 Linux 文件类型1.2 Linux 文件权限及修改二、Linux 用户系统2.1 Linux 的用户2.2 Linux 的用户组2.3 文件归属者修改命令三、Li

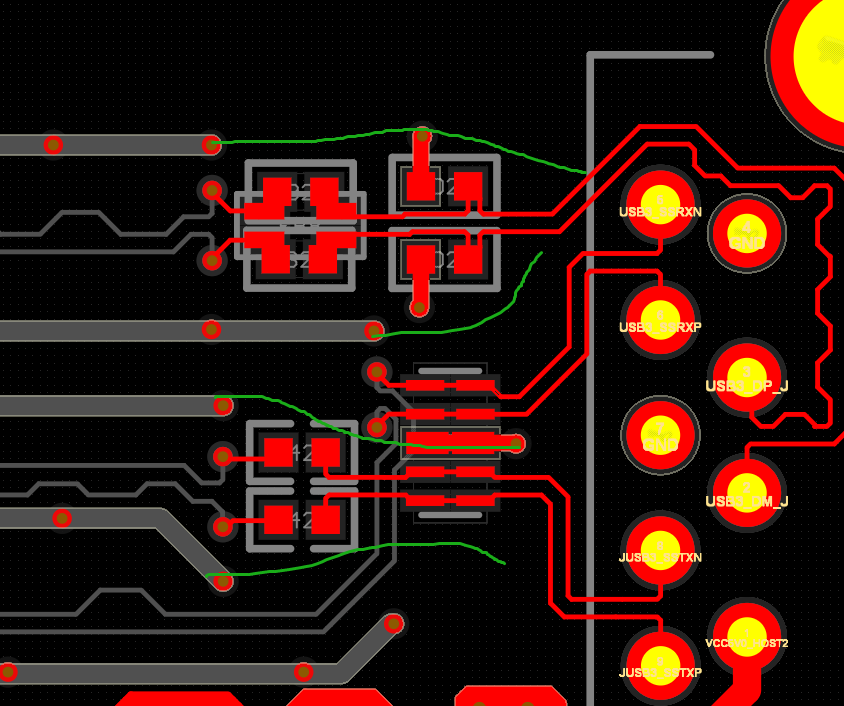

电源管脚加粗走线:注意焊盘扇孔尽量从中心拉直出去扇孔:电源管脚加粗:注意组跟组等长误差是10MIL,不满足 自己修改下:组内误差满足 组跟组不满足。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接

差分走线包地尽量包全:此处扇孔重新优化下:此处连接两个过孔一起连接上,不然另一个过孔没有用:CC1 CC2信号需要加粗走线:此处差分走线完全不耦合 ,不合格:差分对内等长注意需要符合规范:好多差分走线以及对内等长不符合规范,都需要修改。以上

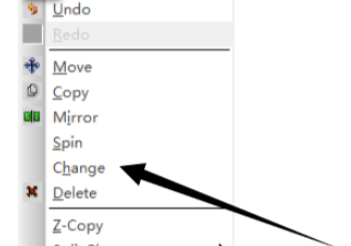

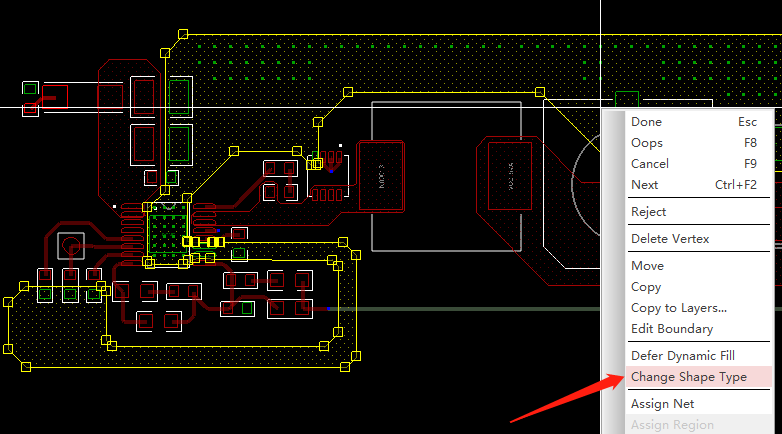

Allegro是一款常用于电路设计和PCB布局的EDA(电子设计自动化)软件,可以用于设计电路图和生成PCB布局。因此很多电子工程师经常使用Allegro来画板子,但在使用过程中有很多问题,其中之一是如何批量修改某网络的线宽?1、打开All

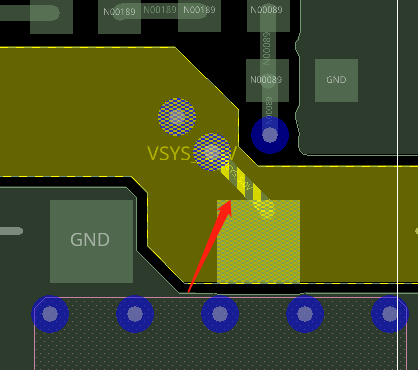

复用后的铜皮把他修改为动态铜皮这里应该打孔铺铜拉线到下面电感垂直摆放最好铺一下整版铜LDO没什么问题以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.tao

铜皮全部是直角,尽量全部都修改为钝角的:主干道器件摆放需要整体中心对齐:电感当前层内部需要挖空:焊盘出线需要从两长边拉出:电源输入输出对应的地在中间的IC焊盘上打孔过孔,进行单点接地:地直接优化下铺铜连接进来:其他的没什么问题了。以上评审报

此处已经铺铜就不用再走线连接:电感内部的当前层挖空处理:其他的也一样,自己去修改。器件就近放,不要路径那么长:此处一个孔是否满足载流,可以多打一个:都看下LDO电路的信号线宽是否满足载流,不满足的出焊盘之后加粗宽度:这边也一致:其他的没什么

扫码关注

扫码关注