- 全部

- 默认排序

LVDS原理及布板技巧

LVDS: 低电压差分信号LVDS(Low Voltage Differential Signal)即低电压差分信号。LVDS的特点是电流驱动模式 电压摆幅350mV加载在100Ω电阻上。其中发送端是一个3.5mA的电流源,产生的3.5mA

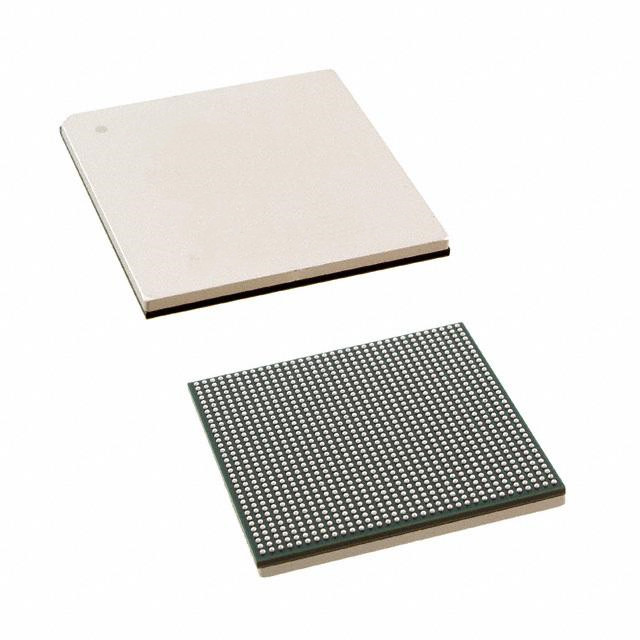

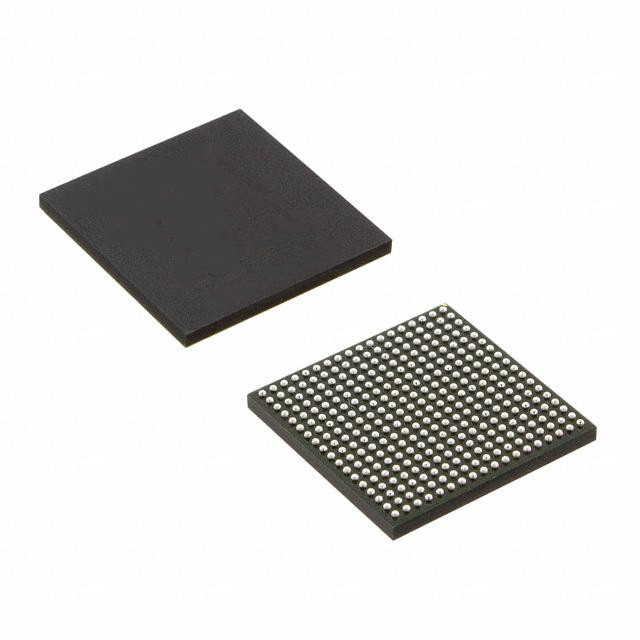

介绍Artix®-7 FPGA能够在多个方面实现更高的性价比,这些方面包括逻辑、信号处理、嵌入式内存、LVDS I/O、内存接口,以及收发器。Artix-7 FPGA非常适合用于需要高端功能的成本敏感型应用。Artix-7 FPGA提供其他

描述Artix-7 FPGA能够在多个方面实现更高的性价比,这些方面包括逻辑、信号处理、嵌入式内存、LVDS I/O、内存接口,以及收发器。Artix-7 FPGA非常适合用于需要高端功能的成本敏感型应用。功能亮点6.6Gb/s收发器,实现

【FPGA】XC7A35T-1FTG256I、XC7A35T-2FTG256C、XC7A200T-2FBG676I基本介绍Artix-7 FPGA能够在多个方面实现更高的性价比,这些方面包括逻辑、信号处理、嵌入式内存、LVDS I/O、内存

概述1、ADCLK846BCPZ 是一个1.2GHz LVDS/CMOS,扇出缓冲区优化的低抖动和低功耗操作。可能的配置范围从6 LVDS到12 CMOS输出,包括LVDS和CMOS输出的组合。两条控制线用于确定输出的固定块是LVDS还是

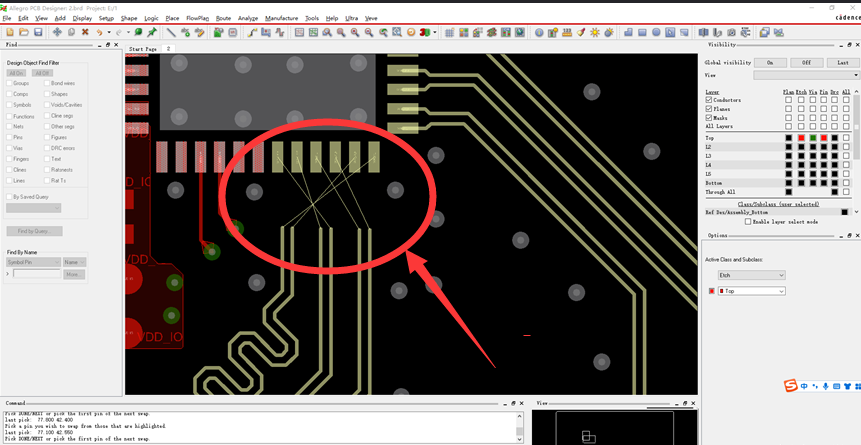

很多电子初学者在使用Cadence Allegro进行Layout设计时,会有一些mipi或LVDS等差分走线,在走线时可能为了匹配线序,导致信号网络的走线是交叉,这样做不仅费时费力,还会影响信号质量,那么如何将这些器件的引脚交换过来?如图

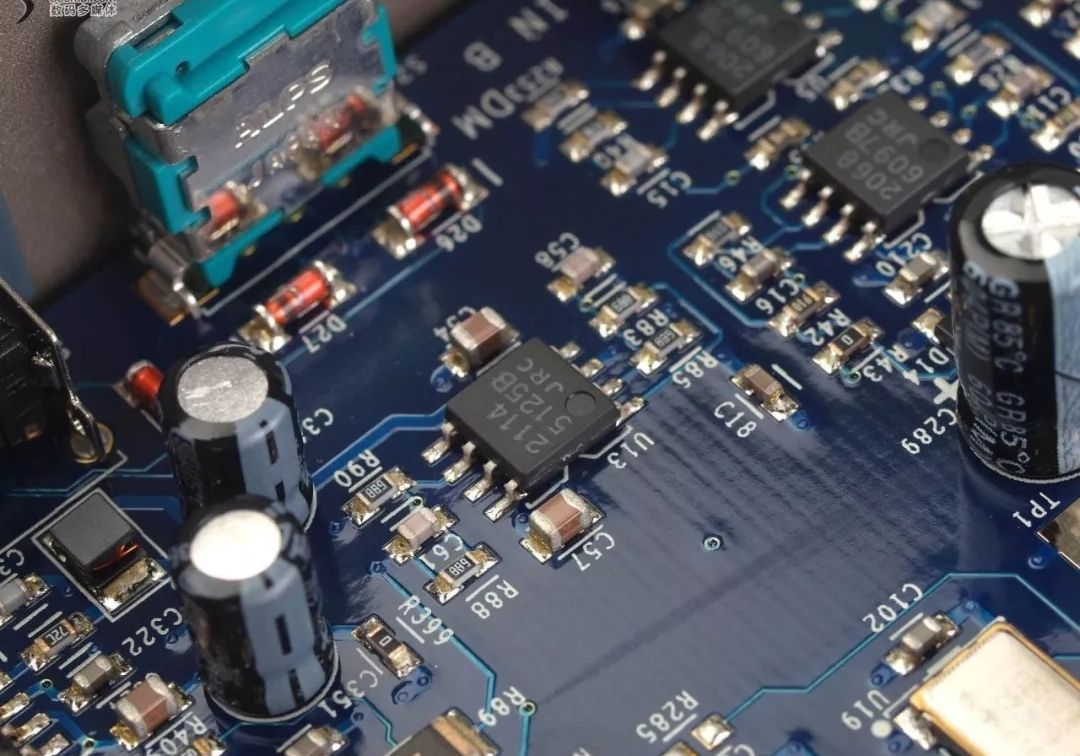

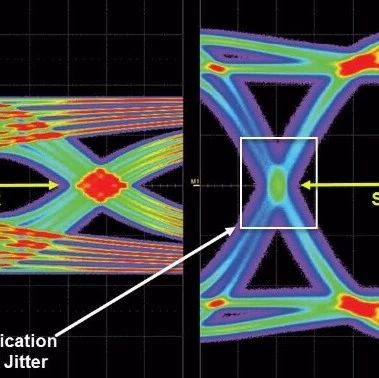

在设计PCB时,经常会遇到高速差分线,比如USB、HDMI、LVDS、以太网等等,高速差分线不仅要求信号线的正端和负端信号线宽及线间距保持一致,还需要对差分信号线进行阻抗控制。控制差分信号线的阻抗,对高速数字信号的完整性是非常重要的,因为差分阻抗影响差分信号的眼图、信号带宽、信号抖动和信号线上的干扰

随着数据传输速率越来越高,现在计算机系统中的数据传输接口基本上都串行化了,像USB、PCIe、SATA、DP等等外部总线将并行总线挤压到只剩下内存总线这个最后的堡垒。当然,就算是并行传输总线最后的倔强DDR也在不断吸收SERDES上的技术来提升自己,尤其是均衡器(Equalization,EQ)技术

【摘要】PECL/CML/LVDS这几种高速差分接口是我们工程中常用接口,本文将从接口起源、输出内部结构、输入内部接口三方面分别阐述各自原理。下一篇文章将重点阐述这几种高速接口之间的互联硬件设计。1. 差分信号接口介绍1.1 PECL 接口PEL 是有 ECL 标准发展而来,在 PECL 电路中省去

我有几个问题,想请教下。

我有几个问题,想请教下。fpga的,普通io是什么电平标准呢ecl.还是cml,LVDS,那种标准。因为,实际高速设计时需要通过电平标准,来设计匹配电路但我没在手册上,看到过相关描述

扫码关注

扫码关注