- 全部

- 默认排序

熟练掌握电子电路设计技术,是每位电子工程师都要学会的任务,不会电路设计的人就无法成为电子工程师,然而很多人在成为电子工程师都会困惑究竟要设计怎么样的电路,今天就讲讲这个话题,希望这篇文章能够对小伙伴们有所帮助。首先,究竟要设计什么样的电路?

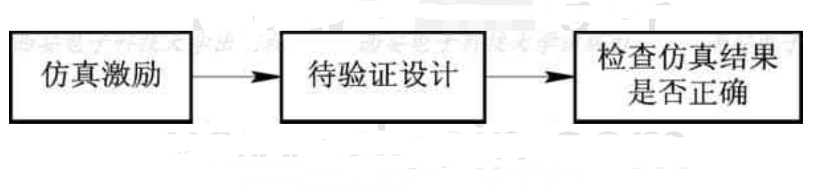

仿真模拟是IC设计的重要环节,但很多小白初学电子设计总会跳过仿真直接测试运行,导致电路崩溃失败,所以有必要进行仿真吗?仿真有什么用吗?如何做好仿真?接下来看看吧!如图所示,仿真是IC功能验证的主要手段,该图是仿真的基本原理。除了功能检查,用

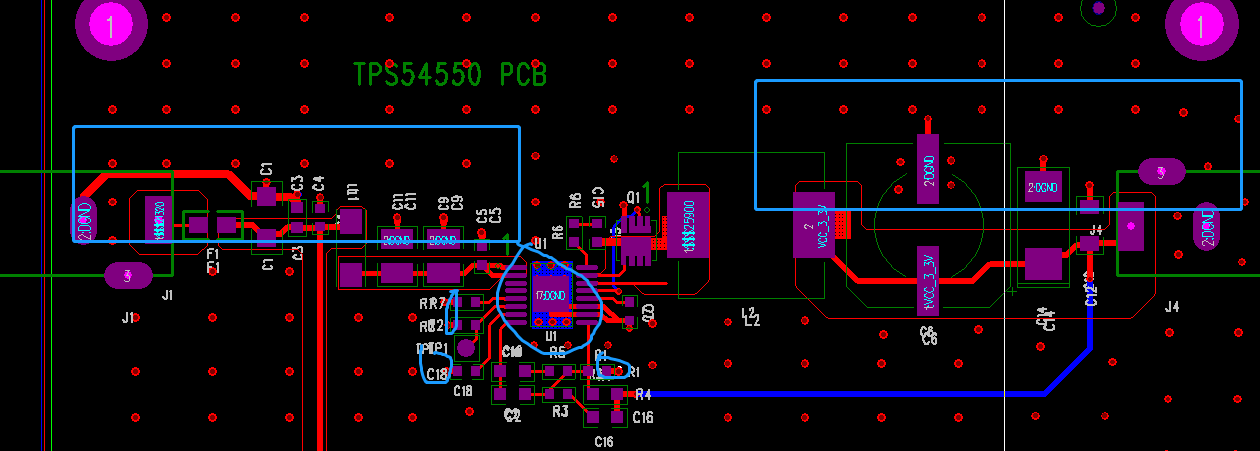

此芯片采用单点接地,就是输入输出和配置电路的地要连接在IC下方进行回流2.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊3.反馈线10mil即可4.主干道铺铜即可,不用多走一根线5.过孔里存在多余的线头以上评审报告来源于凡

Ansys OptICs/ 在这个联合方案中,将介绍一个仿真工作流程来分析单色AR(增强现实)系统的光学性能,用Zemax OptICStudio设计的光学透镜系统和用LumerICal设计光栅结构,到Speos进行系统级分析。 概览

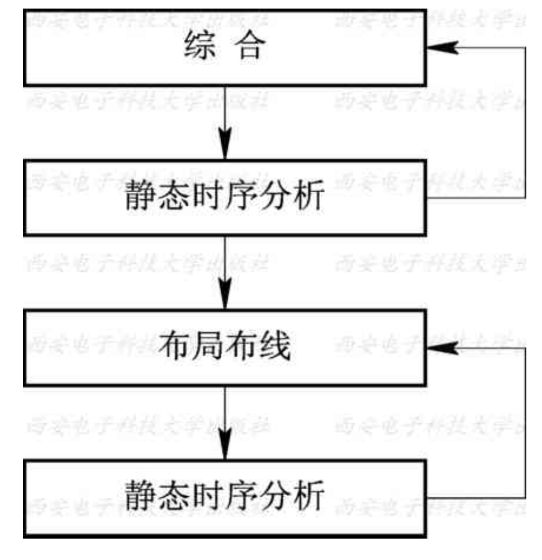

要想成为一个优秀的电子工程师,熟练掌握IC设计是基本技能之一,IC设计可分为多个环节,其中之一是静态时序分析,要想做好IC设计的静态时序分析,该如何做?首先,静态时序分析是检查IC系统时序是否满足要求的主要方法,静态时序分析工具根据往表中各

一个芯片的功耗过大,是会引发多种问题,如性能变差、温度升高降低芯片可靠性、极大限制便携式产品的使用时间及电池寿命,所以工程师要尽量降低芯片的功耗影响,尤其是高性能设计或便携式应用,那么如何降低IC设计的功耗问题?工程师对于高性能设计或便携式

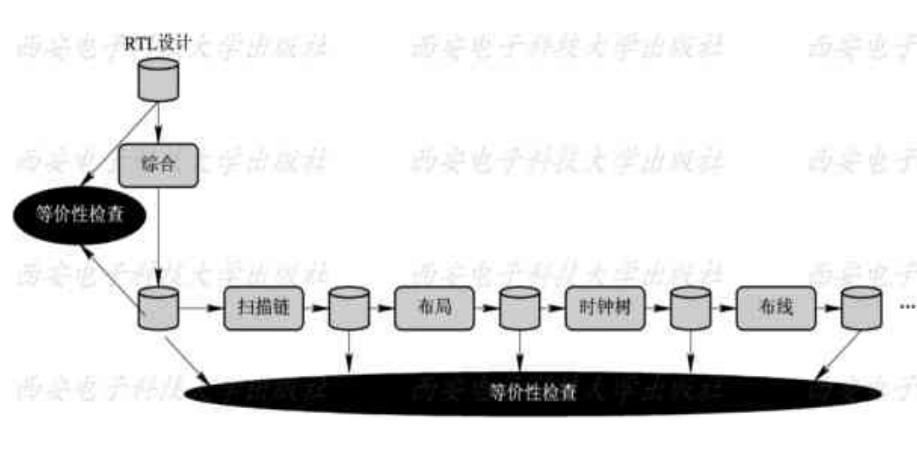

随着现代集成电路的密度及性能要求越来越高,导致现在的IC设计愈发艰难,仿真模拟无法更好测试验证IC系统功能,这时就要用上形式验证环节,但是很多人都没听说过形式验证,所以今天讲讲怎么做好形式验证。一般来说,用仿真方法来验证IC系统功能存在两个

以前信号完整性(SI)问题仅仅出现在高速电路板,但随着电子器件的特征尺寸越来越小元件的供电电压、噪声容限也开始下降,耦合电容增加,这些都导致了在IC系统中会出现信号完整性问题,那么该如何处理IC设计的信号完整性问题?一般来说,影响信号完整性

很多工程师在进行IC设计时都会选择FPGA来验证设计,而不是仿真模拟,这是因为与仿真相比,FPGA检查设计的效率高得多,当然大多数芯片开发中,都会选择FPGA原型机验证与RTL仿真结合起来。所以今天就聊聊基于FPGA的验证分析。在FPGA的

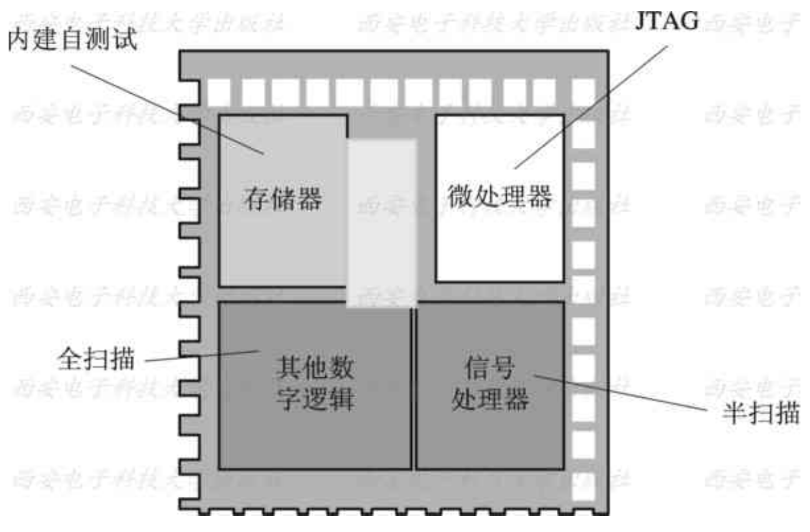

为保证产品的顺利上市,IC系统在设计过程中会进行很多测试,而电子工程师要尽量保证自己所设计的IC产品通过测试顺利上市,所以电子工程师必须了解IC系统的常用测试,今天我们来讲讲!一般来说,测试包括以下几方面的内容:1、功能测试和电气特性测试在

扫码关注

扫码关注