- 全部

- 默认排序

众所周知,芯片行业存在一个定理,那就是摩尔定律,主要内容是集成电路上可容纳的晶体管数目在大约每18个月便会增加一倍。掌握FPGA/IC工程师需要的核心技能,来凡亿教育!>>《基于VIVADO平台的FPGA时序约束教程》随着技术的提升和原材料

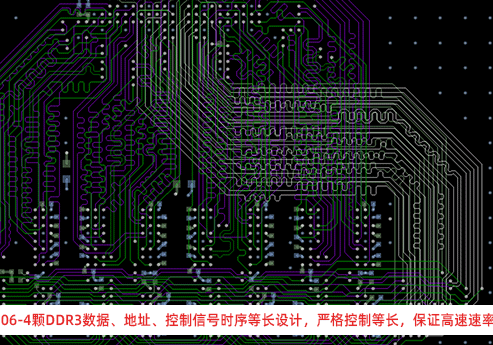

随着芯片内置晶体管数量越来越多,不到一年间隔研发从10nm、7nmnm到5nm,现如今已发展到一年半间隔研发3nm和2nm,可以说研发下一代工艺芯片所需时间越来越长。芯片的摩尔定律即将走到极限。掌握PCB精髓,来凡亿教育吧!>>《Alleg

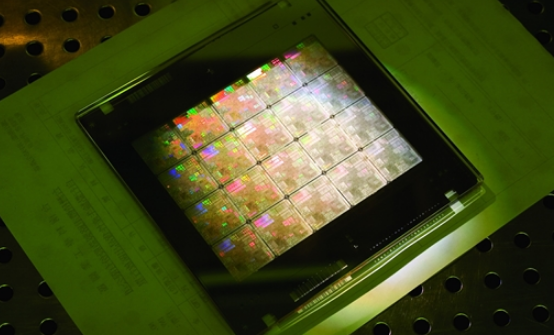

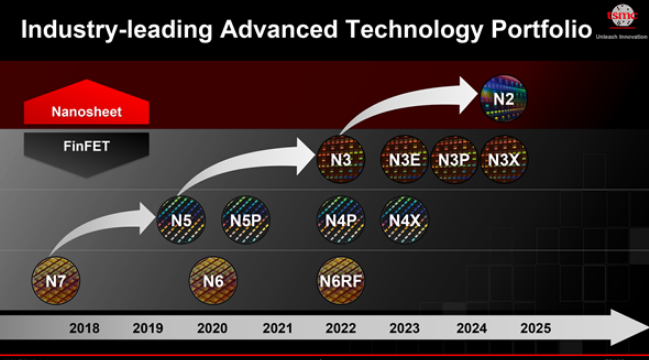

目前芯片制造的上游企业主要以台积电、三星、英特尔为主,以台积电为例,研发芯片的先进制程是4nm,今年下半年将投产3nm先进芯片。而我国大陆发展芯片制造起步较晚,在芯片制造、晶圆代工等方面稍弱,研发最先进的芯片工艺是14nm制程,在2020年

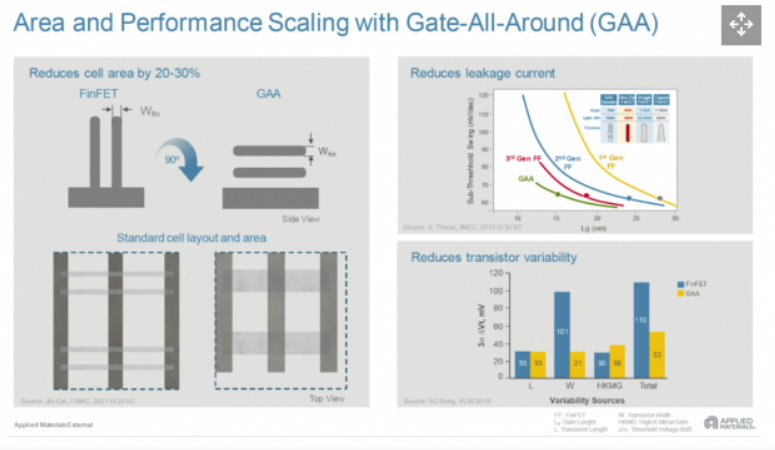

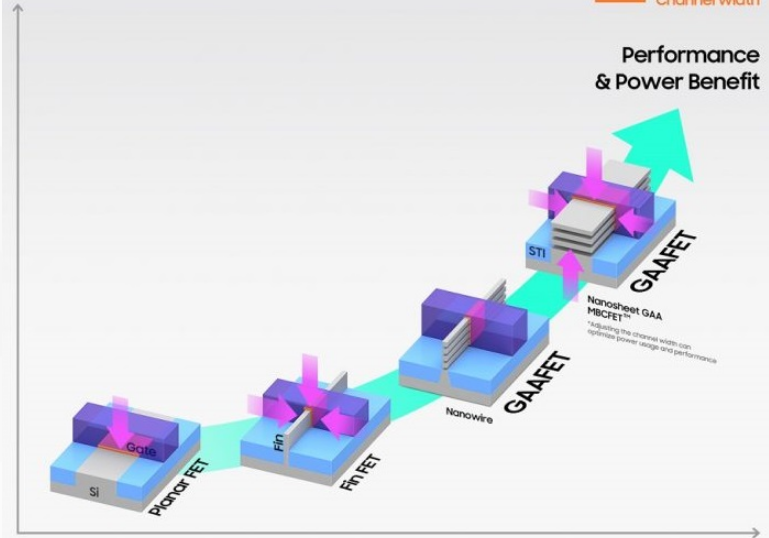

近日三星表示有望在本季度(即未来几周)开始使用3GAE(3nm级栅极全方位早期)制造工艺量产芯片,这意味着三星将首次量产3nm制造芯片,也是全球第一个使用GAAFET(栅极全包围场效应晶体管)的半导体厂商。零基础学习FPGA/ASIC来看看

作为全球半导体先进工艺的领导者,三星和台积电一直垄断着先进芯片领域,但由于近年来三星负责高通的骁龙处理器订单不顺,导致其骁龙产品口碑性能反响不佳,导致高通部分订单转向台积电。为保证先进工艺地位,近日三星宣布将用3nm工艺生产GAA环栅晶体管

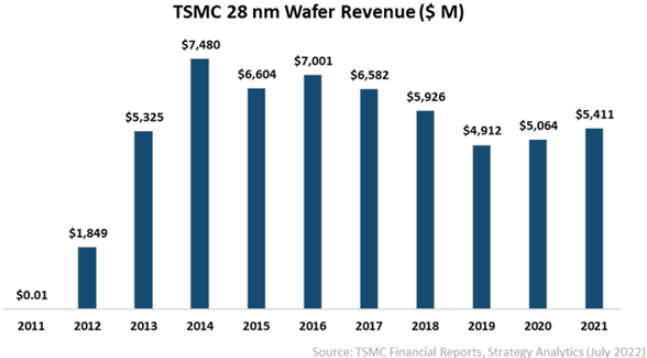

对于半导体工艺来说,大家都对先进工艺有一定的了解,不熟悉成熟制程,举个例子,手机厂商品牌主打招牌必定是采用先进工艺制程的芯片,如3nm、5nm、7nm,但先进工艺制程是在半导体芯片的顶端层面,对于整个半导体行业来说,基本上是以中下游产业为主

众所周知,全球能制作芯片先进工艺的半导体代工厂商只有台积电、三星,目前,在先进工艺上,台积电和三星量产或即将量产的7nm、5nm及3nm。而作为半导体强国的美国却在时间长河中逐渐被落后在台积电三星。为了实现在赛道上超过台积电和三星,美国计划

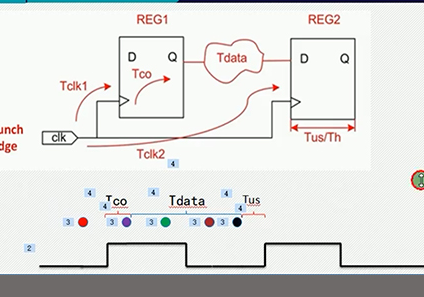

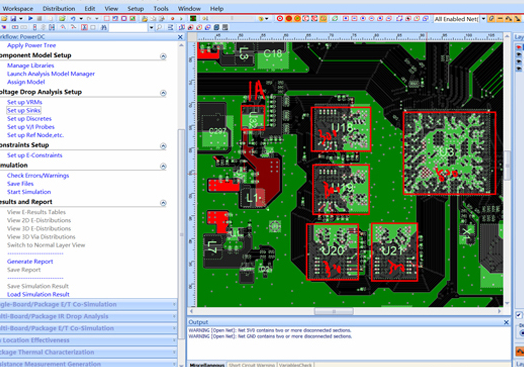

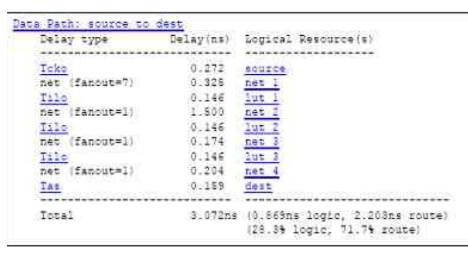

时序性能是FPGA设计最重要的技术指标之一,在项目设计中很多人经常会遇见时序性能差的现象,但不知道该如何解决。造成时序性能差的根本原因有很多1、布局太差如图所示:该图是布局太差的时序报告示意图,其中附加的周围约束为3nm,实际周期为3.02

随着微电子技术和信息技术的日益成熟,5G、大数据、人工智能等多项科技技术层出不穷,这必然要求高性能的芯片,这也促使了先进制程工艺的诞生。然而纵观全球,目前只有台积电和三星能够称霸芯片先进制程工艺,也是唯二能够生产3nm工艺芯片的半导体厂商,

众所周知,5nm以下的芯片先进制程,全球唯有台积电和三星能够进行,所以成为了多家大型品牌公司的选择。如高通、苹果、Intel等,这也造成台积电和三星旗鼓相当、平分秋色。但近年来随着三星良品率的降低,所生产的芯片散热不足,不如台积电更稳定,导

扫码关注

扫码关注