- 全部

- 默认排序

在进行PCB设计的时候,会用到差分,那么首先的第一步就是创建差分,创建完的第二步就是对于刚刚创建的差分进行规则的设置了。在PCB中差分规则是如何设置的呢?如果大家对于差分的创建还不熟悉的,可以去我们的PCB联盟网去搜索对应的技术文章去看看,加强自己的理解。在此就不再叙述了,我们主要讲解对于差分的规则设置。

在进行PCB设计的时候,会用到差分,那么首先的第一步就是创建差分,创建完的第二步就是对于刚刚创建的差分进行规则的设置了。在PCB中差分规则是如何设置的呢?其方法又有哪一些呢?

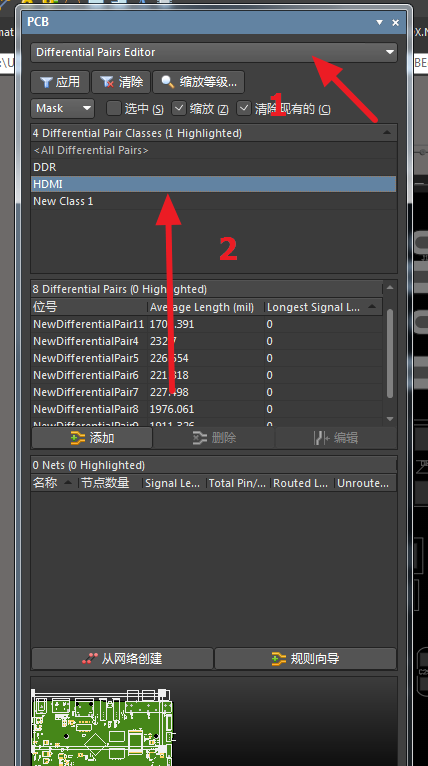

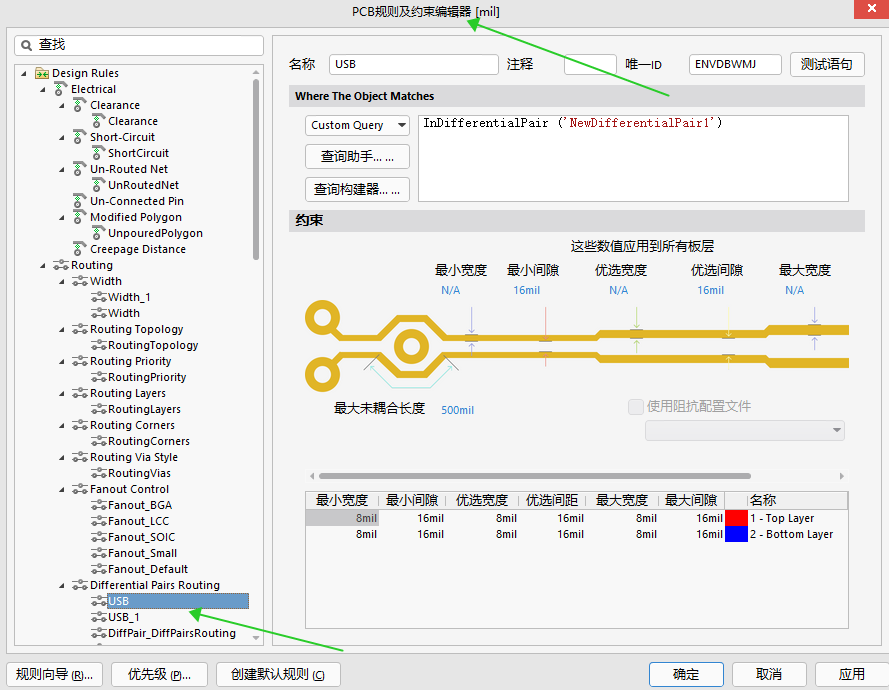

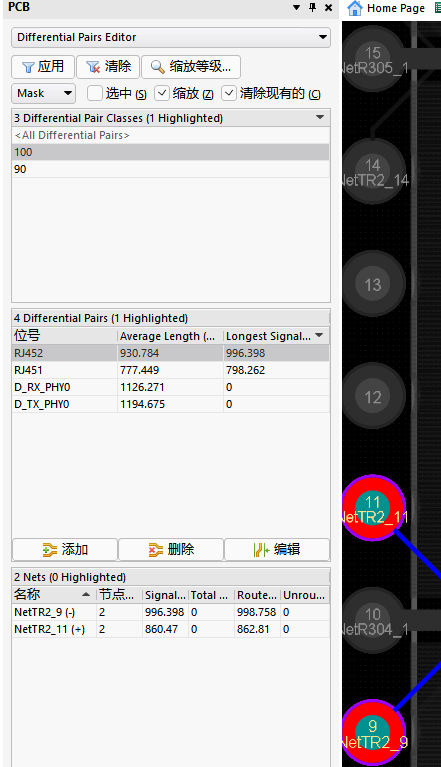

前文对差分类的添加进行了详细的讲述,不再进行赘述,这里对差分规则设置进行讲述。差分规则设置分为两种方法,一种为向导法,另一种为手工法。

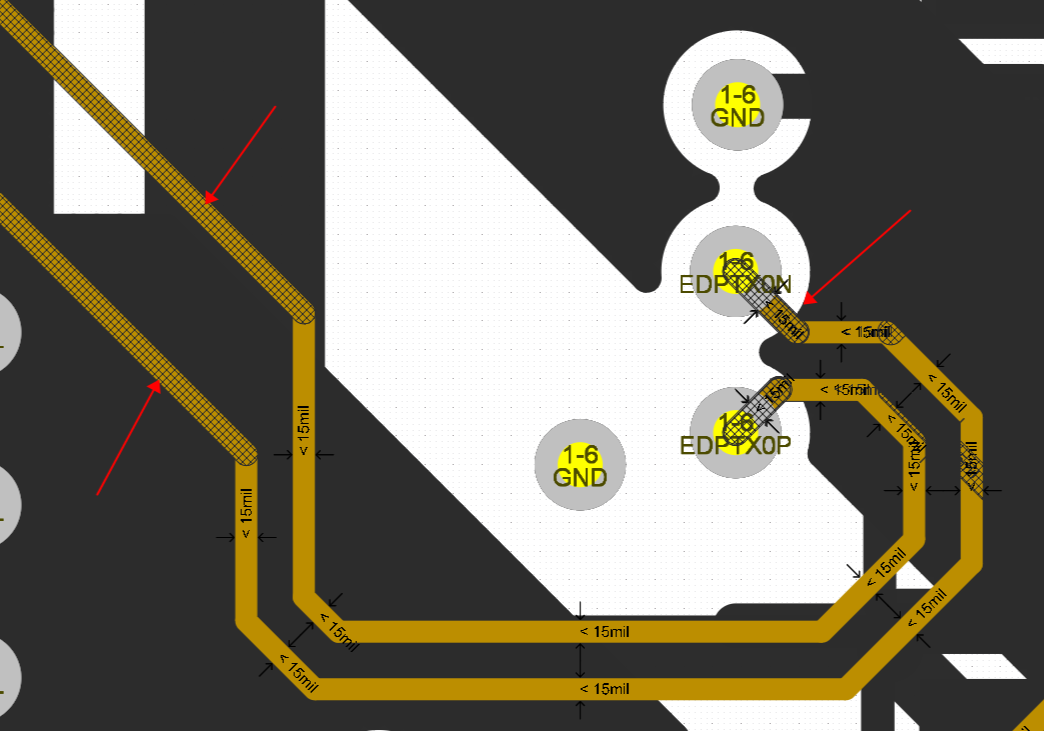

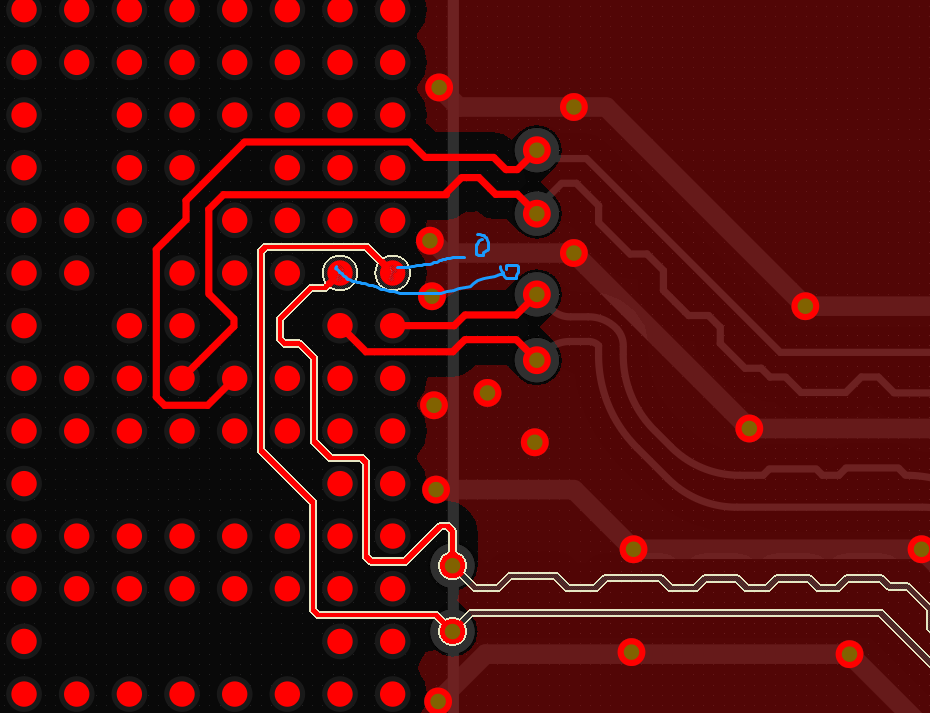

Altium Designer走差分线出现网格是什么原因?答:如图1所示,在AD软件中走差分线出现网格主要是差分线的未耦合长度没有满足差分规则所导致的,未耦合长度指的是差分线中不满足差分间距的长度。图 1 差分走线出现网格走线当出现这种错误

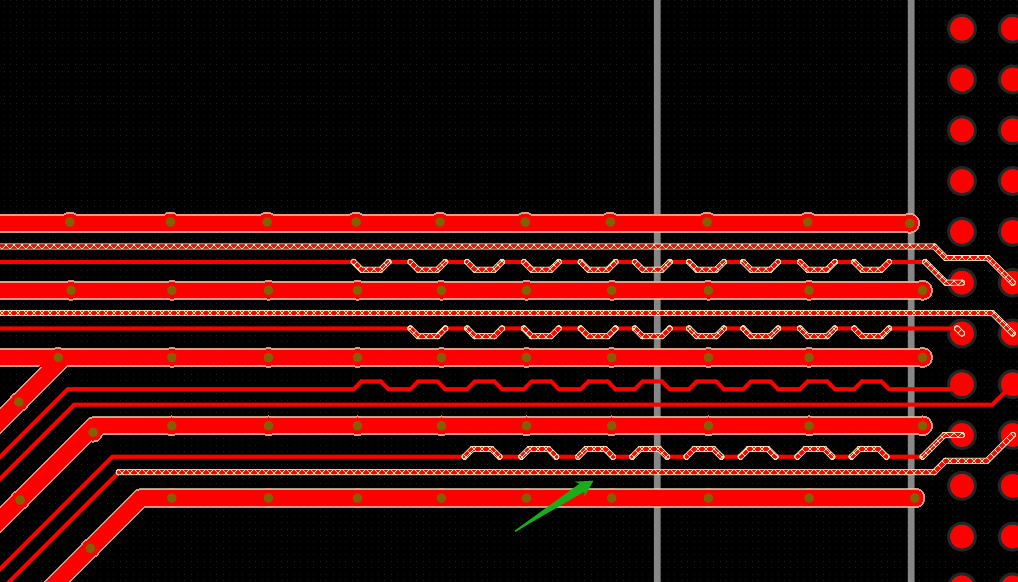

网口的差分信号需要对内等长,误差5mil2.差分出线要尽量耦合3.走线未连接到过孔中心4.RJ45座子需要挖空5.pcb上存在短路6.差分走线不满足差分规则7.锯齿状等长不能超过线距的两倍8.出线宽度超焊盘宽度,与焊盘同宽即可9.时钟包地需

差分走线不满足差分规则,出线不耦合2.此处直接扇孔去底层连接3.差分线修理不当4.此处一个地不用进行处理,直接铺铜即可此处走线需要优化一下以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系

焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊2.差分走线要尽量耦合出线3.此处走线不满足差分规则4.一个地不用进行分割差分 等长处理不当以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以

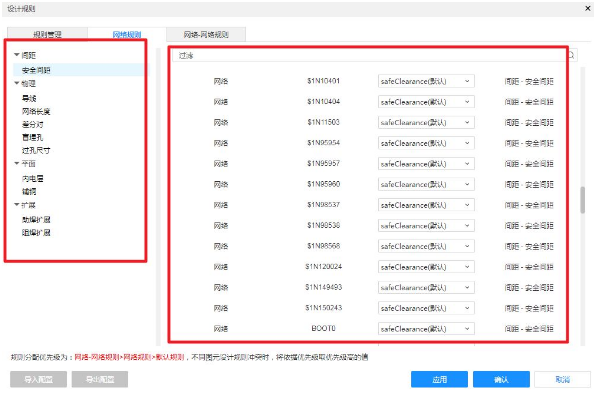

在“设计规则”中的“规则管理”界面将PCB的各个设计规则如线宽规则、差分规则、过孔规则等设置完成之后,就需要将PCB中每个网络所对应的规则进行驱动,那么就可以设置“网络规则”。在“网络规则”中可以对当前PCB内的所有网络进行规则分配,继而让

SATA:可以直接把差分规则里面的耦合度设置大一点就不会报错了:此处差分直接走顶层不用扇孔了:MIPI:注意差分组跟组等长误差为10MIL:此对差分对内等长误差是5MIL:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PC

扫码关注

扫码关注