概述

MAX V系列低成本和低功耗CPLD提供更大的密度和每占地面积的I/O。MAX V器件的密度从40到2210个逻辑元件(32到1700个等效宏单元)和多达271个I/O,为I/O扩展、总线和协议桥接、电源监控和控制、FPGA配置和模拟IC接口等应用提供可编程解决方案。

MAX V器件具有片上闪存、内部振荡器和内存功能。与其他CPLD相比,MAX V cpld的总功耗降低了50%,只需一个电源,可以帮助您满足低功耗设计要求。

技术参数

1、5M570ZT144C5N CPLD 440MC 9NS 144TQFP

可编程类型:系统内可编程

延迟时间 tpd(1) 最大值:9 ns

供电电压 - 内部:1.71V ~ 1.89V

逻辑元件/块数:570

宏单元数:440

I/O 数:114

工作温度:0°C ~ 85°C(TJ)

安装类型:表面贴装型

封装/外壳:144-TQFP(20x20)

基本产品编号:5M570Z

2、5M240ZT100C5N IC CPLD 192MC 7.5NS 100TQFP

可编程类型:系统内可编程

延迟时间 tpd(1) 最大值:7.5 ns

供电电压 - 内部:1.71V ~ 1.89V

逻辑元件/块数:240

宏单元数:192

I/O 数:79

工作温度:0°C ~ 85°C(TJ)

安装类型:表面贴装型

封装/外壳:100-TQFP(14x14)

基本产品编号:5M240Z

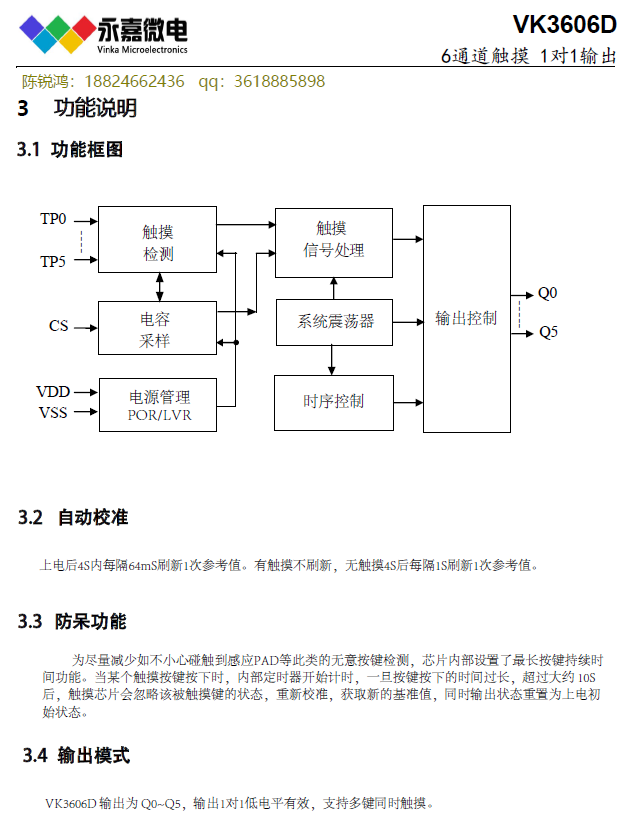

MAX V设备系列的特点:

低成本、低功耗、非易失性CPLD架构

即时启动(0.5 ms或更短)配置时间

待机电流低至25µA,快速下电/复位操作

快速传播延迟和时钟到输出时间

内部振荡器

模拟RSDS输出支持,数据速率高达200 Mbps

模拟LVDS输出支持,数据速率高达304 Mbps

四个全局时钟,每个逻辑阵列块(LAB)有两个时钟可用

用户闪存块最高可达8kbits,用于非易失性存储,最多可达1000个读写周期

单个1.8 v外置电源为设备核心供电

多伏I/O接口,支持3.3V、2.5V、1.8V、1.5V和1.2V逻辑电平

总线友好的架构,包括可编程转换速率,驱动强度,总线保持和可编程上拉电阻

Schmitt触发器支持噪声容忍输入(每个引脚可编程)

注:本文部分内容与图片来源于网络,版权归原作者所有。如有侵权,请联系删除!

扫码关注

扫码关注

![电子设计:IIR数字滤波器设计[学以致用系列课程之数字信号处理]](https://api.fanyedu.com/uploads/image/58/2fe737b3ff3f854913ef2c5df8df52.png)