- 全部

- 默认排序

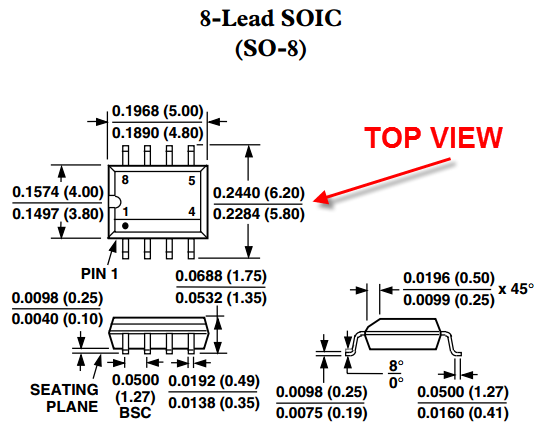

在LAYOUT中制作PCB封装时,在有很多管脚的情况,是怎么放置的。这个小视频操作讲解了在制作封装时有多个管脚的情况下,怎样的快捷放置焊盘方法。

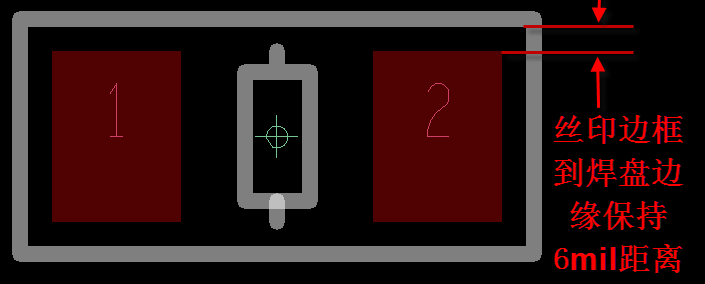

在PADS软件当中,制作封装时丝印边框无论是定义在走线层、丝印层、装配层,最后做出的板都是一样的,只要是2D线,就会自动识别为丝印,不必担心影响走线问题。

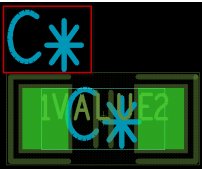

在制作封装时,建议使用的封装字体可如下示。如果字体的太小了,生产会有困难并且可能丝印印出来不方便识别,字体过大需要很大的PCB板空间放置,不利于设计。

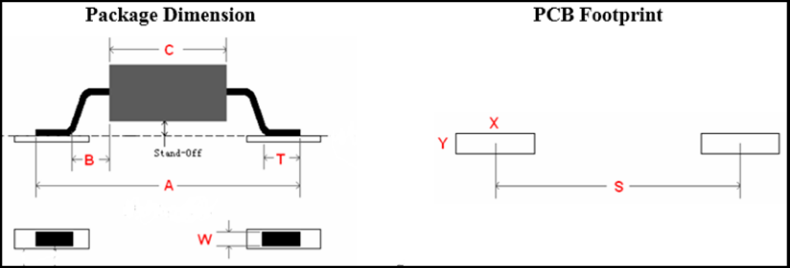

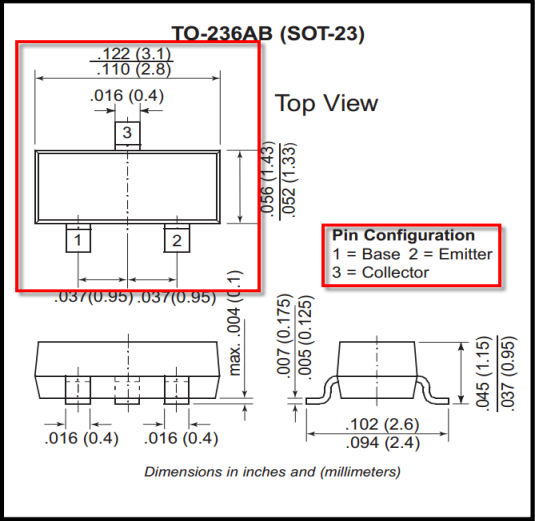

根据器件规格书(Datasheet)制作封装时,一般做出来的封装焊盘管脚长度需要做适当的补偿,即适量地对器件原先的管脚加长一点,具体的补偿方法,是根据器件的管脚类型来补偿的

扫码关注

扫码关注