在现代模拟集成电路设计中,CMOS差分放大器是一种应用广泛的子电路,也是小白学习放大器的重要内容之一,但有很多人学完该电路依然分不清电路图,所以本文将重点探讨CMOS差分放大器的特性应用及电路分析。

CMOS差分法前也叫作差放、差动放大器,是一种将两个输入端电压的差以一固定增益放大的电子放大器,是一种常用的电子防盗器和发射极耦合逻辑电路的输入级。差分放大器只对两个不同电压的差进行放大而不管其共模值;在CMOS差分放大器中,存在电压失调,其主要由MOS晶体管尺寸的不匹配性及工艺偏差等因素造成的。

如果将差分放大器的两个输入端连在一起,在输出端所测到的电压为输出失调电压,如果将这个电压除以放大器的差分电压增益,所得到的失调电压成为输入失调电压。

差分信号的作用:

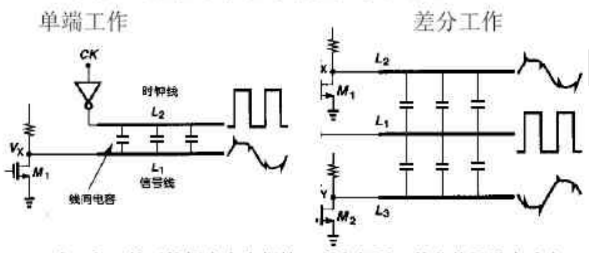

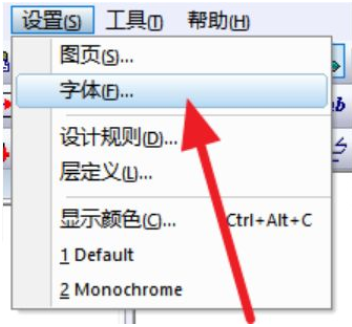

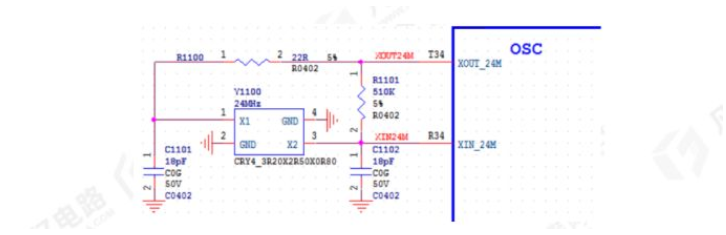

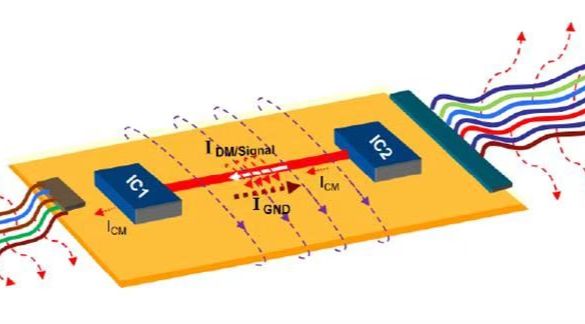

差动工作相当于单端工作的优点,对环境噪声具有更强的抗干扰能力。如图所示:

需要注意的是:L1对L2和L3的干扰幅度大小相等,方向想吐,差分信号没有改变。

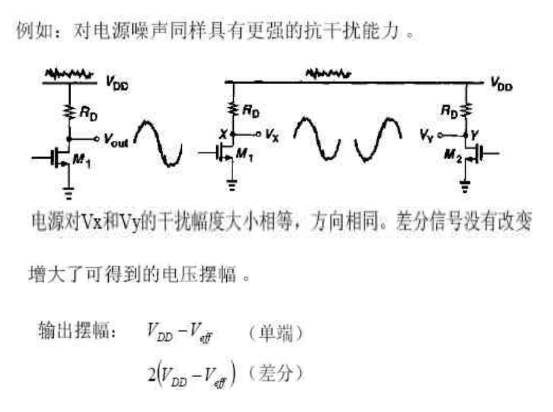

差分信号应用举例:

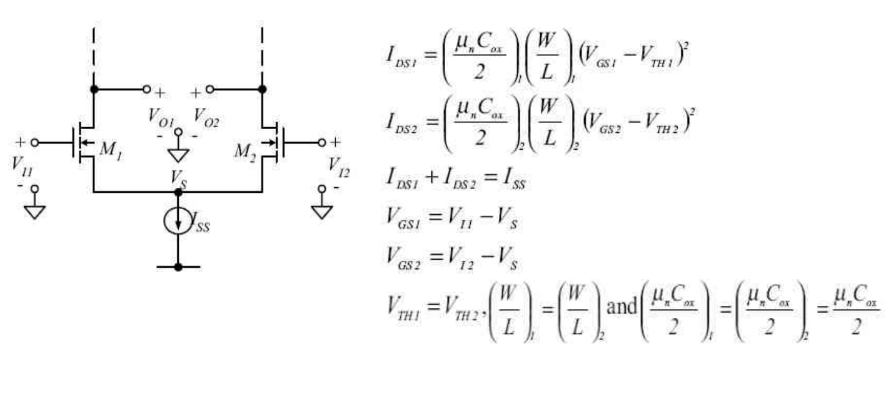

CMOS差分放大器对管的大信号特性:

CMOS差分放大器的小信号特性:

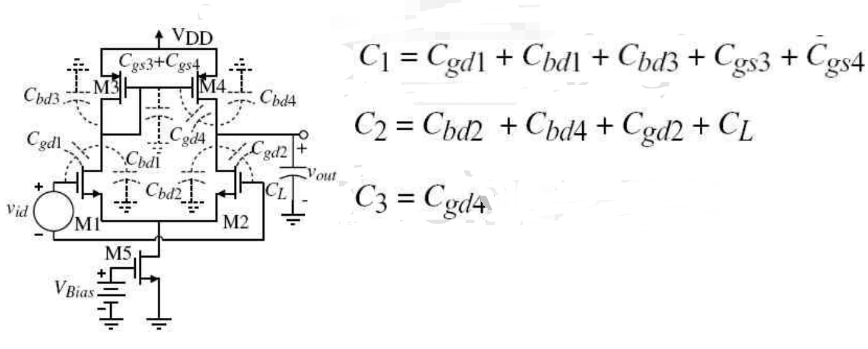

需要注意的是,CMOS差分放大器的频率响应主要由电路各节点的寄生电容所决定。图中的虚线电容为等效寄生电容,其中C1包括Cgd1、Cbd1、Cbd3、Cgs3和Cgs4,C2包括Cbd2、Cbd4、Cgd2和负载电容CL,C3只包括Cgd4。

扫码关注

扫码关注

![电子设计:ModelSim安装及破解[零基础学FPGA设计-理解硬件编程思想]](https://api.fanyedu.com/uploads/image/23/a075f4202af6900e9d6b9a42eac40c.png)