摘要

半导体技术的进步推动了相控阵天线在整个行业的普及。早在几年前,军事应用中已经开始出现从机械转向天线到有源电子扫描天线(AESA)的转变,但直到最近,才在卫星通信和5G通信中取得快速发展。小型AESA具有多项优势,包括能够快速转向、生成多种辐射模式、具备更高的可靠性;但是,在IC技术取得重大进展之前,这些天线都无法广泛使用。平面相控阵需要采用高度集成、低功耗、高效率的设备,以便用户将这些组件安装在天线阵列之后,同时将发热保持在可接受的水平。本文将简要描述相控阵芯片组的发展如何推动平面相控阵天线的实现,并采用示例辅助解释和说明。

简介

在过去几年里,我们在非常重视方向性的场合广泛使用抛物线碟形天线来发射和接收信号。其中许多系统表现出色,在经过多年优化之后保持了相对较低的成本。但这些机械转向碟形天线存在一些缺点。它们体积庞大,操作缓慢,长期可靠性较差,而且只能提供一种所需的辐射模式或数据流。

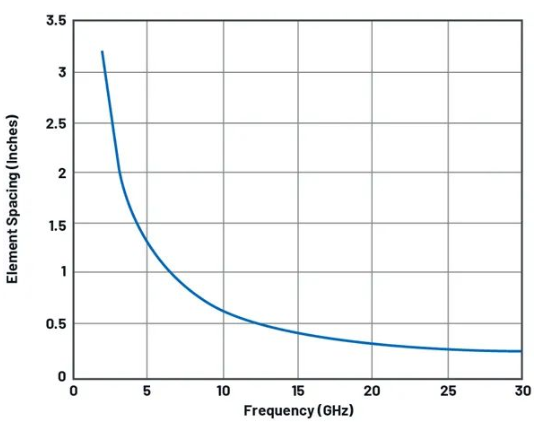

相控阵天线采用电信号转向机制,具有诸多优点,例如高度低,体积小、更好的长期可靠性、快速转向、多波束等。相控阵天线设计的一个关键方面是天线元件的间隔。大部分阵列都需要大约半个波长的元件间隔,因此在更高频率下需要更复杂的设计,由此推动IC在更高频率下,实现更高程度的集成,越加先进的封装解决方案。

人们对将相控阵天线技术应用于各种应用领域产生了浓厚的兴趣。但是,受限于目前可用的IC,工程师无法让相控阵天线成为现实。近期开发的IC芯片组成功解决了这一问题。半导体技术正朝着先进的硅IC方向发展,这让我们可以将数字控制、存储器和RF晶体管组合到同一个IC中。此外,氮化镓(GaN)显著提高了功率放大器的功率密度,可以帮助大幅减小占位面积。

相控阵技术

在行业向体积和重量更小的小型阵列转变期间,IC起到了重大的推动作用。传统的电路板结构基本使用小型PCB板,其上的电子元件垂直馈入天线PCB的背面。在过去的20年中,这种方法不断改进,以持续减小电路板的尺寸,从而减小天线的深度。下一代设计从这种板结构转向平板式方法,平板设计大大减小了天线的深度,使它们能更容易地装入便携应用或机载应用当中。要实现更小的尺寸,需要每个IC足够程度的集成,以便将它们装入天线背面。

在平面阵列设计中,天线背面可用于IC的空间受到天线元件间距的限制。举例来说,在高达60°的扫描角度下,要防止出现光栅波瓣,最大天线元件间隔需要达到0.54 λ。图1显示了最大元件间距(英寸)和频率的关系。随着频率提高,元件之间的间隔变得非常小,由此挤占了天线背后组件所需的空间。

图1.阻止在偏离瞄准线60°时产生光栅波瓣的天线元件间隔

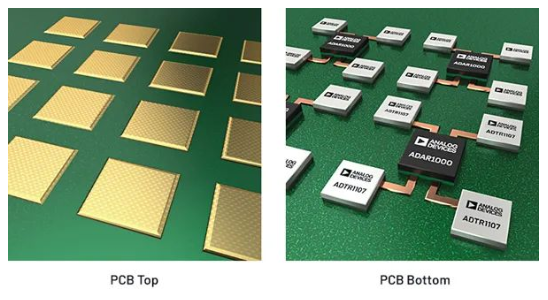

在图2中,左图展示了PCB顶部的金色贴片天线元件,右图显示了PCB底部的天线模拟前端。在这些设计中,在其他层上部署变频级和分配网络也是非常典型的。很明显可以看出,采用更多集成IC可以大幅降低在所需空间内部署天线设计的难度。在我们将更多电子元件封装到更小尺寸内,使得天线尺寸减小之后,我们需要采用新的半导体和封装技术,让解决方案变得可行。

图2.平面阵列,图中所示为PCB顶部的天线贴片,IC则位于天线PCB的背面

半导体技术和封装

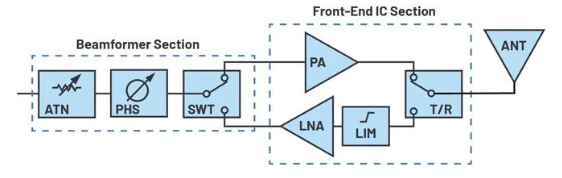

图3中显示了作为相控阵天线构建模块的微波和毫米波(mmW) IC组件。在波束成型部分,衰减器调整每个天线元件的功率电平,以减少天线方向图中的栅瓣。移相器调整每个天线元件的相位以引导天线主波束,并且使用开关在发射器和接收器路径之间切换。在前端IC部分,使用功率放大器来发射信号,使用低噪声放大器来接收信号,最后,使用另一个开关在发射器和接收器之间进行切换。在过去的配置中,每个IC都作为独立的封装器件提供。更先进的解决方案使用集成单芯片单通道砷化镓(GaAs) IC来实现这一功能。对于大部分阵列,在波束成型器之前都配有无源RF组合器网络、接收器/激励器和信号处理器,这一点图中未显示。

图3.相控阵天线的典型RF前端

相控阵天线技术近年来的普及离不开半导体技术发展的推动。SiGe BiCMOS、绝缘体上硅(SOI)和体CMOS中的高级节点将数字和RF电路合并到一起。这些IC可以执行阵列中的数字任务,以及控制RF信号路径,以实现所需的相位和幅度调整。如今,我们已经可以实现多通道波束成型IC,此类IC可在4通道配置中调整增益和相位,最多可支持32个通道,可用于毫米波设计。在一些低功耗示例中,基于硅的IC有可能为上述所有功能提供单芯片解决方案。在高功率应用中,基于氮化镓的功率放大器显著提高了功率密度,可以安装到相控阵天线的单元构件中。这些放大器传统上一般使用基于行波管(TWT)的技术或基于相对低功耗的GaAs的IC。

在机载应用中,我们看到了平板架构日益盛行的趋势,因为其同时具有GaN技术的功率附加效率(PAE)优势。GaN还使大型地基雷达能够从由TWT驱动的碟形天线转向由固态GaN IC驱动、基于相控阵的天线技术。我们目前能使用单芯片GaN IC,这类IC能提供超过100 W的功率,PAE超过50%。将这种效率水平与雷达应用的低占空比相结合,可以实现表贴解决方案,以散除外壳基座中产生的热量。这些表贴式功率放大器大大减小了天线阵列的尺寸、重量和成本。在GaN的纯功率能力以外,与现有GaAs IC解决方案相比的额外好处是尺寸减小了。举例来说,相比基于GaAs的放大器,X波段上6 W至8 W的基于GaN的功率放大器占位面积可减少50%或以上。在将这些电子器件装配到相控阵天线的单元构件中时,这种占位面积的减小有着显著的意义。

封装技术的发展也大大降低了平面天线架构的成本。高可靠性设计可能使用镀金气密外壳,芯片和线缆在其内部互连。这些外壳在极端环境下更坚固,但体积大,且成本高昂。多芯片模块(MCM)将多个MMIC器件和无源器件集成到成本相对较低的表贴封装中。MCM仍然允许混合使用半导体技术,以便最大化每个器件的性能,同时大幅节省空间。例如,前端IC中可能包含PA、LNA和T/R开关。封装基座中的热通孔或固体铜废料被用于散热。为了节省成本,许多商业、军事和航空航天应用都开始使用成本更低的表贴封装选项。

相控阵波束成型IC

集成式模拟波束成型IC一般被称为核心芯片,旨在为包括雷达、卫星通信和5G通信在内的广泛应用提供支持。这些芯片的主要功能是准确设置每个通道的相对增益和相位,以在天线主波束所需的方向增加信号。该波束成型IC专为模拟相控阵应用或混合阵列架构而开发,混合阵列架构将一些数字波束成型技术与模拟波束成型技术结合起来。

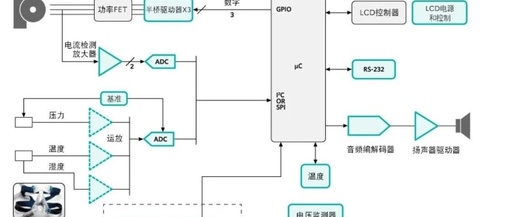

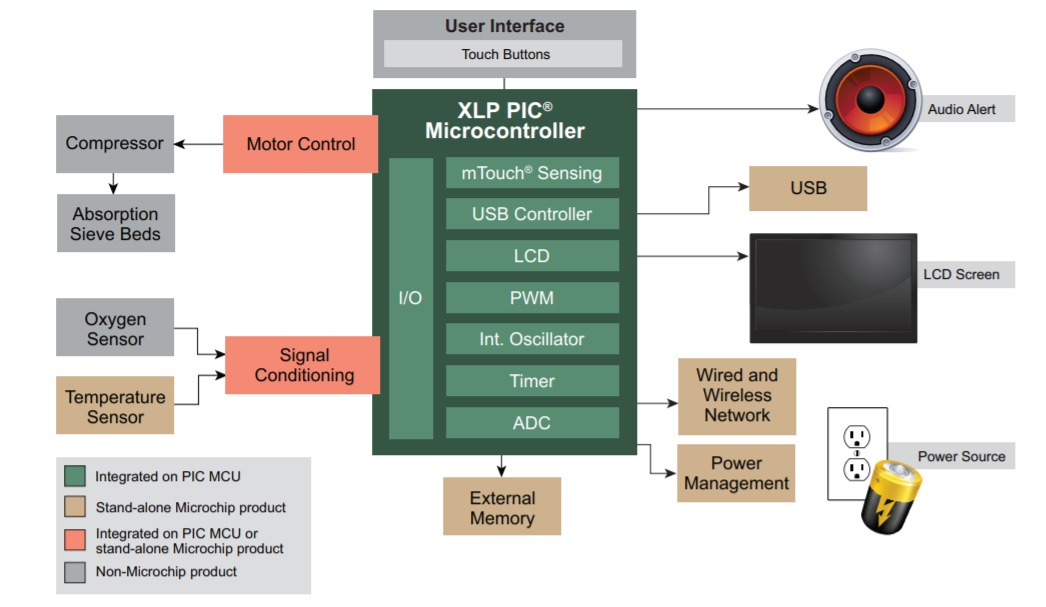

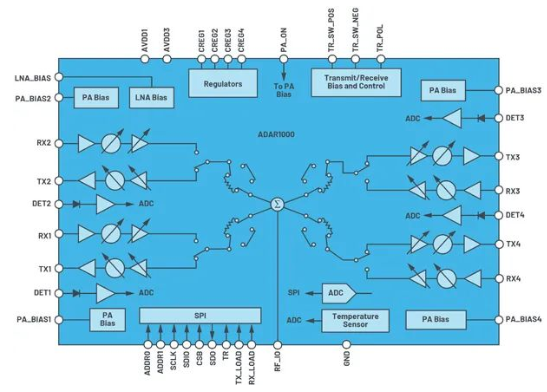

ADAR1000 X-/Ku波段波束成型IC是一款4通道器件,覆盖频段为8 GHz至16 GHz,采用时分双工(TDD)模式,其发射器和接收器集成在一个IC当中。在接收模式下,输入信号通过四个接收通道并组合在通用RF_IO引脚中。在发射模式下,RF_IO输入信号被分解并通过四个发射通道。功能框图如图4所示。

简单的4线式串行端口接口(SPI)可以控制所有片内寄存器。两个地址引脚可对同一串行线缆上的最多四个器件进行SPI控制。专用发射和接收引脚可同步同一阵列中的所有内核芯片,且单引脚可控制发射和接收模式之间的快速切换。这款4通道IC采用7 mm×7 mm QFN表贴封装,可轻松集成到平板阵列当中。高度集成,再加上小型封装,可以解决通道数量较多的相控阵架构中一些尺寸、重量和功率挑战。此器件在发射模式下功耗仅为240 mW/通道,在接收模式下功耗仅为160 mW/通道。

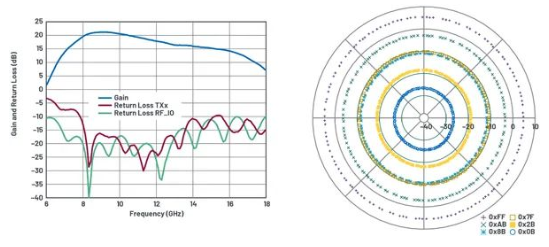

发射和接收通道直接可用,在外部设计上可以与前端IC配合使用。图5显示了器件的增益和相位图。具有全360°相位覆盖,可以实现小于2.8°的相位步长和优于30 dB的增益调整。ADAR1000集成片上存储器,可存储多达121个波束状态,其中一个状态包含整个IC的所有相位和增益设置。发射器提供大约19 dB的增益和15 dBm的饱和功率,其中接收增益约为14 dB。另一个关键指标是增益设置内的相位变化,在20 dB范围内约为3°。同样,在整个360°相位覆盖范围内,相位的增益变化约为0.25 dB,缓解了校准难题。

图4.ADAR1000功能框图

图5.ADAR1000发射增益/回波损耗和相位/增益控制,其中频率 = 11.5 GHz

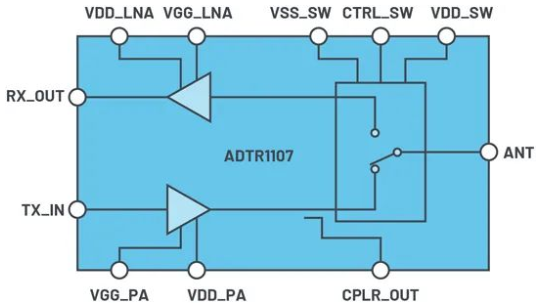

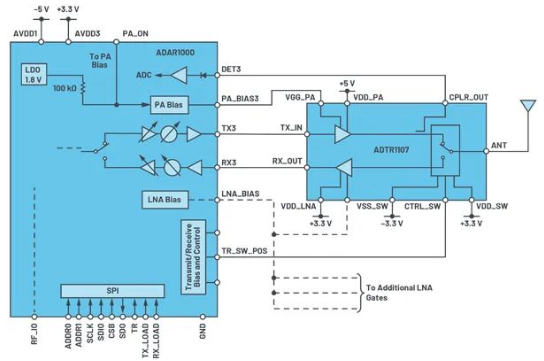

前端IC ADTR1107是ADAR1000波束成型芯片的补充。ADTR1107是一款紧凑型的6 GHz至18 GHz前端IC,包含集成式功率放大器、低噪声放大器(LNA),以及一个反射性的单刀双掷(SPDT)开关。功能框图如图6所示。

图6.ADTR1107功能框图

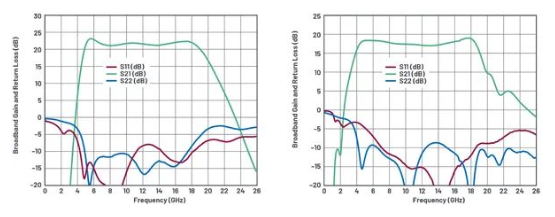

这款前端IC在发射状态下提供25 dBm饱和输出功率(PSAT)和22 dB小信号增益,在接收状态下提供18 dB小信号增益和2.5 dB噪声系数(包括T/R开关)。该器件配有双向耦合器,用于检测功率。输入/输出(I/O)内部匹配至50 Ω。ADTR1107采用5 mm × 5 mm、24引脚基板栅格阵列(LGA)封装。ADTR1107的发射和接收增益及回波损耗如图7所示。

图7.ADTR1107的发射增益/回波损耗和接收增益/回波损耗

ADTR1107专用于和ADAR1000轻松集成。接口原理图见图8。四个ADTR1107 IC由一个ADAR1000内核芯片驱动。出于简单考虑,图上只显示其中一个ADTR1107 IC的连接。

ADAR1000提供所需的所有栅级偏置和控制信号,使其与前端IC无缝连接。虽然ADTR1107 LNA栅级电压自偏置,我们也可以从ADAR1000控制电压。ADTR1107功率放大器的栅级电压也由ADAR1000提供。由于1个ADAR1000驱动4个ADTR1107,所以偏置功率放大器电压需要4个独立的负极栅级电压。每个电压都由一个8位数模转换器(DAC)设置。此电压可由ADAR1000 TR输入或串行外设接口写入置位。置位ADAR1000 TR引脚会在接收和发射模式之间切换ADAR1000的极性。TR_SW_POS引脚可以驱动多达4个开关的栅级,且可用于控制ADTR1107 SPDT开关。

ADTR1107 CPLR_OUT耦合器输出可以与4个ADAR1000 RF检波器输入(图4中的DET1至DET4)中的一个回连,以测量发射输出功率。这些基于二极管的RF检波器的输入范围为−20 dBm至+10 dBm。ADTR1107定向耦合器的耦合系数从6 GHz时的28 dB到18 GHz时的18 dB。

可以通过ADAR1000驱动的栅级电压实现ADTR1107脉冲,同时保持漏极恒定。相比通过漏极脉冲,这种方法更优化,因为这会用到高功率MOSFET开关和栅级驱动器器件与栅级开关,后者采用低电流。还应注意,在发射模式下ADAR1000提供足够功率会令ADTR1107饱和,在天线短路时ADTR1107可以承受总反射功率。

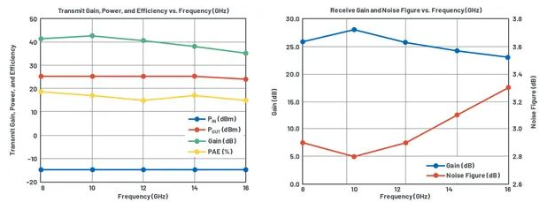

在发射和接收模式下,ADTR1107和ADAR1000在8 GHz至16 GHz频率范围内的组合性能如图9所示。在发射模式下,它们提供约40 dB增益和26 dBm饱和功率,在接收模式下,则提供约2.9 dB噪声系数和25 dB增益。

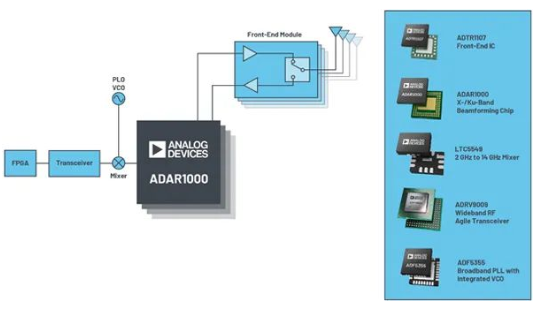

图10所示为4个ADAR1000芯片驱动16个ADTR1107芯片。简单的四线式SPI控制所有片内寄存器。两个地址引脚可对同一串行线缆上的最多四个ADAR1000芯片进行SPI控制。专用发射和接收负载引脚也可同步同一阵列中的所有内核芯片,且单引脚可控制发射和接收模式之间的快速切换。

图8.将ADTR1107前端IC与ADAR1000 X波段和Ku波段波束成型器连接

图9.与ADAR1000(单通道)耦合的ADTR1107的发射和接收性能

图10.4个ADAR1000芯片驱动16个ADTR1107芯片

图11

收发器芯片组和其他配套产品

高度集成的射频收发器芯片可以提升天线层面的集成。ADRV9009就是这种芯片一个很好的例子。它提供双发射器和接收器、集成式频率合成器和数字信号处理功能。该器件采用先进的直接转换接收器,具有高动态范围、宽带宽、错误校准和数字滤波功能。还集成了多种辅助功能,比如模数转换器(ADC)和数模转换器(DAC),以及用于功率放大器的通用输入/输出以及RF前端控制。高性能锁相环可同时针对发射器和接收器信号路径提供小数N分频RF频率合成。它提供极低功耗和全面的关断模式,以在不使用时进一步省电。ADRV9009采用12 mm × 12 mm、196引脚芯片级球栅阵列封装。

ADI公司为相控阵天线设计提供从天线到位的整个信号链,且针对此应用优化IC,以帮助客户加快上市时间。IC技术的进步促使天线技术发生转变,推动了多个行业的变革。

声明:本文转载自网络,如涉及作品内容、版权和其它问题,请于联系工作人员,我们将在第一时间和您对接删除处理!

扫码关注

扫码关注