对于FPGA工程师来说,RTL设计是常见的FPGA必不可少的设计环节,但对于小白来说,很多小白不懂RTL设计,甚至数次在FPGA或RTL设计常走歪路,所以本文将详谈RTL设计。

1、使用Verilog进行RTL设计

使用Verilog进行RTL设计一般可归纳为以下:

①数据流描述:采用assign连续赋值语句

②行为描述:使用always语句或initial语句块的过程赋值语句

③结构化描述:实例化已有的功能模块或原语,即元件例化和IP core。

其中,连续赋值语句是连续驱动的,也就是说只要输入变化,都会导致该语句的重新计算。其被赋值的变量不会被电路寄存。过程赋值语句包括非阻塞过程赋值、阻塞过程赋值和连续过程赋值。

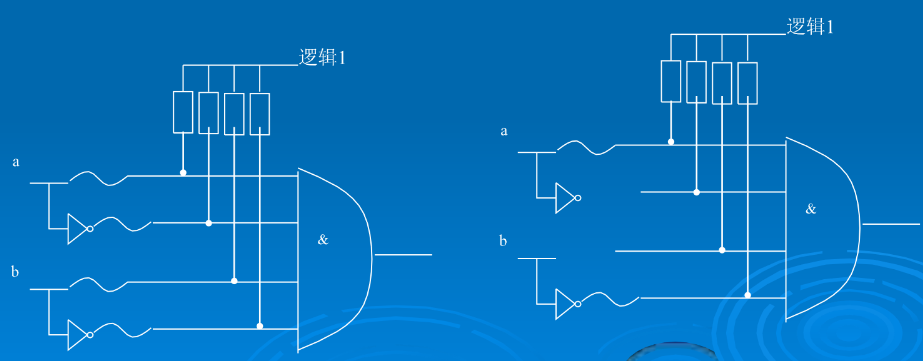

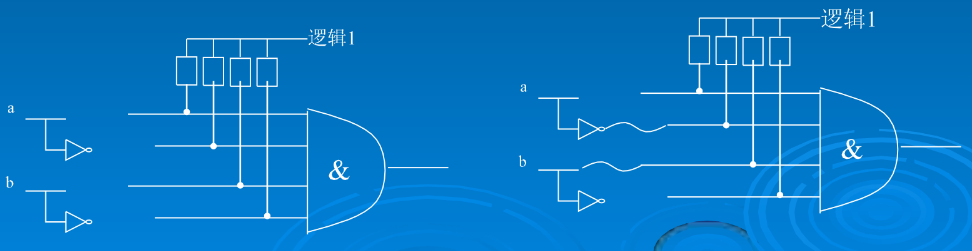

2、硬件设计意识

RTL设计其实就是用语言的方式去描述硬件电路行为的过程。这同一般的软件设计有很大区别,因为对于很多的软件代码,硬件电路是无法实现的(即无法综合,从语言到硬件电路的解析过程称为综合)。我们只能使用可综合的代码结构来实现我们所需的硬件电路。

首先,我们需要建立硬件设计的意识,硬件意识是RTL级设计的基础。

①电路在物理.上是并行工作的。其含义是,一旦接通电源,所有电路都同时工作。

②电路行为的先后顺序通过时钟节拍得顺序来体现。

3、RTL级设计时需注意的问题

①凡是在always或initial语句中赋值的变量,一定是reg类型变量;凡是在assign语句中赋值的变量,一定是wire类型变量。

②定义存储器:reg[3:0] MEMORY[0:7];地址为0-7,每个存储单元都是4bit;

③由于硬件是并行工作的,在Verilog语言的module中,所有描述语句(包括连续赋值语句assign、行为语句块always和initial语句块以及模块实例化)都是并发执行。

④使用完备的if....else语句,使用条件完备的case语句并设置default操作,以防止产生锁存器latch,因为锁存器对毛刺敏感。

⑤研究设计组合逻辑反馈环路,最易引起振荡、毛刺、时序违规等问题。

⑥不要在两个或两个以上的语句块(always或initial)中对同一个信号赋值。

扫码关注

扫码关注

![电子设计:数字逻辑电路基础知识回顾[零基础学FPGA设计-理解硬件编程思想]](https://api.fanyedu.com/uploads/image/d6/6631ce55ec5db0f7ae6624627d08cd.png)