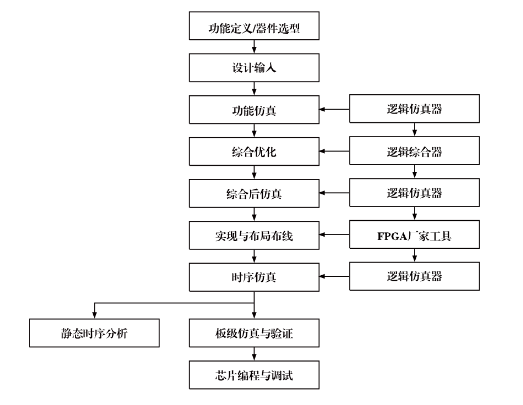

FPGA在逻辑芯片项目工程中是常见的,很多FPGA在项目中基本上都是以HDL代码来设计逻辑电路,但很多小白编写的HDL代码基本上都是不符合需求,费时费力,所以如何快速判断HDL代码是可行的?

任何符合HDL语法标准的代码都是对硬件行为的一种描述,但不一定是可直接对应成电路的设计信息。行为描述可以基于不同的层次,如系统级,算法级,寄存器传输级(RTL)、门级等等。以目前大部分EDA软件的综合能力来说,只有RTL或更低层次的行为描述才能保证是可综合的。绝大部分电路设计必须遵循RTL的模式来编写代码,而不能随心所欲得写仅仅符合语法的HDL代码。

一般来说,以下HDL代码是不可综合的:

①大部分抽象的行为描述代码是不可综合的。

②大部分抽象的运算代码也是不可综合的。

③不定次数的循环运算代码是不可综合的。

如何判断自己写的HDL代码是可综合的?

通常EDA软件对HDL代码的综合能力总是比人的思维差。也就是说,对于一-段代码,如果你不能想象出一个较直观的硬件实现方法,那EDA软件肯定也不行。比如说,加法器、多路选择器是大家都很熟悉的电路,所以类似A+B-C, (A>B)?C:D 这样的运算一定可以综合。而除法、开根、对数等等较复杂的运算,必须通过一.定的算法实现,没有直观简单的实现方法,则可以判断那些计算式是不能综合的,必须按它们的算法写出更具体的代码才能实现。此外,硬件无法支持的抽象行为描述,当然也不能被综合。

不过,这样的判断标准非常主观模糊,遇到具体情况还得按设计人员自己的经验来判断。如果要一个相对客观的标准,一般来说:在RTL级的描述中,所有逻辑运算和加减法运算、以及他们的有限次组合,基本上是可综合的,否则就有无法综合的可能性。当然,这样的标准仍然有缺陷,所以,正确的判断仍然要靠实践来积累经验。当你可以较准确判断代码的可综合性的时候,你对HDL的掌握就算完全入门了。

扫码关注

扫码关注