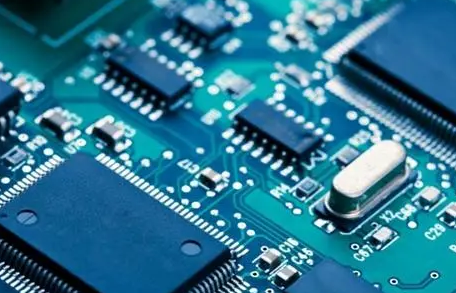

在IC设计过程中,很多电子工程师都会接触到一个新名词,也就是寄生效应,但有很多小白可能不太清楚寄生效应的概念及作用,今天我们来谈谈IC设计中的寄生效应是什么?如何避免?

所谓寄生效应就是那些溜进你的PCB并在电路中大施破坏、令人头痛、原因不明的小故障。它们就是渗入高速电路中隐藏的寄生电容和寄生电感。其中包括由封装引脚和印制线过长形成的寄生电感;焊盘到地、焊盘到电源平面和焊盘到印制线之间形成的寄生电容;通孔之间的相互影响,以及许多其它可能的寄生效应。

理想状态下,导线是没有电阻,电容和电感的。而在实际中,导线用到了金属铜,它有一定的电阻率,如果导线足够长,积累的电阻也相当可观。两条平行的导线,如果互相之间有电压差异,就相当于形成了一个平行板电容器(你想象一下)。通电的导线周围会形成磁场(特别是电流变化时),磁场会产生感生电场,会对电子的移动产生影响,可以说每条实际的导线包括元器件的管脚都会产生感生电动势,这也就是寄生电感。

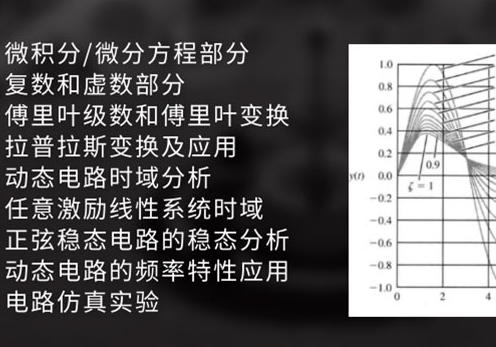

在直流或者低频情况下,这种寄生效应看不太出来。而在交流特别是高频交流条件下,影响就非常巨大了。根据复阻抗公式,电容、电感会在交流情况下会对电流的移动产生巨大阻碍,也就可以折算成阻抗。这种寄生效应很难克服,也难摸到。只能通过优化线路,尽量使用管脚短的SMT元器件来减少其影响,要完全消除是不可能的。

扫码关注

扫码关注

![电子设计:频域采样定理及FFT算法[学以致用系列课程之数字信号处理]](https://api.fanyedu.com/uploads/image/5e/e20549b95077812a27c92ed71009cb.png)