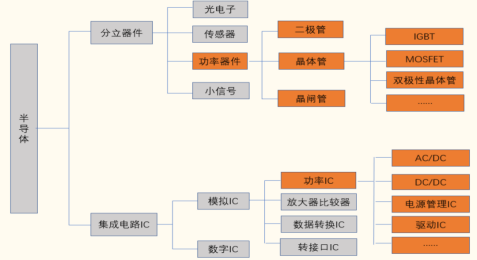

由于开关电源的开关特性,容易使得开关电源产生极大的电磁兼容方面的干扰,作为一个电源工程师、电磁兼容工程师,或则一个 PCB layout 工程师必须了解电磁兼容问题的原因已经解决措施。特别是 layout 工程师,需要了解如何避免脏点的扩大。本文主要介绍了电源 PCB 设计的要点。

layout与PCB的29个基本关系

1、几个基本原理:任何导线都是有阻抗的;电流总是自动选择阻抗最小的路径;辐射强度和电流、频率、回路面积有关;共模干扰和大 dv/dt 信号对地互容有关;降低 EMI 和增强抗干扰能力的原理是相似的。

2、布局要按电源、模拟、高速数字及各功能块进行分区。

3、尽量减小大 di/dt 回路面积,减小大 dv/dt 信号线长度(或面积,宽度也不宜太宽,走线面积增大使分布电容增大,一般的做法是:走线的宽度尽量大,但要去掉多余的部分),并尽量走直线,降低其隐含包围区域,以减小辐射。

4、感性串扰主要由大 di/dt 环路(环形天线),感应强度和互感成正比,所以减小和这些信号的互感(主要途径是减小环路面积、增大距离)比较关键;容性串扰主要由大 dv/dt 信号产生,感应强度和互容成正比,所有减小和这些信号的互容(主要途径是减小耦合有效面积、增大距离,互容随距离的增大降低较快)比较关键。

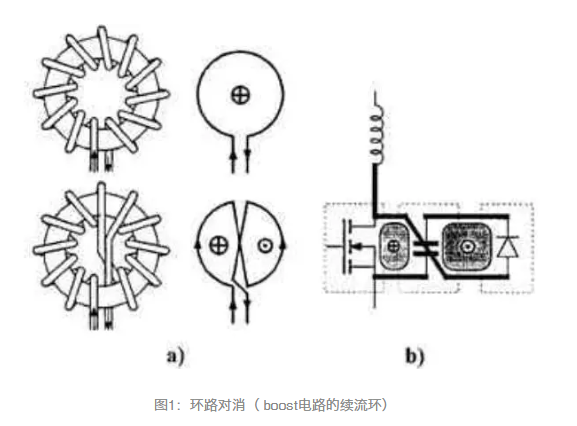

5、尽量利用环路对消的原则来布线,进一步降低大 di/dt 回路的面积,如图 1 所示(类似双绞线利用环路对消原理提高抗干扰能力,增大传输距离):

图1:环路对消( boost电路的续流环)

6、降低环路面积不仅降低了辐射,同时还降低了环路电感,使电路性能更佳。

7、降低环路面积要求我们精确设计各走线的回流路径。

8、当多个 PCB 通过接插件进行连接时,也需要考虑使环路面积达到最小,尤其是大 di/dt 信号、高频信号或敏感信号。最好一个信号线对应一条地线,两条线尽量靠近,必要时可以用双绞线进行连接(双绞线每一圈的长度对应于噪声半波长的整数倍)。如果大家打开电脑机箱,就可以看到主板到前面板 USB 接口就是用双绞线进行连接,可见双绞线连接对于抗干扰和降低辐射的重要性。

9、对于数据排线,尽量在排线中多安排一些地线,并使这些地线均匀分布在排线中,这样可以有效降低环路面积。

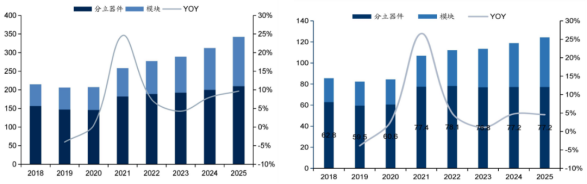

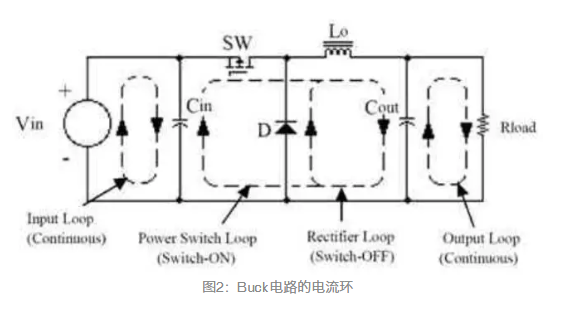

10、有些板间连接线虽然是低频信号,但由于这些低频信号中含有大量的高频噪声(通过传导和辐射),如果没有处理好,也很容易将这些噪声辐射出去。

11、布线时首先考虑大电流走线和容易产生辐射的走线。

12、开关电源通常有 4 个电流环:输入、输出、开关、续流,(如图 2 )。其中输入、输出两个电流环几乎为直流,几乎不产生 emi ,但容易受干扰;开关、续流两个电流环有较大的 di/dt ,需要注意。

13、mos ( igbt )管的栅极驱动电路通常也含有较大的 di/dt 。

14、在大电流、高频高压回路内部不要放置小信号回路,如控制、模拟电路,以避免受到干扰。

15、减小易受干扰(敏感)信号回路面积和走线长度,以减小干扰。

16、小信号走线远离大 dv/dt 信号线(比如开关管的 C 极或 D 极,缓冲 (snubber) 和钳位网络),以降低耦合,可在中间铺地(或电源,总之是常电位信号)进一步降低耦合,铺地和地平面要良好接触。小信号走线同时也要尽量远离大 di/dt 的信号线,防止感性串扰。小信号走线最好不要走到大 dv/dt 信号的下方。小信号走线背面如果能够铺地(同性质地),也能降低耦合到的噪声信号。

17、比较好的做法是,在这些大 dv/dt 、 di/dt 信号走线(包括开关器件的 C/D 极、开关管散热器)的周围和背面铺地,将上下两层铺地用过孔连接,并将此地用低阻抗走线接到公共接地点(通常为开关管的 E/S 极,或取样电阻)。这样可以减小辐射 EMI 。要注意,小信号地一定不能接到此屏蔽地上,否则会引入较大干扰。大 dv/dt 走线通常会通过互容将干扰耦合到散热器及附近的地,最好将开关管散热器接到屏蔽地上,采用表贴开关器件也会降低互容,从而降低耦合。

18、易产生干扰的走线最好不要使用过孔,它会通过过孔干扰过孔所穿过的所有层。

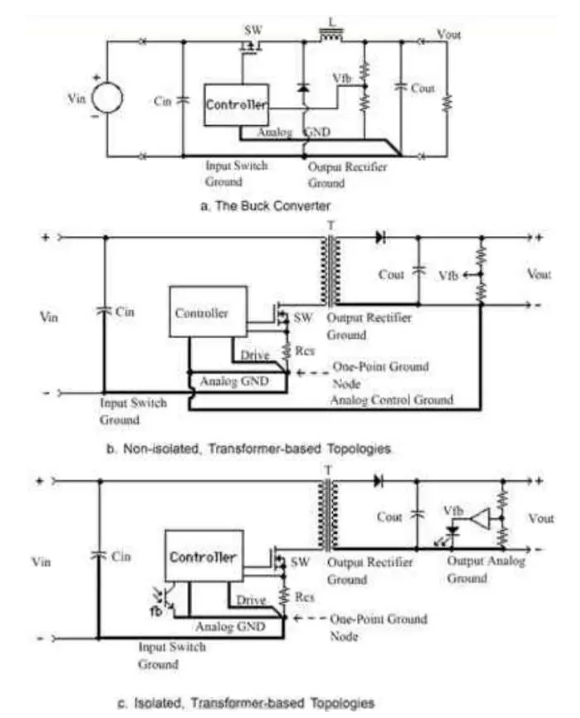

19、屏蔽可以降低辐射 EMI ,但由于增大了对地的电容,会使传导 EMI (共模,或非本征差模)有所增大,不过只要屏蔽层接地得当,不会增大很多。实际设计中可权衡考虑。

20、要防止共阻抗干扰,采用一点接地,电源从一点引出。

21、开关电源通常有三种地:输入电源大电流地、输出电源大电流地、小信号控制地,地的连接方法见如下示意图:

22、接地时首先应先判断地的性质,再进行连接。采样及误差放大的地通常应当接到输出电容的负极,采样信号通常应从输出电容的正极取出,小信号控制地和驱动地通常要分别接到开关管的 E/S 极或取样电阻上,防止共阻抗干扰。通常 IC 的控制地和驱动地不单独引出,此时取样电阻到上述地的引线阻抗必须尽量小,最大程度减小共阻抗干扰,提高电流采样的精度。

23、输出电压采样网络最好靠近误差放大器,而不是靠近输出端,这是由于低阻抗信号比高阻抗信号更不容易受到干扰,采样走线对要尽量相互靠近以减小拾取到的噪声。

24、布局注意电感要远离,并相互垂直,以减小互感,尤其是储能电感和滤波电感。

25、布局注意高频电容和低频电容并联使用时,高频电容靠近使用者。

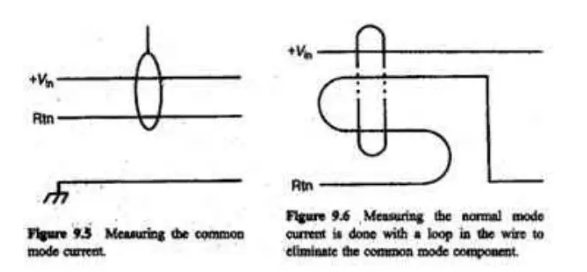

26、低频干扰一般为差模( 1M 以下),高频干扰一般为共模,通常通过辐射耦合。

27、如果高频信号被耦合到输入引线,很容易形成 EMI (共模),可在输入引线接近电源处套一个磁环,如果 EMI 降低就表明存在此问题。解决此问题的方法是,降低耦合或降低电路的 EMI 。如果高频噪声没有被过滤干净而传导到输入引线,也会形成 EMI (差模),此时套磁环不能解决问题,在输入引线接近电源处串两个高频电感(对称),如果 EMI 降低就表明存在此问题。解决此问题的方法是改善滤波,或采用缓冲、钳位等手段减小高频噪声的产生。

28、差模和共模电流的测量:

29、EMI 滤波器要尽量靠近进线,进线的走线要尽量短,尽量减小 EMI 滤波器前后级的耦合。进线最好用机壳地进行屏蔽(方法如上所述)。输出 EMI 滤波器也要作类似处理。尽量拉开进线和高 dv/dt 信号走线的距离,在布局上要加以考虑。

声明:

本文转载自网络 ,如涉及作品内容、版权和其它问题,请于联系工作人员,我们将在第一时间和您对接删除处理!

扫码关注

扫码关注